(54) АДАПТИВНЫЙ КОММУТАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ КОММУТАТОР СИСТЕМЫ ТЕЛЕИЗМЕРЕНИЙ | 1967 |

|

SU225036A1 |

| АДАПТИВНЫЙ КОММУТАТОР СИСТЕМЫ ТЕЛ ЕИЗМЕРЕН ИИ | 1973 |

|

SU407376A1 |

| Коммутатор каналов для телеметрической системы | 1979 |

|

SU855714A1 |

| Адаптивный коммутатор системы телеизмерений | 1980 |

|

SU886032A1 |

| Адаптивный коммутатор системыТЕлЕизМЕРЕНий | 1979 |

|

SU809295A1 |

| Адаптивный коммутатор телеизмерительной системы | 1980 |

|

SU877597A1 |

| Адаптивный коммутатор системы телеизмерений | 1976 |

|

SU590799A1 |

| Устройство для обучения чтению | 1989 |

|

SU1665401A1 |

| Адаптивный статистический анализатор | 1980 |

|

SU955090A1 |

| Устройство для передачи телеметрической информации | 1982 |

|

SU1030830A1 |

Изобретение относится к радиотехнике и может использоваться в цифровых телеметрических системах с адресным разделением каналов.

Известен адаптивный коммутатор, содержащий узел выбора каналов, последовательно соединенные блок статической памяти адресов, блок динамической памяти а.цресов и ;аиодную матрицу, выходы которой соединены с управляющими входами ключей, причем входы блока статической памяти соединены с соответствующими выходами узла выбора каналов 1.

Однако пропускная способность известного адаптивного коммутатора мала.

Цель изобретения - повышение пропускной способности.

Указанная цель достигается тем, что в известный адаптивный коммутатор введены п цепей из последовательно соединенных дельта-модулятора, блока преобразования импульсной последовательности и анализатора импульсной последовательности (где п - число каналов), причем входы дельта-модуляторов соединены с информационными входами ключей, а выхохсы анализаторов импулпсной последовательности соединены с соответствующими входами узла выбора каналов.

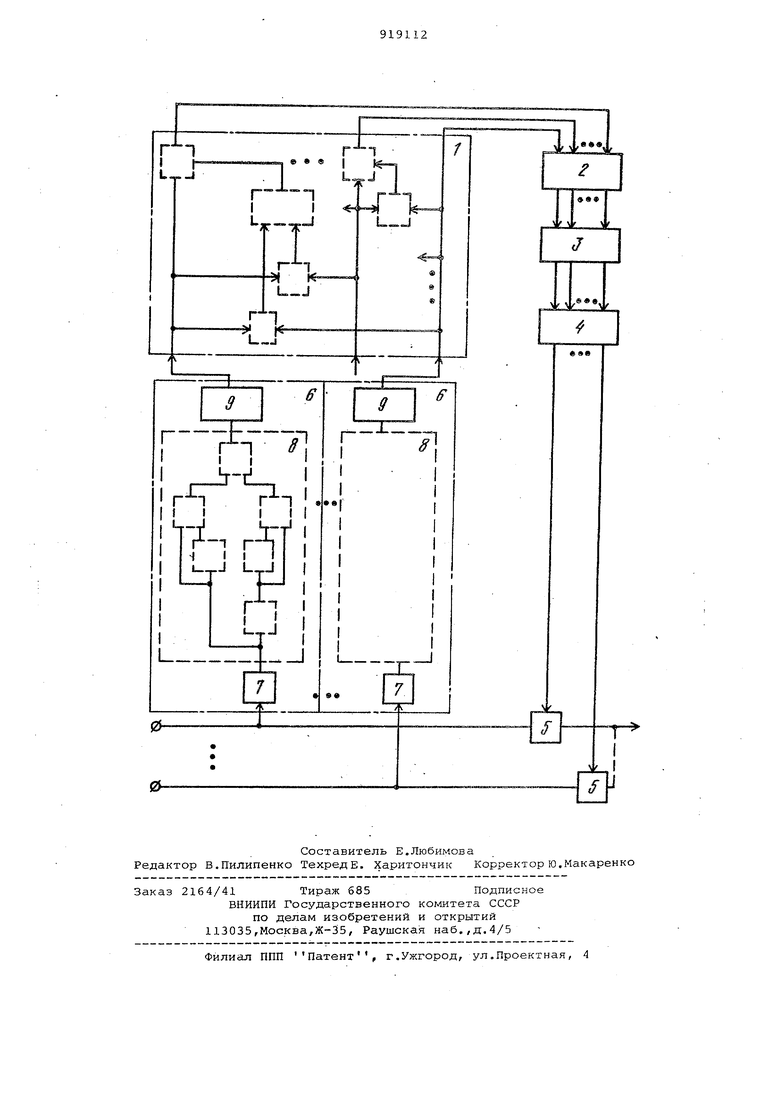

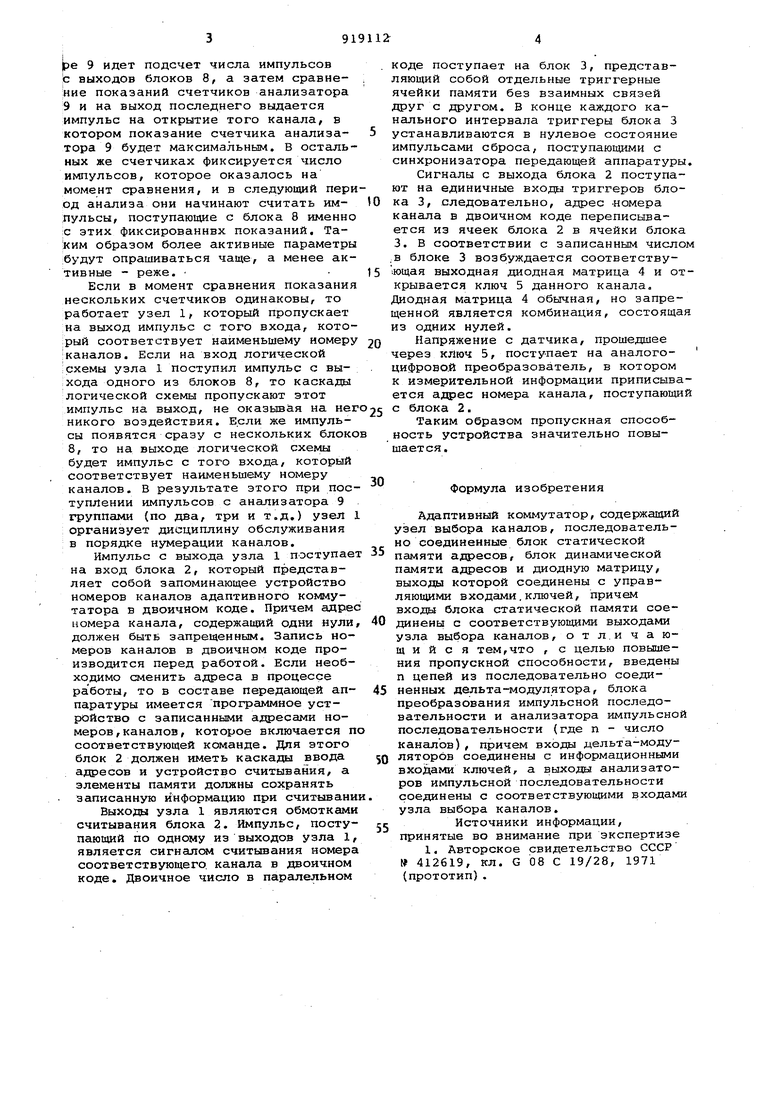

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Адаптивный коммутатор содержит узел 1 выбора каналов, блок 2 статической памяти а.дресов, блок 3 динамической памяти а.цресов, диод10ную матрицу 4, ключи 5 и п цепей 6, содержащих каждая дельта-модулятор 7, блок 8 преобразования импульсной последовательности и анализатор 9 импульсной последовательности.

15

Устройство работает следующим образом.

Напряжения с датчиков информации поступают на соответствующие входы адаптивного коммутатора. Эти напря20жения преобразуются дельта-модуляторами 7 в импульсные последовательности .

Импульсные последовательности с выхода дельта-модулятора 7 поступают на блоки 8, на выходе которых

появляется импульс только в том случае, если на их вход поступают либо два следующих друг за другом импульса, либо две паузы. Далее на выбранном канальном интервале в анализато|ре 9 идет подсчет числа импульсов с выходов блоков 8, а затем сравнение показаний счетчиков анализатора 9 и на выход последнего выдается импульс на открытие того канала, в котором показание счетчика анализатора 9 будет максимальным. В остальных же счетчиках фиксируется число импульсов, которое оказалось на момент сравнения, и в следующий период анализа они начинают считать импульсы, поступающие с блока 8 именно ;с этих фиксированнвх показаний. Таким образом более активные параметры будут опрашиваться чаще, а менее активные - реже. Если в момент сравнения показания нескольких счетчиков одинаковы, то работает узел 1, который пропускает на выход импульс с того входа, который соответствует наименьшему номеру ;каналов. Если на вход логической : схемы узла 1 поступил импульс с выхода одного из блоков 8, то каскады логической схемы пропускают этот импульс на выход, не оказывая на нег никого воздействия. Если же импульсы появятся сразу с нескольких блоко 8, то на выходе логической схемы будет импульс с того входа, который соответствует наименьшему номеру каналов. В результате этого при поступлении импульсов с ангшизатора 9 группами (по два, три и т.д.) узел I организует дисциплину обслуживания в порядке нумерации каналов.

Импульс с выхода узла 1 поступает на вход блока 2, который представляет собой запоминающее устройство номеров каналов адаптивного коммутатора в двоичном коде. Причем адрес номера канала, содержащий одни нули, должен быть запрещенным. Запись номеров каналов в двоичном коде производится перед работой. Если необходимо сменить адреса в процессе работы, то в составе передающей аппаратуры имеется программное устройство с записанными адресами номеров , каналов , которое включается по соответствующей команде. Для этого блок 2 должен иметь каскады ввода адресов и устройство считывания, а элементы памяти должны сохранять записанную информацию при считывани

Выходы узла 1 являются обмотками считывания блока 2. Импульс, поступающий по одному из выходов узла 1, является сигналом считывания номера соответствующего, канала в двоичном коде. Двоичное число в паралельном

коде поступает на блок 3, представляющий собой отдельные триггерные ячейки памяти без взаимных связей друг с другом. В конце каждого канального интервала триггеры блока 3 устанавливаются в нулевое состояние импульсами сброса, поступающими с синхронизатора передающей аппаратуры.

Сигналы с выхода блока 2 поступают на единичные входы триггеров блока 3, следовательно, адрес -номера канала в двоичном коде переписывается из ячеек блока 2 в ячейки блока 3. В соответствии с записанным числом ,в блоке 3 возбуждается соответству ющая выходная диодная матрица 4 и открывается ключ 5 данного канала. Диодная матрица 4 обычная, но запрещенной является комбинация, состоящая из одних нулей.

Напряжение с датчика, прошедшее через ключ 5, поступает на аналогоцифровой преобразователь, в котором к измерительной информации приписывается адфес номера канала, поступающий с блока 2.

Таким образом пропускная способность устройства значительно повышается.

Формула изобретения

Адаптивный коммутатор,содержащий узел выбора каналов, последовательно соединенные блок статической памяти адресов, блок динамической памяти адресов и диодную матрицу, выходы которой соединены с управляющими входами.ключей, причем входы блока статической памяти соединены с соответствующими выходами узла выбора каналов, о т л.и ч а ющ и и с я тем,что , с целью повышения пропускной способности, введены п цепей из последовательно соединенных дельта-модулятора, блока преобразования импульсной последовательности и анализатора импульсно последовательности (где п - число каналов), причем входы дельта-модуляторов соединены с информационными входами ключей, а выходы анашизаторов импульсной последовательности соединены с соответствующими входам узла выбора каналов.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-04-07—Публикация

1980-06-06—Подача