1

Изобретение относится к автоматике и вычислительной технике, в частности к аналоговым запоминающим устройствам, и может быть использовано в вычислителях с . временным разделением обработки информации.

Известно аналоговое запоминающее устройство, содержащее входйой операционный усилитель, накопительный элемент, например конденсатор, делитель напряжения, выходной операционный усилитель, выход которого через элемент обратной связи соединен с инвертирующим входом входного операционного усилителя, буферный каскад, вход которого соединен с одной из обкладок конденсатора и через ключ с делителем напряжения г 1.

Недостатком данного устройства является наличие динамической Ощибки при переходе из режима выборки в режим хранения, а также сложность схемного выполнения.

Наиболее близким к предлагаемому по технической сущности является аналоговое запоминающее устройство, , которое содержит входной и выходной операционные усилители, охваченные через первый пассивный элемент, например резистор, отрицательной

обратной связью, накопительный элемент, например конденсатор, обкладки которого соединены с шиной нулевого потенциала с неинвертирующим входом выходного усилителя, шунтирующий выхОд входного усилителя, первый ключ, второй ключ, соединенный с выходом входного усилителя и шину управления 2.

Однако это запоминающее устройство имеет две существенные динамические ошибки, появляющиеся в устройстве при переходе его с этапа выборки на этап хранения. Первая из них обусловлена наличием разрядного тока конденсатора через паразитные емкость затвор-исток второго ключа от перепада управляющего напряжения U упр, и емкость сток-исток этого же ключа от перепада напряжения на выходе входного усилителя при работе его от аналогового коммутатора. Вторая ошибка обусловлена наличием высокочастотной генерации контура в режиме выборки.

Цель изобретения - повышение точности аналогового запоминающего устройства.

Поставленная цель достигается тем. что в аналоговое запоминающее устройство, содержащее первый накопительный элемент.

например первый конденсатор, одна из обкладок которого соединена с шиной нулевого потенциала, входной операционный усилитель, инвертирующий вход которого соединен с.выходом первого ключа, выходной операционный усилитель, охваченный по инвертирующему входу отрицательной обратной связью, другая обкладка первого конденсатора соединена с неинвертирующим входом выходного операционного усилителя, выход которого подключен к выходу устройства и через первый пассивный элемент, например первый резистор, к инвертирующему входу входного операционного усилителя, выход которого соединен с информационными входами первого и второго ключей, щину управления, соединенную с управляющим входом второго ключа, введены второй накопительный элемент, например второй конденсатор, инвертор, второй и третий пассивные элементы, например резисторы, и третий ключ, информационный вход которого соединен с входом устройства, управляющий вход третьего ключа соединен с щиной управления и входом инвертора, выход которого соединен с управляющим входом первого ключа, выход третьего ключа соединен с неинвентирующим входом входного операционного усилителя и через второй резистор с выходом выходного операционного усилителя, выход второго ключа соединен через третий резистор с другой обкладкой первого конденсатора, выход входного операционного усилителя подключен к одной из обкладок второго конденсатора, другая обкладка которого соединена с инвертирующим входом входного операционного усилителя.

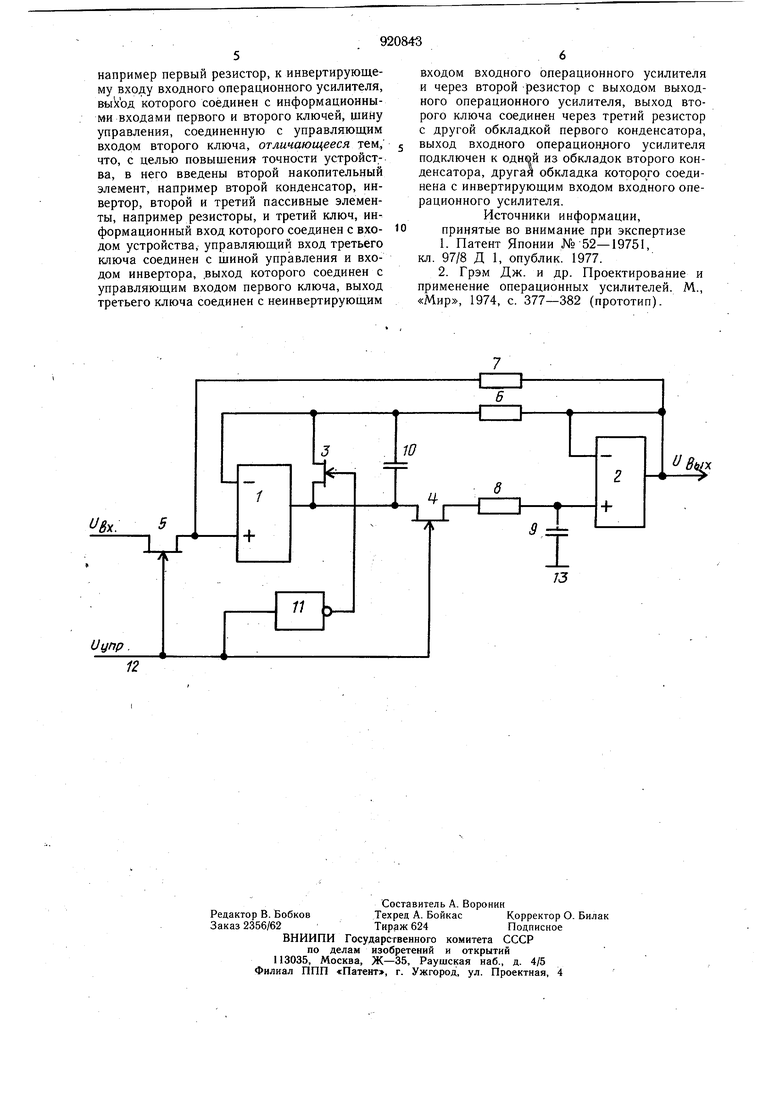

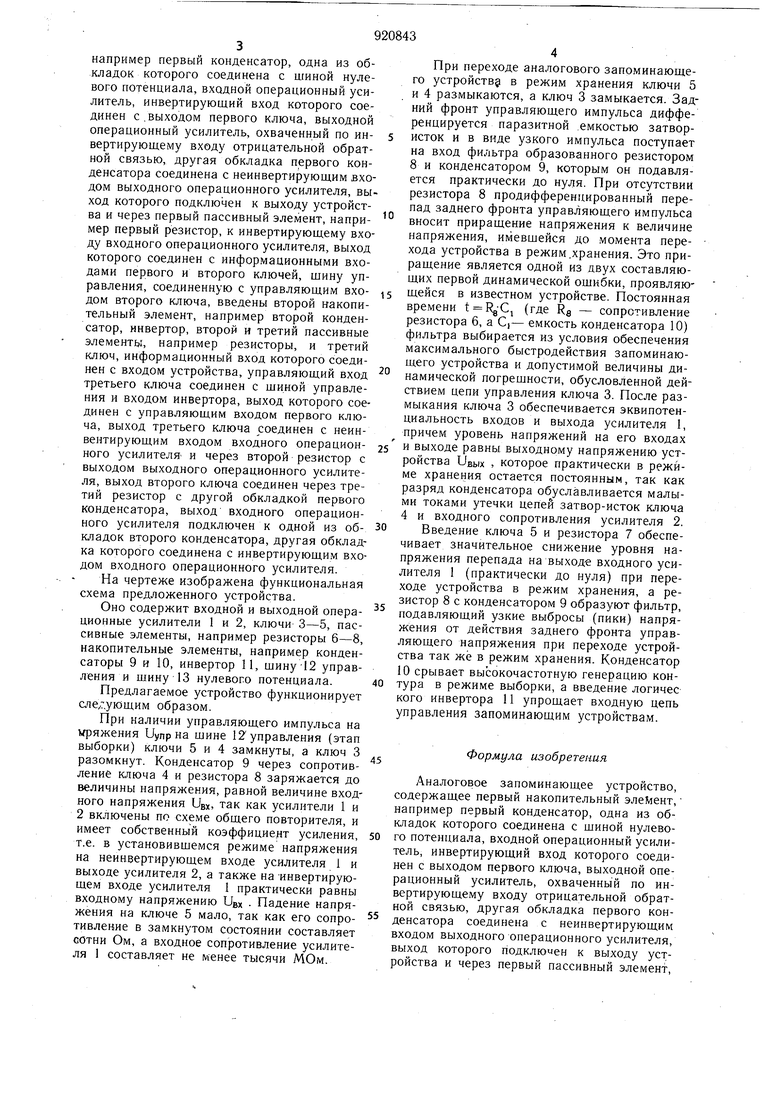

На чертеже изображена функциональная схема предложенного устройства.

Оно содержит входной и выходной операционные усилители 1 и 2, ключи 3-5, пассивные элементы, например резисторы б-8, накопительные элементы, например конденсаторы 9 и 10, инвертор 11, щину12 управления и щину 13 нулевого потенциала.

Предлагаемое устройство функционирует следующим образом.

При наличии управляющего импульса на мряжения Uynp на щине 12 управления (этап выборки) ключи 5 и 4 замкнуты, а ключ 3 разомкнут. Конденсатор 9 через сопротивление ключа 4 и резистора 8 заряжается до величины напряжения, равной величине входного напряжения UBX, так как усилители 1 и 2 включены по схеме общего повторителя, и имеет собственный коэффициент усиления, т.е. в установивщемся режиме напряжения на неинвертирующем входе усилителя 1 и выходе усилителя 2, а также на инвертирующем входе усилителя 1 практически равны входному напряжению UBX . Падение напряжения на ключе 5 мало, так как его сопротивление в замкнутом состоянии составляет сотни Ом, а входное сопротивление усилителя 1 составляет не менее тысячи МОм.

При переходе аналогового запоминающего устройств в режим хранения ключи 5 и 4 размыкаются, а ключ 3 замыкается. Задний фронт управляющего импульса дифференцируется паразитной .емкостью затвористок и в виде узкого импульса поступает на вход фильтра образованного резистором 8 и конденсатором 9, которым он подавляется практически до нуля. При отсутствии резистора 8 продифференцированный перепад заднего фронта управляющего импульса вносит приращение напряжения к величине напряжения, имевщейся до момента перехода устройства в режим .хранения. Это приращение является одной из двух составляющих первой динамической ощибки, проявляющейся в известном устройстве. Постоянная времени t Rg-C, (где Rg - сопротивление резистора 6, а Cj- емкость конденсатора 10) фильтра выбирается из условия обеспечения максимального быстродействия запоминающего устройства и допустимой величины динамической погрещности, обусловленной действием цепи управления ключа 3. После размыкания ключа 3 обеспечивается эквипотенциальность входов и выхода усилителя I, причем уровень напряжений на его входах

5 и выходе равны выходному напряжению устройства ОЕЫХ , которое практически в режиме хранения остается постоянным, так как разряд конденсатора обуславливается малыми токами утечки цепей затвор-исток ключа 4 и входного сопротивления усилителя 2.

Введение ключа 5 и резистора 7 обеспечивает значительное снижение уровня напряжения перепада на выходе входного усилителя 1 (практически до нуля) при переходе устройства в режим хранения, а резистор 8 с конденсатором 9 образуют фильтр, подавляющий узкие выбросы (пики) напряжения от действия заднего фронта управляющего напряжения при переходе устройства так же в режим хранения. Конденсатор 10 срывает высокочастотную генерацию контура в режиме выборки, а введение логичес кого инвертора 11 упрощает входную цепь управления запоминающим устройствам.

Формула изобретения

Аналоговое запоминающее устройство, содержащее первый накопительный элемент, например первый конденсатор, одна из обкладок которого соединена с щиной нулевого потенциала, входной операционный усилитель, инвертирующий вход которого соединен с выходом первого ключа, выходной операционный усилитель, охваченный по инвертирующему входу отрицательной обратной связью, другая обкладка первого конденсатора соединена с неинвертирующим входом выходного операционного усилителя, выход которого подключен к выходу устройства и через первый пассивный элемент.

например первый резистор, к инвертирующему входу входного операционного усилителя, выход которого соединен с информационными входами первого и второго ключей, шиНу управления, соединенную с управляющим входом второго ключа, отличающееся тем, что, с целью повышения точности устройства, в него введены второй накопительный элемент, например второй конденсатор, инвертор, второй и третий пассивные элементы, например резисторы, и третий ключ, информационный вход которого соединен с входом устройства, управляющий вход третьего ключа соединен с шиной управления и входом инвертора, выход которого соединен с управляющим входом первого ключа, выход третьего ключа соединен с неинвертирующим

входом входного операционного усилителя и через второй резистор с выходом выходного операционного усилителя, выход второго ключа соединен через третий резистор с другой обкладкой первого конденсатора, выход входного операционлого усилителя подключен к одной из обкладок второго конденсатора, другая обкладка которого соединена с инвертирующим входом входного операционного усилителя.

Источники информации, принятые во внимание при экспертизе

1.Патент Японии №52-19751, кл. 97/8 Д 1, опублик. 1977.

2.Грэм Дж. и др. Проектирование и применение операционных усилителей. М., «Мир, 1974, с. 377-382 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1987 |

|

SU1531173A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU769632A1 |

| Аналоговое запоминающее устройство | 1984 |

|

SU1223308A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU963105A1 |

| Аналоговое запоминающееуСТРОйСТВО | 1979 |

|

SU809392A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU830584A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU991514A1 |

| Аналоговое запоминающее устройство | 1985 |

|

SU1305780A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1065889A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU928420A1 |

J

ивх.

;/

Ugnp,

Авторы

Даты

1982-04-15—Публикация

1980-07-04—Подача