(5) БЛОК СИНХРОНИЗАЦИИ ДЛЯ СЧИТЫВАОДИХ УСТРОЙСТВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок синхронизации для считывающих устройств | 1979 |

|

SU790004A1 |

| Устройство для записи и считывания информации | 1979 |

|

SU963010A1 |

| Устройство для записи информации в оперативную память | 1982 |

|

SU1049966A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ И КОНТРОЛЯ ИНФОРМАЦИИ - | 1979 |

|

SU826375A1 |

| Устройство для обучения основам вычислительнй техники | 1981 |

|

SU1005156A1 |

| Устройство для ввода информации | 1979 |

|

SU798913A1 |

| Устройство для ввода информации | 1980 |

|

SU943692A1 |

| Устройство для ввода информации | 1980 |

|

SU945858A1 |

| Устройство для ввода графичес-КОй иНфОРМАции | 1979 |

|

SU798916A1 |

| Устройство управления многоканальной информационно-измерительной системой | 1977 |

|

SU693374A1 |

Изобретение относится к вычисли-, тельной технике и может быть использовано в координатных пультах ввода информации и считывающих устройствах .

M3BecteH блок синхронизации для считывающих устройств, содержащий генератор импульсов, подключенный к счетчику, выходы которого подключены к дешифраторам, распределитель импульсов Ц.

Однако такой о(1ладает малым быстродействием и ограниченными возможностями синхронизации.

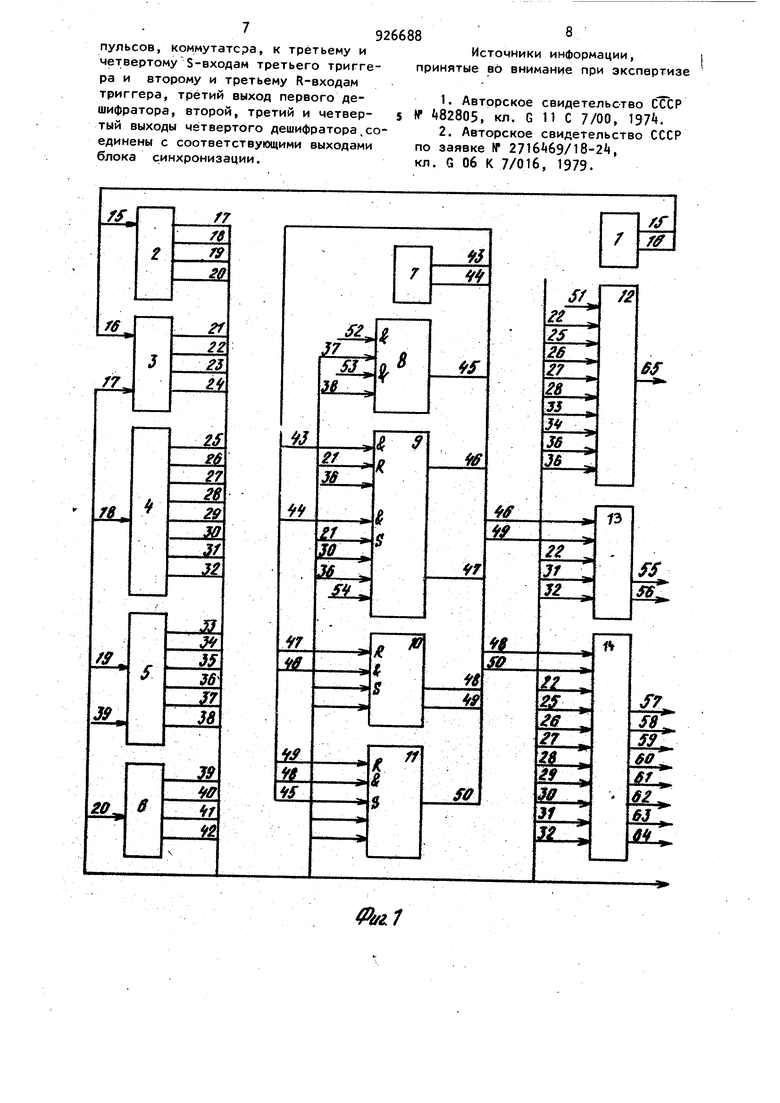

Наиболее близким к изобретению является блок синхронизации для считывающих устройств, содержащий генератор импульсов, первый выход которого подключен к входу счетчика, первый , второй , третий и четвертый выходы которого подключены к первому входу первого, к входу второго, к первому входу третьего и к входу четвертого дешифраторов соответственно, первый и второй распределители импульсов, первый и второй триггеры, блок управления, первый и второй выходы которого подключены соответственно к первому R-входу и первому S-входу первого триггера, неинвертируемый выход первого триггера подключен к первому S-входу второго триггера и первому входу второго распредели10теля импульсов, инвертируемый выход первого триггера подключен к R-входу второго триггера, инвертируемый выход КОТОРОГО подключен ко второму входу второго распредели15теля импульсов, второй выход генератора импульсов подключен к синхронизирующему входу первого дешифратора, первый выход четвертогодешифратора подключен к синхронизи30рующему входу третьего дешифратора, первый,второй и четвертый выходы первого, выходы второго и первый, второй, третий и четвертый выходы третьего дешифраторов подключены к синхронизирующим входам первого и второго распредилетелей импульсов, ко второму,третьему и четвертому S-входам первого триггера, ко второму и третьему S-входам второго триггера 2 Однако такой блок имеет ограниченные возможности синхронизации и недостаточную надежность из-за сбое синхронизации. Цель изобретения - повышение надежности. Указанная цель достигается тем, что в блок синхронизации для считы вающих устройств введены коммутатор третий распределитель импульсов и третий триггер, причем неинвертиру емый выход второго триггера подключен к первому S-входу третьего триггера и первому входу третьего распределителя импульсов, инвертиру мый выход второго триггера подклю чен к R-входу третьего триггера, ин вертируемый выход третьего триггера подключен ко второму входу третьего распределителя импульсов, выход коммутатора подключен ко второ му S-входу третьего триггера, пятый S-вход первого триггера, первый и второй входы коммутатора являются соответствующими входами блока синх ронизации, второй выход первого, вы ходы второго и третьего .дешифраторов подключены к синхронизирующим входам третьего распределителя импульсов, коммутатора, к третьему и четвертому S-входам третьего триг гера и второму и третьему R-входам первого триггера, третий выход первого дешифратора, второй , третий и четвертый выходы- четвертого дешифра тора соединены с соответствующими выходами блока синхронизации. На фиг, 1 представлена структур ная схема блока; на фиг.2- временны диаграммы работы дешифраторов 3,,5 на фиг. 3 - диаграммы работы второго и третьего распределителей 13 и 1 импульсов. В состав блока входят генератор 1 импульсов, счетчик 2, дешифраторы Зб, блок 7 управления, коммутатор 8, триггеры , распределители IZ-I импульсов. Обозначены связи 15-50 между блоками, входы 515 уп равления, выходы 55-6 второго и третьего распределителей импульсов 84 13 и 14; выход 65 первого распределителя импульсов. Первый выход 15 генератора 1 импульсов подключен к счетчику 2, а второй выход 16 - ко входу синхронизации первого дешифратора 3. Первые выходы 17 счетчика 2 (разряды 1,2) подключены к дешифратору 3. Вторые вь ходЪ1 18 счетчика 2 (разряды 3,.5)подключены к дешифратору 4, третьи 19 (разряды 6,7,8) подкл№ е«ы « дешифратору 5, а четвертые выходы. 20 (старшие разряды) подклЬ(ёны к дешифратору. 6. Пёрши выход 39 четвертого дешифратора 6 подключён ко входу блокировки третьего дешифратора 5Выхода и kk блока 7 управления подключены к первому К-входу и переому S-вхбду триггера 9, неинвертируёмый выход 6 которого подключен к первому S-входу триггера 10 и перВО1 входу второго распредели теля импульсов 13, а инвертируемый выход k7 - к R-входу триггера 10. Нейнвертируемый выход 48 триггера t О подключен к первому S-входу триггера и первому входу третьего , распределителя Ц импульсов, а инеертирую мый выход 3 - к R-входу триггера П и ко второму входу второго распределителя 13 импульсов. Ин&ертируемый выход 50 триггера 11 подключен ко второму входу третьего распределителя И импульсов. Выход 15 коммутатора 8 подключен ко второму S-вхОду триггера 11. Выходы дешифраторов подключены ко входам синхронизации распределителей 12-Н импульсов, коммутатора 8,ковторому и третьему R-аходам и ко второму, третьему и четвертому $-входам триггера 9, ко второму и третьему З-входам триггера 10, третьему и четвертому S-входам триггера 11, Блок синхронизации работает следующим образом. Генератор 1 импульсов непрерывно воздействует на счетный вход счетчика 2, код которого поступает на вхОды дешифраторов . Временная диаграмма работы дешифраторов показана на фиг. 2. Основные такты работы блока за каждый период его работы определяются дешифратором 6. Дешифраторы 3 и 4 работают в каждом такте, а дешифратор 5- только в первом такте. ПерЬый распределитель

12импульсов работает только в первом такте. Его работа частично управляется кодом координат, поступающим от координатного пульта ввода информации (не показан.) Опросные импульсы с выходов первого распределителя 12 импульсов поступают только а систему кодирующих элементов координатного пульта.

Второй и.третий распределители

13и 1 импульсов работают только при нажатии кнопки блока 7 управлег ния (не показана). При нажатии кнопки блока 7 управления происходит последовательная установка в 1 триггеров 9-11 согласно.временной диаграмме (фиг, 3),

Однако первый триггер 9 устанав- . ливается в 1 только при поступлении на его S-вход S сигнала от схемы контроля преобразователя кода координатного пульта ввода информации, В случае некоторых неправильных действий оператора пуск распределителей 13 и 1 импульсов не производится,.

Второй распределитель 13 импульсов всегда однократно вырабатывает только два импульса на выходах 55 и 5б), Работа третьего распределителя 14 импульсов зависит ot работы коммутатора 8. В случае поступления на вход 52 управлякйцего сигнала от координатного пульта третий распределитель 14 импульсов однократно вырабатывает восемь импульсов (на выходах 57-64), Однако при поступлении сигнала на другой вход 53 коммутатора 8 третий распределитель 14 импульсов работает многократно (до 8) обеспечивая при этом в координатном пульте ввод нескольких байтов, например, из долговременной памяти.

Работа распределителей 13 и 14 импульсов может возобновляться только при новом нажатии кнопки блока 7 управления. Преждевременный сброс распределителей 14 импульсов устраняется за счет поступления на R-BXOды первого триггера 9 импульсов синхронизации с выходов 21 и Зб первого и третьего дешифраторов 3 и 5Введение в известный блок новых элементов и связей повышает его надежность и расширяет возможности синхронизации.

Формула изобретения Блок синхронизации для считывающих устройств, содержащий генератор импульсов, первый выход которого подключен к входу счетчика, первый, второй, третий и четвертый выходы которого подключены к первому входу первого, к входу второго, к первому входу третьего и к входу четвертого дешифраторов соответственно, первый и второй распредилители импульсов, первый и второй триггеры, блок управления, первый и второй выходыкоторого подключены соответственно к первому R-входу и первому S-входу первого триггера, неинвертируемый выход первого триггера подключен к первому S-входу второго триггера и первому входу второго распределителя импульсов, инвертируемый выход первого триггера подключен к R-входу второго триггера, инвертируемь й выход которого подключен к второму входу второго распределителя импульсов, второй выход генератора импульсов подключен к синхронизирующему входу первого дешифратора, первый в.ыход четвертого дешифратора подключен к синхронизирующему входу третьего дешифратора, первый, второй и четвертый выходы первого, выходы второго и первый, второй, третий и четвертый выходы третьего дешифраторов подключены к синхронизирующим входам первого и второго распределителей импульсов, к второму, третьему и четвертому S-входам первого триггера , к второрому и третьему S-входам второго триггера, отличающийся тем, что, с целью повышения надежности, в него введены коммутатор, третий распределитель импульсов и третий ; триггер, причем неинвертируемый выход второго триггера подключен к первому S-входу третьего триггера и первому входу третьего распределителя импульсов, инвертируемый выход второго триггера подключен к R-входу третьего триггера, инвертируемый выход третьего триггера подключен к второму входу третьего распределителя импульсов, выход коммутатора подключен к второму S-входу третьего триггера, пятый S-вход первого триггера, первый 1 второй входы коммутатора являются соответствующими входами блока синхронизации, второй выход первого, выходы второго и третьего дешифраторов подключены к синхронизирующим |входам третьего распределителя им9266пульсов, коммутатсра, к третьему и четвертому S-входам третьего триггера и второму и третьему R-входам триггера, третий выход первого дешифратора, второй, третий и четвертый выходы четвертого дешифратора,соединены с соответствующими выходами блока синхронизации. 5

ffi7 8 Источники информации, принятые вб внимание при экспертизе 1.Авторское свидетельство СССР N «82805, кл. G П С 7/00, 197. 2.Авторское свидетельство СССР по заявке ff 2716 69/18-24, кл. G 06 К 7/016, 1979.

f-JT.

n 26П.

n

n

n

n

n

H9.

f. .

y-JJ-г

f

n

n

n

n

Авторы

Даты

1982-05-07—Публикация

1980-04-04—Подача