рого соединен с первым входом второго элемента И, второй вхоц которого и первый вхоа третьего элемента И поа- . ключены к выхоау первого триггера, второй вхоа первого элемента И и третьи единичные входы второго и третьего триггеров соединены с тридцать четвертым выходом генератора синхросигналов, тридцать пятый выход которого aajisiется другим выходом синхронизации уст ройства, а тридцать шестой выход подключен к второму входу третьего элемента И, выходы с первого по четверты распределителя сигналов являются одни1046 ми из управляющих выходов устройства, а пятый и шестой выходы подключены со ответственно к нулевому входу второго триггера и к первому нулевому входу третьего триггера, второй нулевой вход которого соединен с выходом первого элемента И, выходы с седьмого по десятый распределителя сигналов подключены к управляющим входам коммутатора и являются другими управляющими выходами устройства, выходы коммутатора являются другими информационными выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи информации в оперативную память | 1982 |

|

SU1089624A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ И КОНТРОЛЯ ИНФОРМАЦИИ - | 1979 |

|

SU826375A1 |

| Устройство для записи информации в оперативную память | 1982 |

|

SU1092562A1 |

| Устройство для записи информации в оперативную память | 1981 |

|

SU1005184A1 |

| Устройство для ввода информации | 1979 |

|

SU798913A1 |

| Устройство для контроля средств числового программного управления | 1988 |

|

SU1675852A1 |

| Устройство для ввода графичес-КОй иНфОРМАции | 1979 |

|

SU798916A1 |

| Устройство для записи информации в оперативную память | 1986 |

|

SU1322371A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

| Устройство для записи информации в оперативную память | 1982 |

|

SU1208582A1 |

1

Изобретение относится к вычислительной технике и может быть использовано для записи информации в оперативную память..

Известно устройство для записи информации в оперативную память, соцер жащее блок ввода, входы которого подключены к выходам блока синхронизации, а выход - к информационному входу преобразователя последовательного кода в параллельный ij .

Недостатком этого устройства является ограниченная область его применения.

Наиболее близким к изобретению по технической сущности является устройств для записи информации в оперативную память, содержащее блок ввода, преобразователь последовательного кода в параллельный, блок синхронизации, первый восьмой выходы которого подключены к трактирующим входам блока ввода и преобразователя последовательного кода в параллельный, девятый, десятый и одиннадцатьй выходы - к вхоцам синхронизации блока ввода, двенадцатый выход к входу установки О преобразователя последовательного кода в параллельный, информационный вход которого подключен к выходу блока ввода, входы ввода параллельного кода подключены к тринадцатому, четы|Я1адцатому, пятнадцато лу выходам блока синхронизации, а выходы к первым информационным выходам устройства 2 .

Недостатком этого устройства является то, что в нем отсутствует возможКОСТЬ преобразования последовательного кода в двоично-деся тичный код и возможность передачи его в оперативную память, что ограничивает область его применения.

Цель изобретения - расширение области применения устройства за счет выполнения записи двоично-десятичных чисел в оперативную память.

0

Поставленная цель достигается тем, что в устройство для записи информации в оперативную память, содержащее генератор синхросигналов, выходы которого с первого по восьмой подключены к вхо5дам опроса первого преобразователя кода и формирователя информационных сигналов, входы синхронизации которого соединены с выходами с девятого по одиннадцатый генератора синхросигналов,

0 двенадцать выход которого подключен к входу установки первого преобразователя кода, информационный вход которого соединен с выходом формирователя информационных сигналов, а управляющие вхо5ды - с выходами с тринадцатого по пят надцатый генератора синхросигналов, причем выходы первого преобразователя кода являются одними из информационных выходов устройства, введены дешифратор,

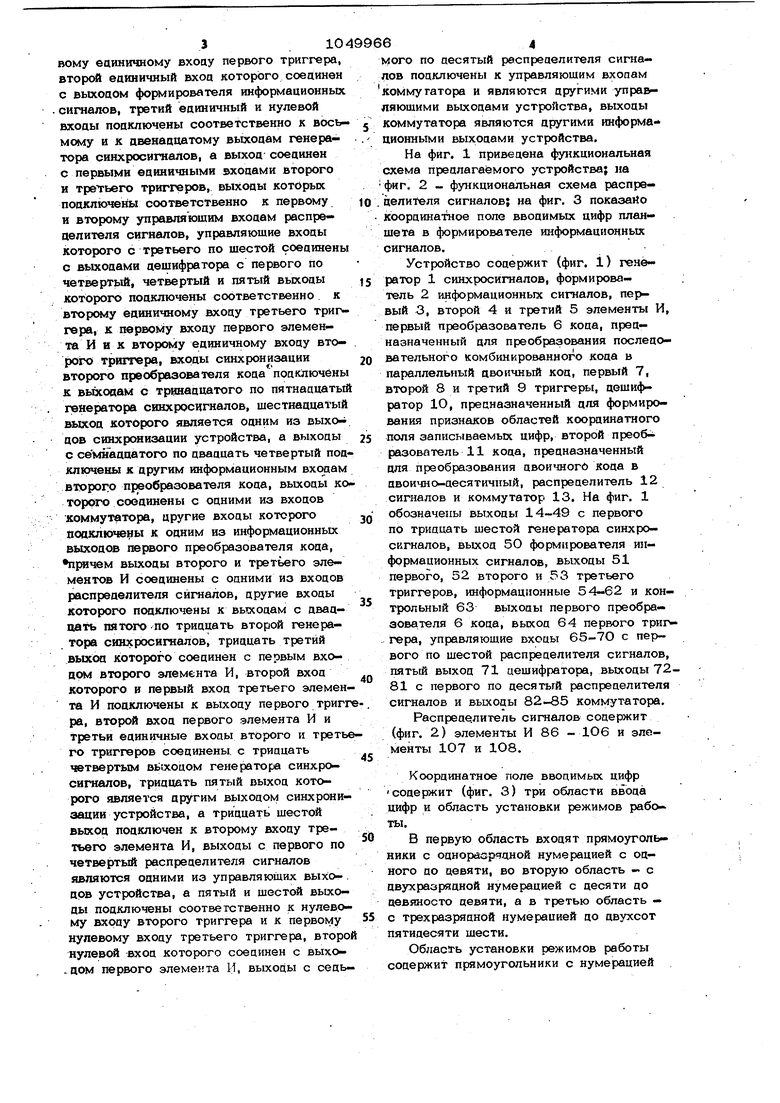

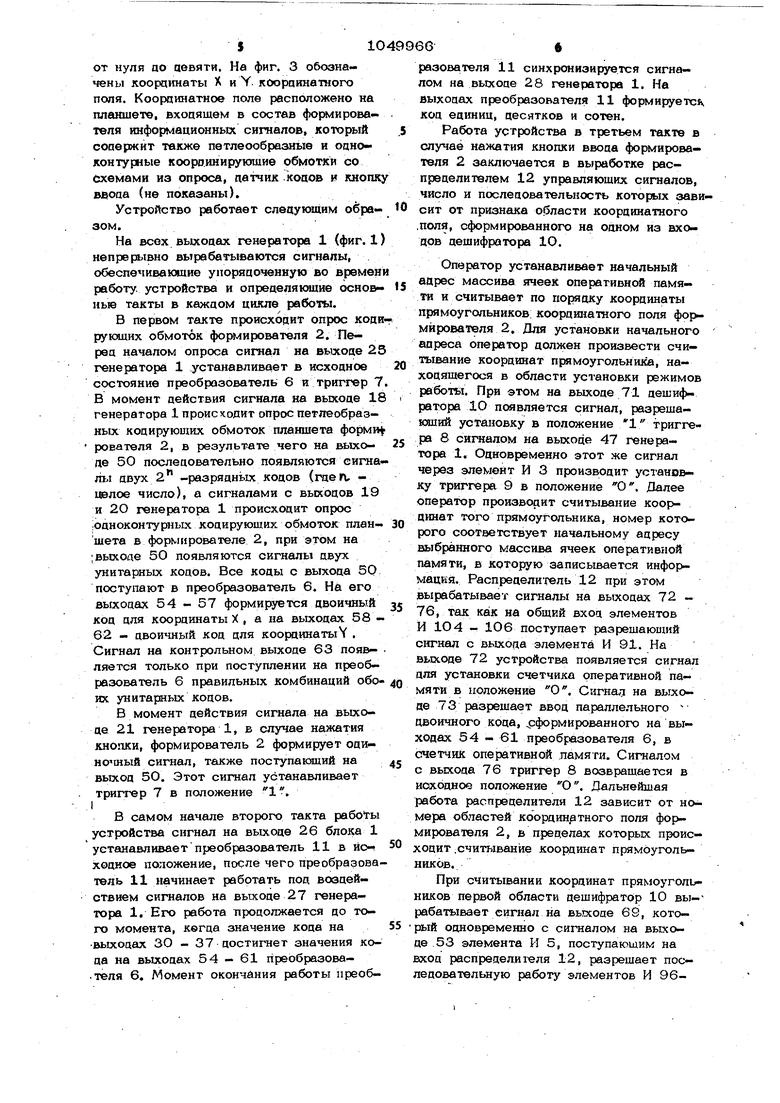

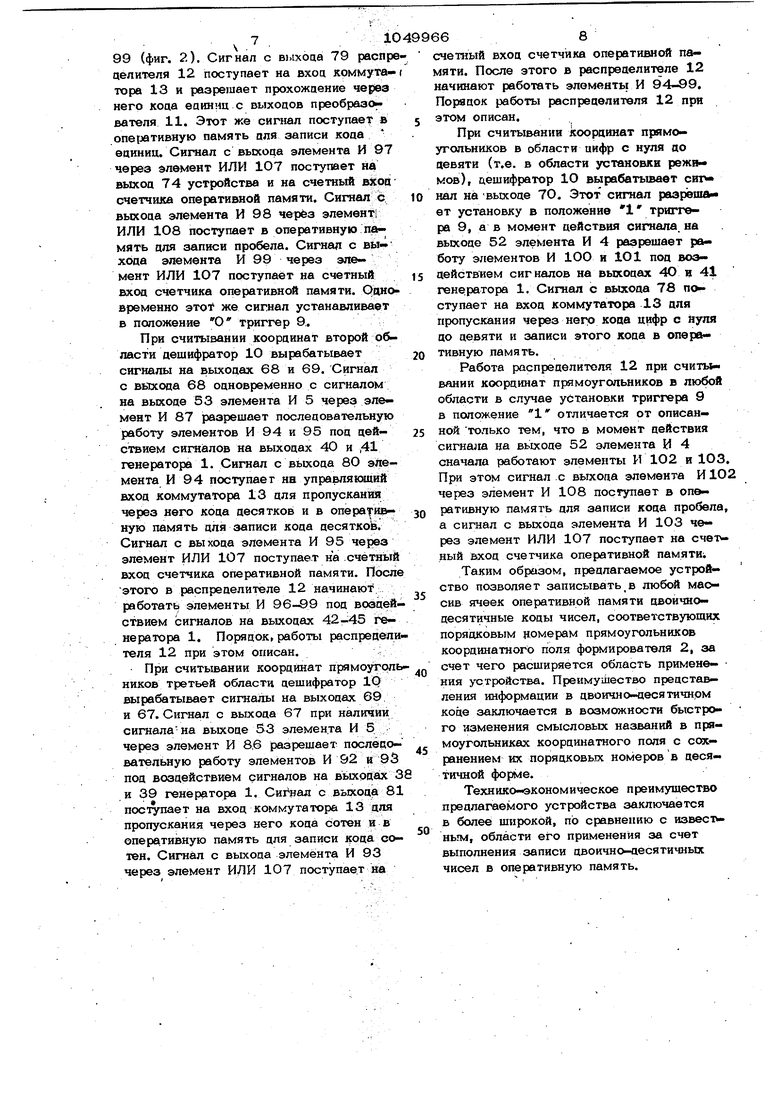

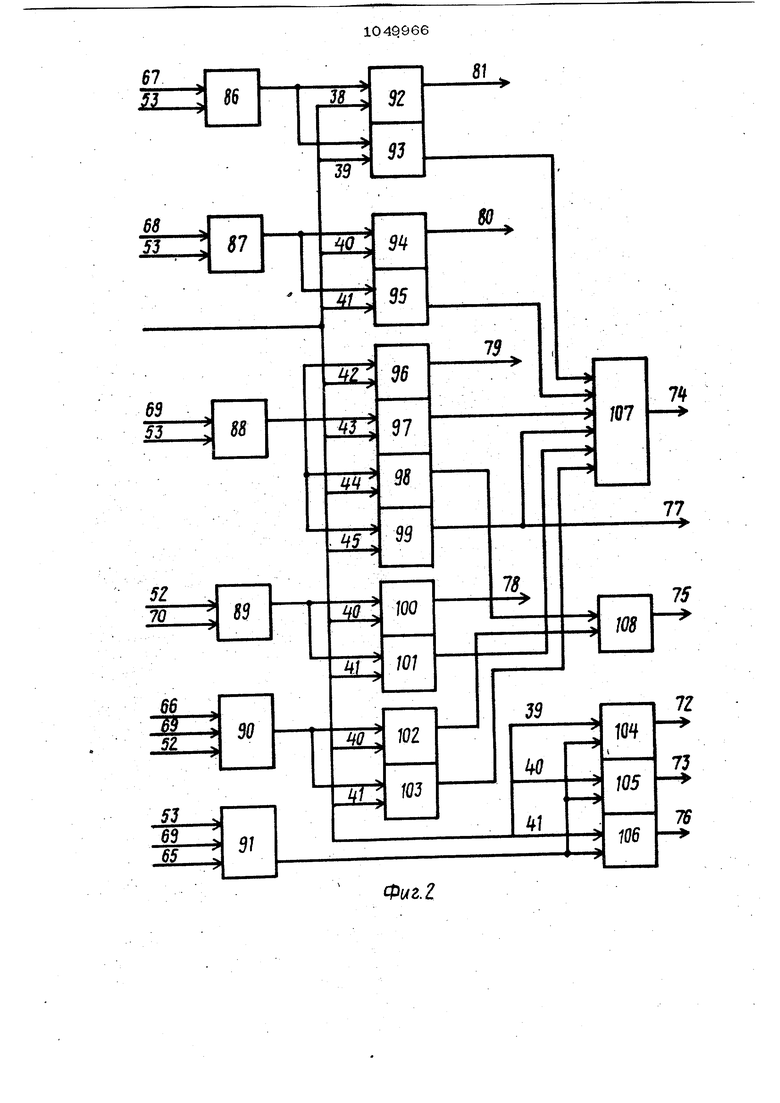

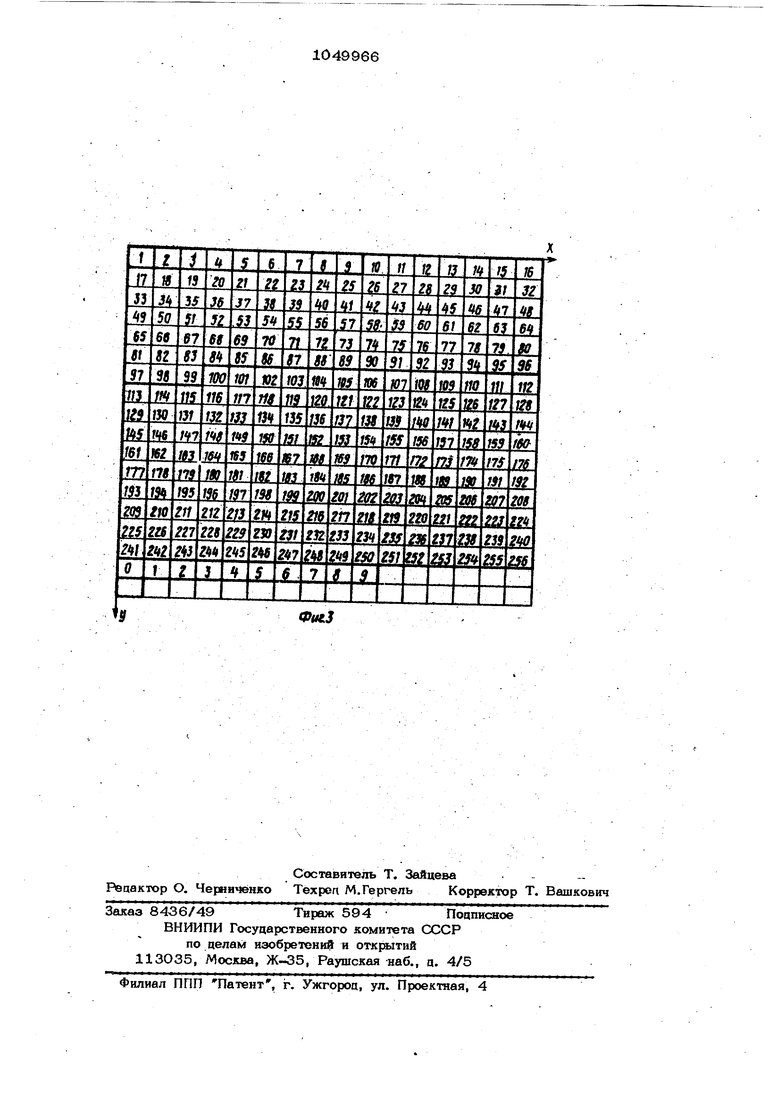

0 | распределитель сигналов, триггеры, эле- . менты И, коммутатор и второй преобразователь кода, одни из информационных входов которого и входы дешифратора соединены с информационными выходами первого преобразователя кода, контрольный выход которого подключен к первому еаиничному входу первого триггера, второй единичный вхоц которого соецинен с выходом формирователя информационных .сигналов, третий единичный и нулевой входы подключены соответственно к восьмому и к цвенадцатому выходам генератора сннхросигналов, а выход соединен с первыми единичными входами второго и третьего триггеров, выходы которых подключены соответственно к первому и второму управляющим входам распределителя сигналов, управляющие входы которого с третьего по щестой соединены с выходами дешифратора с первого по чвтверть1Й, четвертый и пятый выходы которого подключены соответственно к второму единичному входу третьего триггера, к первому входу первого элемента И их второму единичному входу второго триггера, входы синхронизации второго преобразователя кода подключены к выхоаам с тринадцатого по пятнадцаты генератора синхросигналов, шестнадцатый которого является одним из выходов синхронизации устройства, а выходы с семнадцатого по двадцать четвертый под ключены к другим информационным входам второго преобразователя кода, выхоцы ко торого соединены с одними из входов коммутатора, другие входы которого подключе1)1Ы к одним из информационных выходов первого преобразователя кода, причем выходы второго и третьего элементов И соединены с оаними из входов распределителя сигналов, другие входы которого подключены к выходам с двадцать пятогоПО тридцать второй генератора синхросигналов, тридцать третий выход которого соединен с первым входом второго элемента И, второй вход которого и первый вход третьего элемен та И подключены к выходу пе рвого тригг ра, второй вход первого элемента И и третьи единичные вхоаы второго и треть го триггеров соединены с тридцать четвертым BtixoaoM генератора синхросигналов, тридцать пятый выход которого является другим выходом синхронизации устройства, а тридцать щестой выход подключен к второму входу третьего элемента И, выходы с первого по четвертый распределителя сигналов являются одними из управляющих выхо-. дрв устройства, а пятый и щестой выходы подключены соответственно к нулевому входу второго триггера и к первому нулевому входу третьего триггера, второ нулевой вход которого соединен с выхо.дом первого элемента И, выхоцы с седь- Kjoro по десятый распределителя сигналов подключены к управляющим входам коммутатора и являются другими управляющими выходами устройства, выходы коммутатора являются другими информа ционными выходами устройства. На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема распре- целителя сигналов; на фиг. 3 показало координатное поле вводимых цифр планшета в формирователе информационных сигналов. Устройство содержит (фиг. 1) генератор 1 синхросигналов, формирователь 2 информационных сигналов, 3, второй 4 и третий 5 элементы И, первый преобразователь 6 кода, предназначенный для преобразования последовательного комбинированного кода в параллельный двоичный код, первый 7, второй 8 и третий 9 триггеры, дещи4 ратор 10, предназначенный для формирования признаков областей координатного поля записываемых цифр, второй преобразовотель 11 кода, предназначенный для преобразования двоичного кода в двоично-десятичный, распределитель 12 сигналов и коммутатор 13. На фиг. 1 обозначены выходы 14-49 с первого по тридцать шестой генератора синхросигналов, выход 50 формирователя информационных сигналов, выходы 51 первого, 52 второго и 53 третьего триггеров, информационные 54-62 и контрольный 63 выходы первого преобра- зова.теля 6 кода, выход 64 первого триг- Гера, управляющие входы 65-7О с первого по щестой распределителя сигналов, пятый выход 71 дешифратора, выходы 7281 с первого по десятый распределителя сигналов и выхоцы 82-85 коммутатора. Распределитель сигналов содержит (фиг. 2) элементы И 86 - 1О6 и элементы 107 и 1О8. Координатное поле вводимых цифр -содержит (фиг, 3) три области ввода цифр и область установки режимов рабо ты. В первую область входят прямоугольники с одноразрядной нумерацией с одного до девяти, во вторую область - с двухразрядной нумерацией с десяти до девяносто девяти, а в третью область - с трехразрядной нумерацией до двухсот пятидесяти шести. Облас гь установки режимов работы содержит прямоугольники с нумерацией S10 от нуля по цевяти. На фиг. 3 обозначены лоорцинаты X и Y координатного поля. Координатное поле расположено на планшете, входящем в состав формирователя информационных сигналов, который содержит также петлеообразные и одноконтурные координирующие обмотки со Схемами из опроса, датчик кодов и кнопк ввода (не показаны). Устройство работает следующим образом. На всех выходах генератора 1 (фиг. 1 непрерывно вырабатываются сигналы, обеспечивающие упорядоченную во времен работу, устройства и определяющие основные такты в каждом цикле работы. В первом такте происходит опрос коди рующих обмоток формирователя 2. Перед началом опроса сигнал на Bbtxocte 25 генератора 1 устанавливает в исходное состояние преобразователь 6 и триггер 7 В момент действия сигнала на выходе 18 генератора 1 происходит опрос петлеобразных кодирующих обмоток планшета форми рователя 2, в результате чего на выходе 5О последовательно появляются сигна- Л1Л двух 2 -разрядньгх кодов (гдеп, целое число), а сигналами с вьсходов 19 и 2О генератора 1 происходит опрос одноконтурных кодирующих обмоток план щета в формирователе 2, при этом на ;выходе 50 появляются сигналы двух унитарных кодов. Все коды с выхода 50 поступают в преобразователь 6. На его выхоцах 54-57 формируется двоичный код для координаты X , а на выходах 5862 - двоичный код цля координатыV . Сигнал на контрольном выходе 63 появ- ляется только при поступлении на преобразователь 6 правильных комбинаций обоих унитарных кодов. В момент действия сигнала на выходе 21 генератора 1, в случае нажатия кнопки, формирователь 2 формирует одиночный сигнал, также поступающий на выход 50. Этот сигнал устанавливает триггер 7 в положение 1. I В самом начале второго такта работы устройства сигнал на выходе 26 блока 1 устанавливает преобразователь 11 в йс- ходкое положение, после чего преобразователь 11 начинает работать под воздействием сигналов на выходе 27 генератора 1. Его работа продолжается до того момента, квгда значение кода на выхоцах ЗО - 37 достигнет значения кода на выходах 54 - 61 преобразова теля 6. Момент окончания работы преоб66разователя 11 синхронизируется сигналом на выходе 28 генератора 1. На выходах преобразователя 11 формируется код единиц, десятков и сотен. Работа устройства в третьем такте в случае нажатия кнопки ввода формирователя 2 заключается в выработке распределителем 12 управляющих сигналов, число и последовательность которых зависит от признака области коорцинатного .поля, сформированного на одном из входов дешифратора 10. Оператор устанавливает начальный адрес массива ячеек оперативной памяти и считывает по порядку координаты прямоугольников: координатного поля фог мйрователя 2, Для установки начального адреса оператор должен произвести считывание координат прямоугольника, находящегося в области установки режимов работы. При этом на выходе 71 дещи(| ратора 10 появляется сигнал, разрещаюший установку в положение 1 триггера 8 снгаал ом на выходе 47 генератора 1. Одновременно этот же сигнал через элемент И 3 производит установку триггера 9 в положение О. Далее оператор производит считывание Koof аннат того прямоугольника, номер которого соответствует начальному адресу выбранного массива ячеек оперативной памяти, в которую записывается инфо{ мацкя. Распределитель 12 при этом вырабатывает сигналы на выходах 72 76, так как на общий вход элементов И 104 - 106 поступает разрешающий сигнал с выхода элемента И 91. На вьгходе 72 устройства появляется сигнал для установки счетчика оперативной памяти в положение О, Сигнал на выходе 73 разрешает ввод параллельного двоичного кода, формированного на выходах 54 - 61 преобразователя 6, в счетчик оперативной .памяти. Сигналом с выхода 76 триггер 8 возвращается в исжодное положение О. Дальнейшая работа распределителя 12 зависит от но мера областей координатного поля формирователя 2, в пределах которьк происходит .считывание координат прямоугольников. При считывании координат прямоугольников первой области дещифратор 10 вы-рабатывает сигнал на вьххопе 69, который одновремешю с сигналом на выходе .53 элемента И 5, поступающим на ход распределителя 12, разрещает последовательную работу элементов И 9699 (фиг. 2). Сигнал с Bi.ixoaa 79 распрецелителя 12 поступает на вход комму та- тора 13 и разрешает прохожаение через него кода ецинмц с выхоцов преобразо вателя 11. Этот же сигнал поступает в oneijaTHBHyro память для записи коаа единиц. Сигнал с выхоца элемента И 97 через элемент ИЛИ 107 поступает на выхоа 74 устройства и на счетный bkoa счетчика оперативной памяти. Сигнал с выхоаа элемента И 98 через элемент ИЛИ 108 поступает в оперативную па мять для записи пробела. Сигнал с выхода элемента И 99 через элемент ИЛИ 1О7 поступает на счетный вход счетчика оперативной памяти. Одновременно 3Tot же сигнал устанавливает в положение О триггер 9.

При считывании координат второй области дешифратор 10 вырабатывает сигналы на выходах 68 и 69. Сигнал с выхода 68 одновременно с сигналом на выходе 53 элемента И 5 через элемент И 87 разрешает последовательную работу элементов И 94 и 95 под действием сигналов на выходах 40 и ,41 генератора 1. Сигнал с выхода 80 элемента И 94 поступает нн управлякмций вход коммутатора 13 для пропускания через него кода десятков и в опера и) ную память для записи кода десяткой. Сигнал с выхода элемента И 95 через элемент ИЛИ 1О7 поступает на счетный вход счетчика оперативной памяти. После этого в распределителе 12 начинают работать элементы И 96-99 под воздействием сигналов на выходах 42-45 генератора 1. Порядок, работы распределителя 12 при этом описан.

При считывании координат прямоугольников третьей области дешифратор 1Q вырабатывает сигналы на выходах 691 и 67. Сигнал с выхода 67 при наличии сигнала-на выходе 53 элемента И 5 через элемент И 8.6 разрешает последовательную работу элементов И 92 и 9 под воздействием сигналов на вьисодах 3 и 39 генератора 1. с выхода 81 поступает на вход коммутатора 13 для пропускания через него кода сотен ив опера.тивную память для записи кода сотен. Сигнал с выхода элемента И 93 через элемент ИЛИ 107 поступает на

счетный вход счетчика оперативной памяти. После этого в распределителе 12 начинают работать элементы И 914-99. Порядок работы распределителя 12 при этом описан.

При считывании координат прямоугольников в области цифр с нуля до девяти (т.е. в области установки режимов), дешифратор 10 вырабатьшает на выходе 70. Этот сигнал разреш ет установку в положение 1 триггера 9, а в момент действия сигнала, на выходе 52 элемента И 4 разрешает работу элементов И 1ОО и 1О1 под воздействием сигналов на выходах 4О в 41 генератора 1. Сигнал с выхода 78 п ступает на вход коммутатора 13 для пропускания через него кода цифр с нуля до девяти и записи этого кода в оперативную память.

Работа распределителя 12 при считывании координат прямоугольников в любой области в случае установки триггера 9 в положение 1 отличается от описанной только тем, что в момент действия сигнала на вькоде 52 элемента И 4 сначала работают элементы И 102 и 103. При этом сигнал с выхода элемента И102 через элемент И 108 поступает в оперативную память для записи кода пробела, а сигнал с выхода элемента И ЮЗ через элемент ИЛИ 107 поступает на счет. ный вход счетчика оперативной памяти;

Таким образом, предлагаемое устройство позволяет записывать в любой массив ячеек оперативной памяти двоичнодесятичные коды чисел, соответствующих порядковым номерам прямоугольников координатного поля формирователя 2, за счет чего расширяется область применения устройства. Преимущество представления информации в двоично-десятичирм коде заключается в возм М4Ности быстрого изменения смысловых названий в прямоугольниках координатного поля с сокранением их порядковых номеров в десятичной форме.

Технико-экономическое преимущество предлагаемого устройства заключается в более широкой, по сравнению с извесьным, области его применения за счет выполнения записи двоично-десятичных чисел в оперативную память.

Фмг.г

Ф1лЗ

9

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для записи информации в оперативную память | 1974 |

|

SU482805A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1983-10-23—Публикация

1982-06-04—Подача