(54) АСССЦИАТИБНОЕ ЗАПОМИНАЮиШЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1980 |

|

SU926717A1 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU877617A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU310308A1 |

| Ассоциативное запоминающее уст-РОйСТВО C АВТОНОМНыМ КОНТРОлЕМ | 1978 |

|

SU813507A2 |

| Ассоциативное запоминающее устройство с автономным контролем | 1977 |

|

SU660092A1 |

| Ассоциативное запоминающее устройство | 1973 |

|

SU484562A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU533989A1 |

| Ассоциативное запоминающее устройство с самоконтролем | 1980 |

|

SU858105A1 |

| Ассоциативное оперативное запоминающее устройство | 1981 |

|

SU978197A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

t

Изобретение относится к запоминающим устройствам.

Известно ассоциативное запоминающеь устройство, содержащее регистр признака опроса, блок памяти ассоциативных признаков, индикаторы совпадения, блок памяти основной информации и регистр числа TI

Недостатком известного устройства является небольшой объем памяти при выполнении устройства в виде интегральной схемы.

Наиболее близким техническим решением к данному изобретению является ассоциативное запоминающее устройство, содержащее накопитель с ячейками памяти, соединенными с входным регисгром, регистром acки, дополнительным сдвигающим регистром, основным сдвигающим регистром, входы и выходы которого соештены с выходами и входами регистра СЛО6 регистра занятости, блока считывания мп пхзначного ответа, выходы допилиительно1о сдвигающего регист-

pa соединены со входами основного сдвигающего регистра 2 .

Недостатком этого устройства является невысокое быстродействие при операции поиска словофср)м в машинном словаре, так как требуется предварительная сортировка всех искомых словоформ.

Целью изобретения является повышение быстродействия устройства при поиске словоформ в машинном словаре.

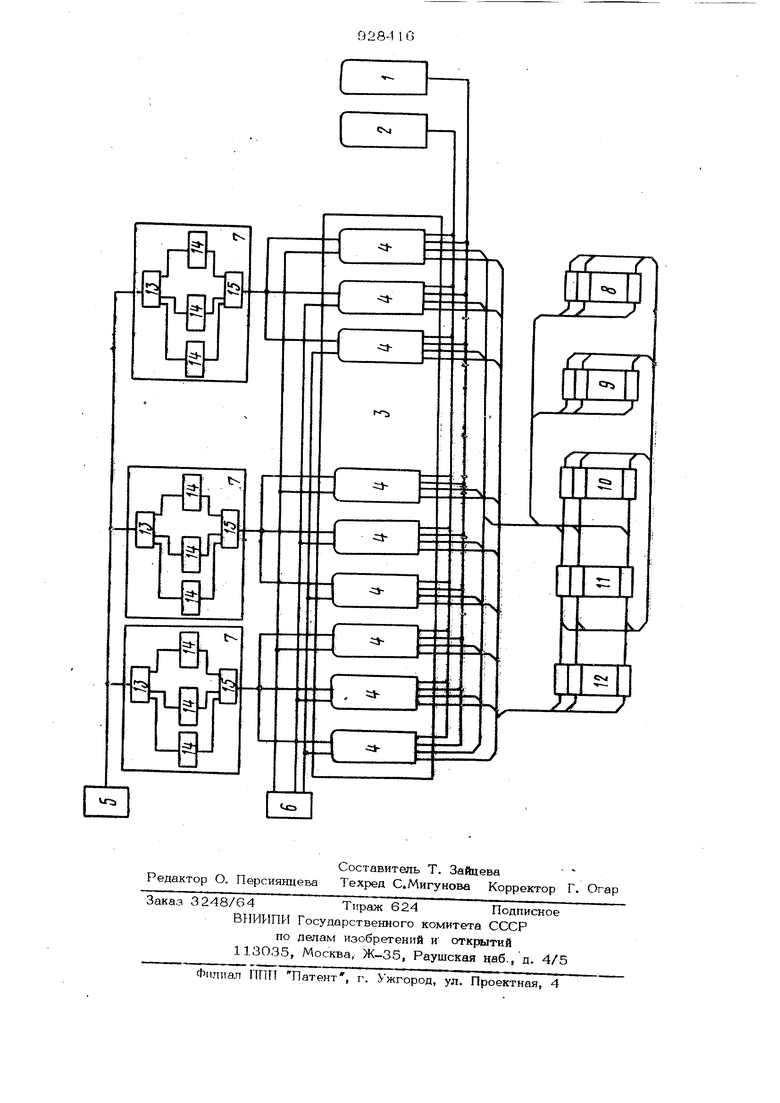

Поставленная цель достигается тем, что в асссщиативное запоминающее угтгройство, содержащее ретистр признака поиска, регистр маски, основной накопитель, основной и дополнительный регистры сдвига, регистр границ чисел, регистр кодов эавяггости и блок извлечения многозначного ответа причем одни из входов основного вакопнтвля подклкмены к выхо дам регистра признака поиска, регистра маски и основного регистра сдвига, а выходы - ко входам дополнительного регистра сдвига, выходы которого соединены со входами основного регистра сдвига, выходы и другие входы которого соответственно соединены со входами и выходами регистра границ чисел, регистра кодов занятости и блока извлечения многозначного ответа, введены регистр адреса, распределитель импульсов и дополнительные накопители, причем выход регистра адреса подключен ко входам дополнительных накопителей, выходы которых и выходы распределителя импульсов соединены с другими входами основного накопителя, выходы регистра адреса и распределителя импульсов являются адресными входами устройства. При этом каждый дополнительный на- копитель целесообразно выполнить содержашим дешифратор, регистры границ чисел и элемент ИЛИ, причем выходы дешифратора подключены ко входам регистров границ чисел, выходы которых соединены со входами элемента ИЛИ, вЫход которого является выходом дополнительного накопителя, входом которого являет ся вход дешифратора. На чертеже изображена структурная схема .предложенного устройства. 5стройство содержит регистр 1 признака поиска, регистр 2 маски, основной накопитель 3 с ячейками памяти 4, регистр 5 адреса, распределитель 6 импульсов, дополнительные накопители 7, блок 8 извлечения многозначйого ответа, регистр 9 кодов занятости, регистр 10 границ чисел, основной 11 и дополнитель ный 12 регистры сдвига. При этом каждый дополнительный накопитель выполнен содержащим дешифратор 13, регистры 14 чисел и элемент ИЛИ 15. Устройство работает следующим обравом. При поиске словоформ в машинном сло варе, причем словарь хранится в регистрах 14 накопителей 7, в регистр 1 сводится первое машинное слово обрабатываемой словоформы. На регистр 5 поступает адрес регистров 14, в которых хра нится соответствующая часть машинного словаря. Поступивший адрес деши 1рируется дешифраторами 13. Одна из выходных шин каждого дешифратора 13 возбуждает ся, и полученные импульсы передаются на адресные шины соответствующих регистров 14.. При этом происходит считывание хранящейся на данных регистрах 14 информации на входы соответствующих элементов ИЛИ 15. Одновременно с этим на распределитель 6 поступает импульс, который затем передается на шины записи соответствуюших ячеек памяти 4 накопителя 3. В следующий момент времени эти ячейки памяти 4 воспринимают информацию, поступающую с выходов соответствующих элементов ИЛИ 15 накопителей 7. Затем в регистр 5 вводится следующий адрес. Дешифраторы 13 в каждом накопителе 7 дешифрируют этот адрес и вь1бирают следующие регистры 14. На распределитель 6 подается второй импульс, который поступает на шины записи следующих ячеек памяти 4. При этом на эти ячейки памяти 4 переписывается информация, поступающая через элементы ИЛИ 15 от выбранных регистров 14. Таким же образом осуществляется заполнение остальных ячеек памяти 4 накопителя 3. После того как накопитель 3 заполнен, содержимое регистра 1О переписывается на основной регистр 11, В логических схемах ячеек памяти 4 далее осуществляется сравнение машинного слова, хранящегося в регистре 1, со всеми машинными словами, храшпдимися в ячейках памяти 4, отмеченными единичными разрядами основного регистра 11. Результаты сравнения поступают на дополнительный регистр 12. Далее в регистр 1 вводится следующее машинное слово словоформы. Содержимое основного регистра 11 и дополнительного регистра 12 сдвигается на один разряд. Выполняется аналогичное сравнение входного машинного слова с мащиннь1ми словами, хранящимися в отмеченных единичными разрядами основного регистра 11 ячейках памяти 4. Полученные результаты сравнения поступают на дополнительный регистр 12 для коррекции его содержимого. Эти действия выполняются до тех пор, пока не будет получен результат сравнения последнего машинного слова исходной словоформы. В этом случае содержимое основного регистра 11 корректируется содержимым дополнительного peirncrpa 12 и затем пересылается в блок 8, который осуществляет вывод из накопителя 3 номера исходной словоформы в машинном словаре. На этом процесс поиска по одной словоформе заканчивается. Поиск по другой словоформе выполняется таким же образом. Технико-экономическое преимущество предложенного устройства заключается в более высоком, по сравнению с известным устройством, быстродействии при поиске словоформы в машинном словаре.

Формула изобретения 5

н допопнительаые нахотггепн, выход регистра адреса подключен ко ЕКОдам дополнительных накопителей выходы которых и выходы распределителя импульсов соединены с другими входами основного накопителя, входы регистра адреса и распределителя импу7П сов являются адресными входами устройства.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-05-15—Публикация

1980-08-27—Подача