(54) АССОЦИАТИВНОЕ ЗАПОМИКАЮШЕЕ УСТРШСТВО

С САМОКОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1100638A1 |

| Ассоциативное запоминающее устройство | 1977 |

|

SU714500A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2037892C1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU555438A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| Устройство для извлечения многозначного ответа из ассоциативной памяти | 1985 |

|

SU1292039A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Устройство для считывания информации из ассоциативной памяти | 1981 |

|

SU955203A1 |

Изобретение относится к запоминающи устройствам. Известно ассоциативное запоминающее устройство, содержащее регистр данных, регистр маски, реверскв л 1й сдвигающий регвзтр, накопитель, блок очередности, регистр занятости, регистр исследуемых слов Ш Недостатком этого устройства являются большие аппаратурные затраты. Наиболее близким к предлагаемому техническим решением является ус-фойство, содержащее блок управления, три блока сложения по модулю два, коммутатор, два блока сравнения, ИЛ Недостатком этого устройства являетс снижение быстродействия вследствие необходимости выполнения последователь- ных процедур пословного считьтания и поразрядного поиска для контроля правильности хранения всего массива информации в ассо Аиативном накопителе. Цель изобретения - повышение быстродейстакя устройства. Поставленная цепь достигается тал, что в ассоциативное запоминающее устройство с самоконтролем, содержашее накопитель матркчното типа, каждый ассоциативный элемен памяти которого выполнен из запоминающего эп№гента, схемы сравнения и элемента И, блок обработки многозначного ответа, индикаторы ответа, схему поразрядного сравнения, дешифратор адреса, сумматор по модулю дза и блок управления, причем первые выходы запоминаюошх элеь1ентов подключены соответственно к первым входам схем Сравнения, выходы которых соединены со входами соответствующих элементсв И, первые входы запоминающих элементов каждой строки соединены шинами выборки с соответствующими выходами дешифратора адреса, вторые входы запоминающих элементов каждого столбца подключены соответстве1гао к одним их входов сумматора по модулю

два и входам записи устройства, а вторые выходы - к другим входам сумматора по модулю два и входам считывания устройства, второй вход одной из схем сравнения первой строки и первого столбца накопителя соединен с соответствующим входом поиска устройства, выходы индикаторов ответа подключены соответственно к одним из входов блока обработки многозначного.ответа, первый выход

которого соединен с одним из входов деши})ратора, другие входы которого являются адресными входами устройства, другой вход и второй выход блока обработки многозначного ответа подключены соответственно к первым выходу и входу блока управления, вторые выход и вход которого соединены соответственно с управляющим входом сумматора по модулю два и с выходом схемы сравнения, одни из входов которой подключены соответственно к выходам сумматора по модулю два, другие входы - ко входам элементов И последней строки накопителя а выходы являются выходами устройства, введены группы snsvfeHTce И-ИЛИ, причем выходы элементсш И-гИЛИ первой группы соединены соответственно со вторыми входами других схети сравнения первой строки и первого столбца накопителя,

первые входы одних из элементов И-ИЛИ первой группы подключены соответственно к выходам схем сравнения предыдущей строки первого столбца накопителя, а; первые входы других - соответственно

к выходам схем сравнения предыдущего столбца первой строки накопителя, выходы элементов Р1-ИЛИ второй группы соединены соответственно со вторыми входами схем сравнения вторых и всех последующих строк и столбце® накопителя, первые входы элементов И-ИЛИ второй группы каждой строки подключены соответст венно к выходам схем сравнения предыдущей строки того же столбца, вторые входы элементе И-ИЛИ второй группы каждого столбца соединены с выходами схем сравнения предыдущего столбца той же строки, вторые входы элементов И-.ИЛИ первой группы и третьи входы элементов И-ИЛИ второй группы каждого столбца накопителя подключены соответственно ко вxoдa I поиска устройства, пер вые входы элементов И-ИЛИ третьей групы подключены соответственно к выходам э-лементов И, вторые входы - к выходам схем сравнения последнего столбца накопителя, а выходы - ко индикаторов ответа, третьи входы

элементов И-ИЛИ первой и тоетьей групп и четвертые входы элементов И-ИЛР1 второй группы соединены с третьим выходом блока управления, а пятые входы элементов И-ИЛИ второй группы - с четвертым выходом блока управления.

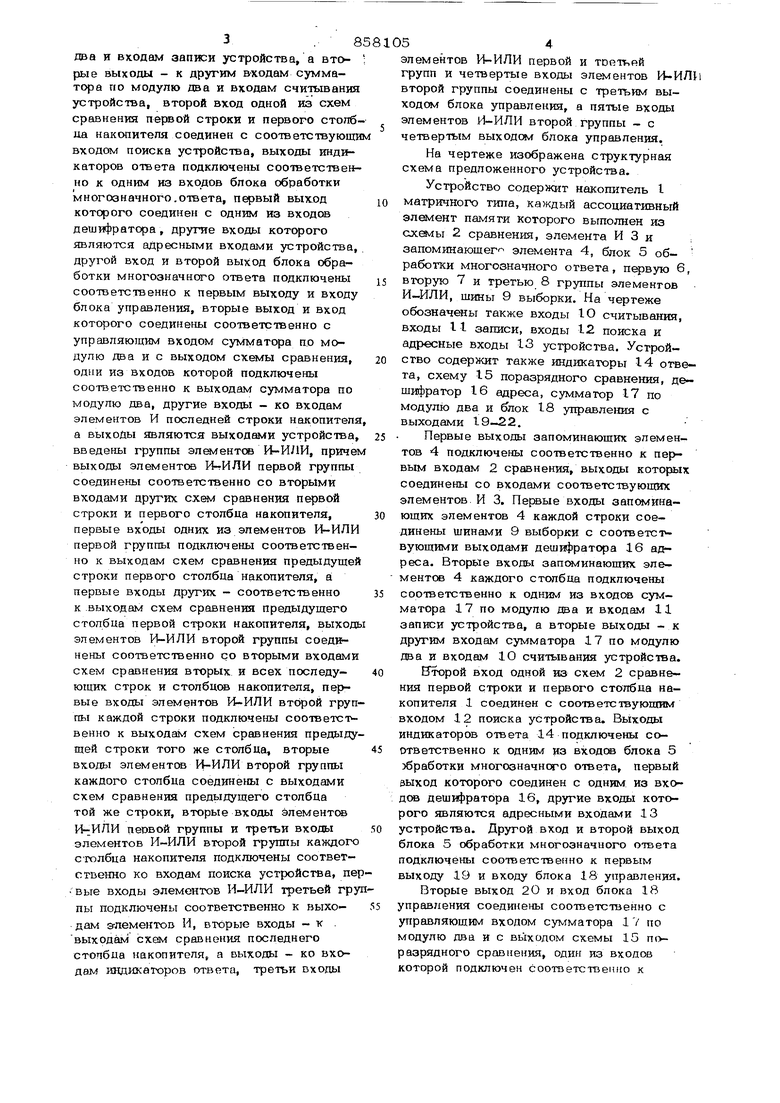

На чертеже изображена структурная схема предложенного устройства.

Устройство содержит накопитель I матричного типа, каждый ассоциативный элемент памяти которого выполнен из схемы 2 сравнения, элемента И 3 и запоминающего элемента 4, блок 5 обработки многозначного ответа, первую 6, вторую 7 и третью 8 группы элементов И-ИЛИ, щины 9 выборки. На чертеже обозначены также входы Ю считывания, входы 11 записи, входы 12 поиска и адресные входы 13 устройства. Устройство содержит также индикаторы 14 ответа, схему 15 поразрядного сравнения, дешифратор 16 адреса, сумматор 17 по модулю два и блок 18 утфавления с выходами 19-22.

Первые выходь запоминающих элементов 4 подключены соответственно к первым входам 2 сравнения, выходы которых соединены со входами соответствующих элементов И 3. Первые входы запсж инающих элементов 4 каждой строки соединены шинами 9 выборки с соответст вуюшими выходами дешифратора 16 адреса. Вторые входы запетлинаюших элементов 4 каждого столбца подключены соответственно к одним из входе® сумматора 17 по модулю два и входам 11 записи устройства, а вторые выходы - к другим входам сумматора 17 по модулю два и входам 10 считывания устройства.

Второй вход одной из схем 2 сравнения первой строки и первого столбца накопителя 1 соединен с соответствуюшшуг входом 12 поиска устройства. Выходы индикаторов ответа 14 подключены соответственно к одним из входев блока 5 збработки многозначного ответа, первый аыход которого соединен с одним из входсж дешифратора 16, другие входы которого являются адресными входами 13 устройства. Другой вход и второй выход блока 5 обработки многозначного ответа подключены соответственно к первым вьщоау 19 и входу блока 18 управления.

Вторые выход 2О и вход блока 18 управления соединены соответственно с управляющим входом сумматора 17 по модулю два и с выходом схемы 15 поразрядного сравнения, один из входов которой подключен соответственно к выходу сумматора 17 по модулю два, другие входы - ко входам элементов И 3 последней строки накопителя 1, а выходы являются выходами устройства. Выходы элементов 6 И-ИЛИ первой группь соединены соответственно со вторалми входами других схем 2 сравне ния первой строки и первого столбца накопителя 1. Первые входы одних из элементе®. 6 И-ИЛИ первой группы подключены соответственно к выходам схем 2 сравнения предыдущей строки первого столбца накопителя 1, а первые входы других - соответственно к выходам схем 2 сравнения предыдущего столбца первой строки накопителя 1, Выходы элементе 7 И-ИЛИ второй группы соединены соответственно со вторыми входами схем 2 сравнения вторых и всех последующих строк и столбце накопите ля 1. Первые входы элементов 7 И-ИЛИ второй группы каждой строки подключен соответственно к выходам схем L; срав ния предыдущей строки того же столбца BTOfAie входы элементов 7 И-ИЛИ втор группы каждого столбца соединены с выходами схем 2 сравнения предыдущег столбца той же. строки накопителя 1. В рые входы элементов 6 И-ИЛИ пе{шой группы и третьи входы элементов И-ИЛ второй группы каждого столбца накопителя 1 подключены соответственно ко входам 12 поиска устройства. Первые ВХОФ1 элементов 8 И-ИЛИ третьей группы подключены соответственно к вы дам элементе И 3, вторые входы - к выходам 2 сравнения последнего столбца накопителя 1, а выходы - ко входшъ индикаторов 14 ответа. Третьи входы элементе И-ИЛИ первой 6 и третьей 8 групп соединены с третьим 21 выходом блока 18 управления, а пятые входы элементов 7 И-ИЛИ второй группы - с четвертыми 22 выходам блока 18 управления. Устройство работает следующим образом. С-ц&лы 2 сравнения с помощью элементов И-ИЛИ первой 6 и второй 7 групп образуют последовательные цепи полусумматоров, которые обеспечивают получение сумм по модулю два информационного содержания слова (по строке или разряда (по столбцу) накопителя 1, иcпoльзyeмыx. контроля всех запоми нающих элементов 4. В процессе ассоциативного поиска схемы 2 сравнения выполняют операцию сложения по модулю два информации. запи санной в запсж(инаюпшх элй 1ентах 4, с информацией, подаваемой внешним устрсАством на входы 12 поиска. Слова, совпадающие с кодом псягска, выделяются элементами И.З, а факт совпадения запоминается индикатсфами 14 ответа. Перед начале работы инфе)рмационное содержание накопителя 1 сумматора 17 по модулю два предполагается нулевым. При записи в устройство некоторого числа по входам 11 записи в некоторый адрес, заданный внешним кодом адреса на адресных входах 13, предпола гается прецваригельное считывание информации по этому адресу на входы 10 считъшания посредством выборки слова дешифратором 16 адреса через шины 9 выборки из накопитетя 1. В процессе зап1к;и информации пителем 1 происходит вычисление поразрядной контрольной суммы информации всех слов, записываемых в накопитель 1 при помощи сумматора 17 по модулю два, для чего через его первые я вторые инфо{ лационные входы последе атепьно вводится сначала считываемая, а затем записьшаемая по некоторому адресу информация. При последовательной выборке информации в сумматоре 17 по модулю два накапливается значение разности по модулю два записываемой и считываемой инфсфмации и образуется необходимое значение контрешьной суммыГ При операции считьюания блок 18 управления запрещает суммирование инфс машга сумматоре 17 по модулю даа. Контреоть информации, записанной в накопитель 1 , может производиться горвзештальным Л1йо вертикальным суммнре анигал иа ормааяп по модулю два вдоль строки (слов) или столбце (разяде) матрицы накопителя 1 при наличия игналов логического О на входах 12 по1юка. При горизонтальнее суммировании от лока 18 управления подается сигнал логической на его третий выход О на его 21 и сигнал логического четвертый выход 22. Это обеспечивает подключение выода схем 2 срш1нения некоторой строки оответственно к первым входам схем 2 равнения, принадлежащих к той же

строке накопителя 1 через эпоменты И-ИЛИ первой 6 и второй 7 групп.

При этом выходы схем 2 сравнения последнего столбив накопителя 1 подключаются через эпементы 8 третьей группы ко входам 14 индикатороз ответа.

На выходах схем 2 сравнения последнего столбца накопителя 1 образуется значение-суммы по модулю два соотьетствующих слов, которое запоминается индикаторами 14 ответа. При наПИЧШ1 избыточных разрядов в каждом слове накопителя, дополняющих до (У значения суммы информационного содер;кан1Ш всех разрядов слова, в случае нечетного количества ощибок на выходе индикаторов 14 ответа устанавливается значение единима.

ESiioK 5 обработки многозначного

ответа анализирует состояние индикаторо 14 ответа и при наличии хотя бы одной eaiffla i на их выходах выдает сигнал в блок 18 управления,

Бпок 18 управления может инишшровать выборку из накопителя 1 неисправных слов с помощью блока обработки многозначного ответа и деши{)ратора 16 адреса для коррекции ошибки либо маскировать неисправные слова записью признака неисправности в служебные рзаряды .неисправных слов накопителя 1.

Дг;Я проведения вертикального суммирован11Я вдояь столбцов накопителя бло- ,;:ом 18 управления подается на третий выход 21 сигнал логического О, а на четвертый выход 22 - логической Ъ. Результаты суммирования сравниваются схемой 15 поразрядного сравнения с сос--то,янием соответствующих разрядов

су--Аыатора 1 7 по модулю isaa, содержашего контрольную cyMiviy.

При наличии хотя бы одного песовпаденкя в блок 18 управления подается ошибки с управляющего выхода скемы 15 поразрядного сравнения.

Неисправный разряд указьтается С1х:тоянием I на одном из выходов схемы 15 поразрядного сравнения,

При наличии информации о кратности ошибок, определяемых .блоком 5 обрабо-гки многозначного ответа и СХЙУГОЙ 15 поразрядного сравнения по результатам гор заонта7гьного или вертикального суммирования по модулю, два, передаваемых в блок 18 управления, возможна коррекция некоторых типов ошибки, например одиночной, при считиванил юти перезапи

неисправной информации в аапсминающ элементе с контролем процесса перезаписи, Технико - экономическое преимущество предложенного устройства заключается в его более высоком по сравнению с известным быстродействии за счет обеспечения непрерьтного контроля всего объема ассоциативного накопителя при записи, считывании и хранении информации.

Формула изо б ре

тения

Ассоциативное запоминающее устройство с самоконтролем, содержащее накопитель матричного типа, каждь й ассоциативный элемент памяти которого выполнен из запоминающего элемента, схемы сравнения и элемента И, блок обработки многозначного ответа, индикаторы ответа, схему поразрядного сравнения, дешифратор адреса, сумматор по модулю два и блок управления, причем первые выходы запоминающих элементов подключены соответственно к первым входам схем сравнения, выходы которых соединены со входами соответствующих элементе® И, первые входы запоминающих элементов каждой строки соединены шинами выборки с соотеетствуюшими выходами дешифратора адреса, вторые входы запоминающих элементов каждого столбца подключены соотьетс-гвенно к одним из входов сумматора по модулю два и входам записи устройства, а вторы выходы - к другтфл входам сумматора по модулю два и входам считывания устройства, второй вход одной из схем сравнения первой строки и первого столбца накопителя соединен с соответствующим входом поиска устройства, выходы индикаторов ответа подключены соответ ственно к одним из входов -блока обработки многозначного ответа, первый выход которого соединен с одн15м из входов дешифратора, другие входы которого 5тляются адресными входшу и устройства, другой вход и второй ВЫ7СОД блока обработки многозначного ответа подключены соответственно к первым выходу и входу блока управления, вторые выход и вход которого соединены соответственно с управляющими входом сумматора по модулю два и с выходами схемы поразрядного сравнения, один из входов которой подключены соответственно -к выхода сумматора по модулю два, другие входы ко входам элементов И последней строки накопителя, а выходы являются выходами устройства, отличаюшеася тем, что с целью повышения быстродействия устройства, оно содержит группы элеме тов ИгИЛИ, причзи( выходы элементов И-ИЛИ первой группы соединены соответ iCTBOHHo со вторыми входами прупк. схем сравненЕСя лервой строки к первого столбца накопита1Я, первые входы одних вз элементов И-ИЛИ первой группы подключены соответственно к вькодам схем сравнеиия предьщущей строки первохчэгстолбца накопителя, а первые входы других - соооветсовенно к выходам сх&л сравнения предыдущего столбца первЬй строки накопителя, выходы элементов И-ИЛИ второй группы соединены соответс1вшно со вторыми входами сх сравнения вторых и всех последуюпхих строк и столбцов накопителя, первые входы элементов И-ИЛИ второй группы каждой строки подключены cooiBeTCtseHно к выходам схем сравнения предыдуш строки того же столбда, вторые входы алемейтс И-ИЛИ второй группы кождого

столбца соединены с выходами сх срав нениа прзошхушего столбца той же стро ки« вторые входы элементов И-ИЛИ первой группы и третья входы элементов И-ИЛИ второй группы каждого стопбиа накопителя подключены соотве1С1венно ко входам поиска устройства, входы элементов И-ИЛИ третьей группы подключены соответственно к выходам эл&ментсв И, вторые входы - к выходам схем сравнения последнего столбца накопителя, а выходы - ко входам индикаторов ответа, третьи входы элементов И-ИЛ первой и третьей групп и четвертые входы элементов И-ИЛИ BTopt группы соепяявиы с третьим выходом блока управления, а пятые входы элементов И-ИЛЙ второй группы - с четвертым выходом блока управления.

Источники нв4 ормацша, принятые во внимание при экспертизе. 1. Авторское свидетельство СССР №618794, кл. Q 11 С 15/ОО, 1977.

Авторы

Даты

1981-08-23—Публикация

1980-01-04—Подача