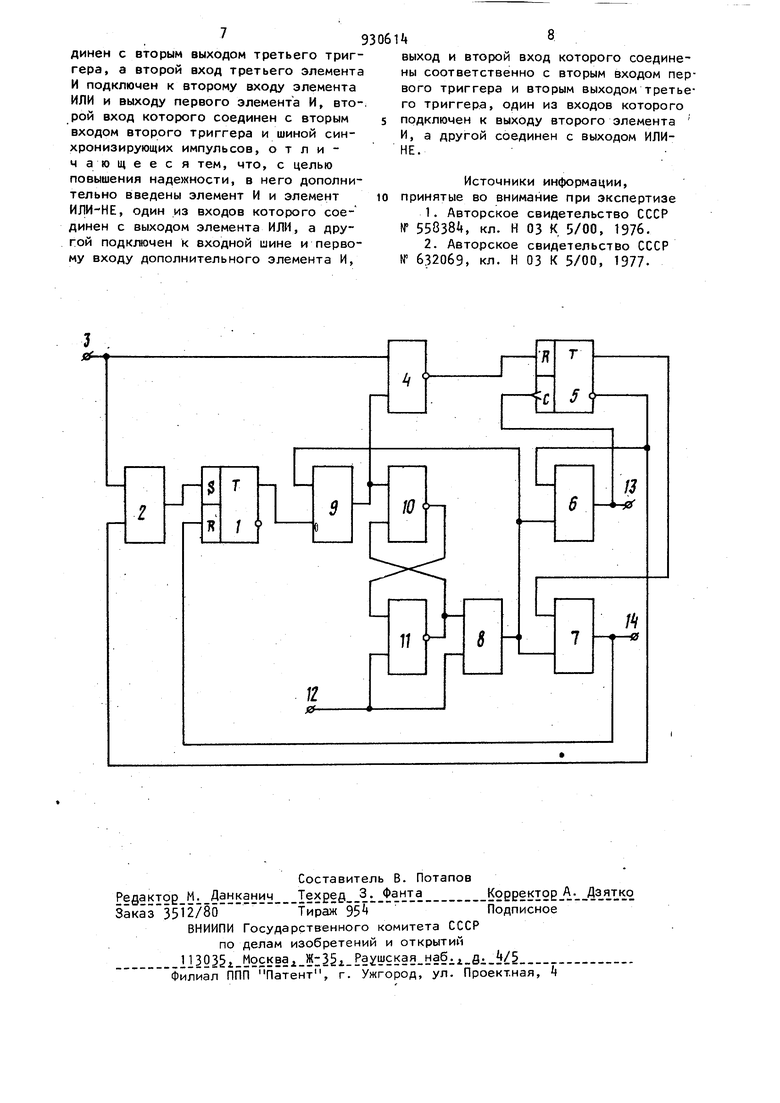

Изобретение относится к импульсно технике и может быть использовано дл временной привязки импульсов в устройствах автоматики и вычислительной техникиi осуществляющих обмен информацией асинхронно. Известно устройство для синхронизации импульсов, которое содержит входной триггер, элемент ИЛИ, триггер, построенный на элементах И-НЕ, два элемента И и счетный триггер И. Известное устройство позволяет формировать сдвинутые во времени парные синхронизированные импульсы LljНедостаток устройства заключается в том, что оно может формировать ложные импульсы в случае, если длительность входного асинхронного i iпульса превышает длительность синхро низирующего импульса.Это обусловлено тем, что по окончании второго синхро низированного импульса устройство возвращается в исходное состояние, т.е. на выходе входного и счетного триггеров устанавливается потенциал О, но присутствующий на входе устройства, а также на установочном вхоДе счетного триггера, синхронизируеМый импульс снова переключает входной триггер, устанавливая на его выходе потенциал 1. Это дает возможность устройству независимо от числа поступивших на счетный вход счетного триггера синхронизированных импульсов формирователь ложные импульсы по мере поступления синхронизирующих импульсов в течение всего времени присутствия входного асинхронного импульса на входе устройства. Наиболее близким по технической сущности к изобретению является устройство, соде| кащее входной триггер, элемент ИЛИ, триггер, выполненный на элементах И-НЕ, три элемента И и триггер со счетным входом 2. В данном устройстве также на выходы может поступать не по одному, а по несколько импульсов в случае. 39 если длительность синхронизируемых импульсов будет превьниать длительность синхронизирующих импульсов. Это связано с тем, что по окончании второго синхронизированного импульса устройство возвращается в исходное состояние, т.е. на выходе входного и счетного триггеров устанавливается потенциал О, не присутствую щий на входе устройства, а также на установочном входе счетного триггера синхронизируемый импульс снова переключает входной триггер, устанавли вая на его выходе потенциал 1. Это дает возможность устройству независимо от числа поступивших на счетный вход счетного триггера синхронизирог ванных импульсов формировать ложные импульсы по мере поступления синхронизирующих импульсов в течение всего времени присутствия входного асинхро ного импульса на входе устройства. Цель изобретения - повышение наде ности за счет формирования синхронизированных выходных импульсов при лю бой длительности входных асинхронных импульсов. Эта цель достигается тем, что в устройство для синхронизации импульсов, содержащее входную шину и после довательно соединенные первый триггер, элемент ИЛИ, второй триггер, вы полненный на элементах И-НЕ, первый элемент И, второй элемент И и первую выходную шину, а также последователь но соединенные третий триггер, тре- . тий элемент И и вторую выходную шину подключенную также к одному из входов первого триггера, при этом второй вход второго элемента И соединен со вторым выходом третьего триггера, а второй вход третьего элемента И подключен ко второму входу элемента ИЛИ и выходу первого элемента И, второй вход которого соединен со вторым вхо дом второго триггера и шиной синхронизирующих импульсов, дополнительно введены элемент И и элемент ИЛИ-НЕ, один из входов которого соединен с выходом элемента ИЛИ, а другой подключен к входной шине и первому входу дополнительного элемента И, выход и второй вход которого соединены соответственно, с вторым входом первого триггера и вторым выходом третье го триггера, один из входов которого подключен к выходу второго элемента И, а другой соединен с в-ыходом элемента ИЛИ-НЕ. li-4 На чертеже приведена функциональная схема устройства а Устройство для синхронизации импульсов содержит первый триггер 1, дополнительный элемент И 2, входную шину 3 элемент ИЛИ-НЕ Ц, третий триггер 5, второй элемент И 6, третий элемент И 7, первый элемент И 8, зле мент И 8, элемент ИЛИ 9, второй триггер, выполненный на элементах И-НЕ 10 и 11, шину 12 синхронизирующих импульсов, выходные шины 13 и 14. Единичный вход триггера 1 подключен к выходу элемента И 2, первый вход которого соединен с входной ши-ной 3 входных импульсов и одним из входов элемента ИЛИ-НЕ k, нулевой вход триггера 1 подключен к выходной шине 14 устройства и выходу элемента И 7, а выход триггера 1 соединен с первым входом элемента ИЛИ 9, второй вход которого соединен с одними из входов элементов И 6 и 7 и выходом элемента И 8. Первый вход триггера, выполненного на элементах И-НЕ 10 и 11 подключен к выходу элемента ИЛИ 9 и соединен с другим входом элемента ИЛИ-НЕ 4, второй вход этого триггера соединен с шиной 12 синхронизирующих импульсов и вторым входом элемента И 8, первый вход которого подключен к выходу элемента И-НЕ 11 и второму входу элемента И-НЕ 10, выход которого соединен с вторым входом элемента И-НЕ 11. Счетный вход триггера 5 подключен к выходной шине 13 устройства и выходу элемента И 6, а установочный вход - к выходу элемента ИЛИ-НЕ 4, единичный выход триггера 5 соединен с первым входом элемента И 7; а нулевой - с вторым входом элемента И 6 и вторым входом элемента И 2. Устройство работает следующим образом. В исходном состоянии триггеры 1 и 5 находятся в нулевом состоянии. Нулевой потенциал с единичного выхода триггера 1 поступает на первый вход элемента ИЛИ Э- Единичный потенциал с нулевого выхода счетного триггера 5 поступает на второй вход элемента И 6 и второй вход элемента И 2, а нулевой потенциал с единичного выхода - на первый вход элемента И 7Входные асинхронные импульсы поступают с шины 3 через элемент И 2 на единичный вход триггера 1 и переводят его в единичное состояние. Потенциал 1 с единичного выхода триггера 1 через элемент ИЛИ 9 поступает на первый вход элемента И-НЕ 10. При отсутствии синхронизирующего импульса на шине 12 на выходе элемента И-НЕ 11 присутствует потенциал 1,который поступает на второй вход эле-, мейта 1 -НЕ 10 и первый вход элемента И 8. В этом случае на выходе элемента И-НЕ 10 устанавливается потенциал логического нуля, который запирает по первому входу элемент И-НЕ 11, на выходе которого устанавливается потенциал 1 независимо от уровня потенциала на его втором входе, т.е. на шине 12 устройства. Потенциал логической единицы на выходе элемента И-НЕ 11 поступает на второй вход элемента И-НЕ 10 и первый вход эле мента И 8. Поступающий затем на шину 12 первый синхронизирующий импульс через открытые элементы И 8 и И 6 проходит на первую в 1ходную шину . 13 устройства и счетный вход триггера 5 ас выхода элемента И 8 проходит также на первый вход элемента И-НЕ 10 через элемент ИЛИ 9. По окон чании первого синхронизирующего импульса на выходе элемента И 8 и на шине 13 появляется потенциал О, а на единичном выходе триггера 5 устанавливается потенциал 1, поступающий на первый вход элемента И 7. С .нулевого выхода триггера 5 потенциал О поступает на второй вход элемента И 6, запрещая повторную выдачу оч редного импульса на шину 13, на второй вход, элемента И 2, запрещая повторное срабатывание триггера 1 после выдачи второго импульса.

Поступающий затем на шину 12 вто-, рой синхронизирующий импульс через открытые элементы И 8 и И 7 проходит на вторую выходную шину 1 устройств и нулевой вход триггера 1, а с выход элемента И 8 через элемент ИЛИ 9 на первый вход элемента И-НЕ 10 и один из входов элемента ИЛИ-НЕ 4. В этом случае триггер 1 установится в исходное нулевое состояние и с выхода этого триггера потенциал О поступит на первый вход элемента ИЛИ 9 на еыходе которого будет присутствовать потенциал 1 по второму входу в течение действия синхронизирующего импульса. X

По окончании второго синхронизирующего импульса на выходе элемента И 8 и шине появится потенциал О

306U6

который также установится на выходе элемента ИЛИ 9При поступлении на шину 12 третье го и последующих синхронизирующих 5 импульсов на выходе элемента И 8 и шинах 13 и 1 выходные импульсы не появятся. После выдачи второго синхронизированного импульса триггер 5 останется в единичном состоянии и

10 будет находиться в этом состоянии до тех пор, пока будет присутствовать входной импульс на шине 3- После снятия входного импульса и выдачи двух синхронизированных импульсов

15 на выходе элемента ИЛИ-НЕ k появится потенциал 1, устанавливающий триггер 5 в исходное состояние. В этом случае с нулевого выхода триггера 5 , потенциал 1 поступает на второй

20 вход элемента И 2 и разрешает новому входному импульсу пройти через элемент И 2 на единичный вход триггера 1 для формирования очередной пары синхронизированных импульсов.

25 Данное устройство некритично к длительности входного импульса. Это следует из того, что после выдачи выходных импульсов, когда входной импульс еще не окончен, счетный триг3Q гер 5 может установиться в исходное

нулевое состояние только тогда, ког, да на его установочный вход поступит высокий уровень с выхода элемента ИЛИ-НЕ 4, т.е. на его входах должны присутствовать потенциалы О, что

35 невозможно только после окончания входного импульса и выдачи выходных импульсов. Таким образом, данное уст-. ройство стабильно формирует два синхронизированных импульса независимо

40 от длительности входного асинхронного импульса, что повышает надежность устройства.

45

Формула изобретения

Устройство для синхронизации импульсов, содержащее входную шину .и последовательно соединенные первый

триггер,элемент ИЛИ, второй триггер,выполненный на элементах И-НЕ, первый элемент И, второй элемент И и .первую выходную шину, а также последовательно соединенные третий триггер, третий элемент И и вторую выходную шину, подключенную также к одному из входов первого триггера, при этом второй вход второго элемента И

динен с вторым выходом третьего триггера, а второй вход третьего элемента И подключен к второму входу элемента ИЛИ и выходу первого элемента И, второй вход которого соединен с вторым входом второго триггера и шиной синхронизирующих импульсов, отличающееся тем, что, с целью повышения надежности, в него дополнительно введены элемент И и элемент ИЛИ-НЕ, один из входов которого соединен с выходом элемента ИЛИ, а другой подключен к входной шине и первому входу дополнительного элемента И,

k

выход и второй вход которого соединены соответственно с вторым входом первого триггера и вторым выходом третьего триггера, один из входов которого подключен к выходу второго элемента И, а другой соединен с выходом ИЛИНЕ.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 55838it, кл. Н 03 К 5/00, 1976,

2.Авторское свидетельство СССР № 632069, кл. Н 03 К 5/00, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации импульсов | 1981 |

|

SU961125A1 |

| Устройство для синхронизации импульсов | 1978 |

|

SU744947A1 |

| Формирователь импульсов,синхронизированных тактовой частотой | 1984 |

|

SU1187255A1 |

| Формирователь одиночных импульсов, синхронизированных тактовой частотой | 1978 |

|

SU746887A1 |

| Формирователь одиночных импульсов | 1980 |

|

SU945968A1 |

| Устройство для синхронизации импульсов | 1978 |

|

SU741440A1 |

| Формирователь импульсов | 1981 |

|

SU1045371A1 |

| Селектор импульсов | 1987 |

|

SU1522390A1 |

| Устройство для обнаружения импульсных кодовых комбинаций | 1986 |

|

SU1406756A1 |

| Формирователь одиночных импульсов,синхронизированных тактовой частотой | 1979 |

|

SU864529A2 |

J efJ

Авторы

Даты

1982-05-23—Публикация

1980-03-19—Подача