(21)4162173/24-21

(22)18.12.86

(46) 30.06.88. Бюл. № 24 (72) С.В.Смирнов

(53)621.373 (088.8)

(56)Авторское свидетельство СССР № 813747, кл, Н 03 К 5/19, 1979.

Авторское свидетельство СССР № 1353313, кл. Н 03 К 5/19, 1986.

(54)УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ИМ- ПУЛЬСНЬК КОДОВЫХ КОМБИНАЦИЙ

(57)Изобретение может быть использовано в приемных устройствах систем обмена дискретной информацией, подверженных воздействию импульсных помех. Устройство для обнаружения импульсных кодовых комбинаций содержит регистр 1 сдвига, счетчики 2-4 импульсов, триггеры 6, 7, 15-17, элементы 5, 20, 21 сравнения, элементы И 10-12, 18, 19, элементы ИЛИ 8, 9, инвертор 13, блок 14 выдачи кодов, содержащий шесть источников кода и три коммутатора, входную шину 22, шину 23 тактовой частоты, установочные входы 24, вход 23 начальной установки и выходную шину 26. Устройство имеет расширенный диапазон обнаружи- ваем1,1Х импульсных кодовых комбинаций, I 3.п. ф-лы, 2 ЦП.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Частотный дискриминатор | 1984 |

|

SU1211868A1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Устройство для формирования одиночных импульсов | 1990 |

|

SU1758856A1 |

| Многоканальное устройство для подключения абонентов к общему ресурсу | 1990 |

|

SU1837307A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| Система экстремального регулирования | 1985 |

|

SU1352452A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| Устройство для регистрации информации | 1989 |

|

SU1603412A1 |

СО

Од

СП

Фиг.}

Изобретение относится к импульсно технике и может быть использовано в приемных устройствах систем обмена дискретной информацией, подверженных воздействию импульсных помех.

Цель изобретения - расширение диапазона обнаруживаемых импульсных кодовых комбинаций.

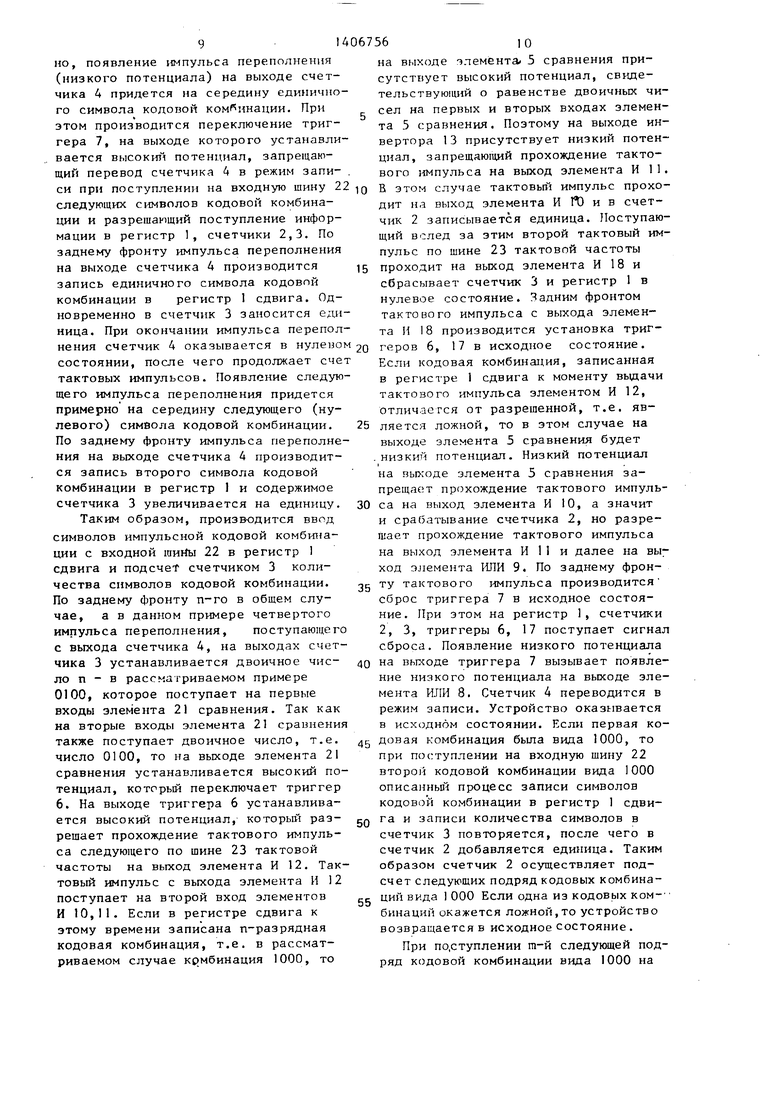

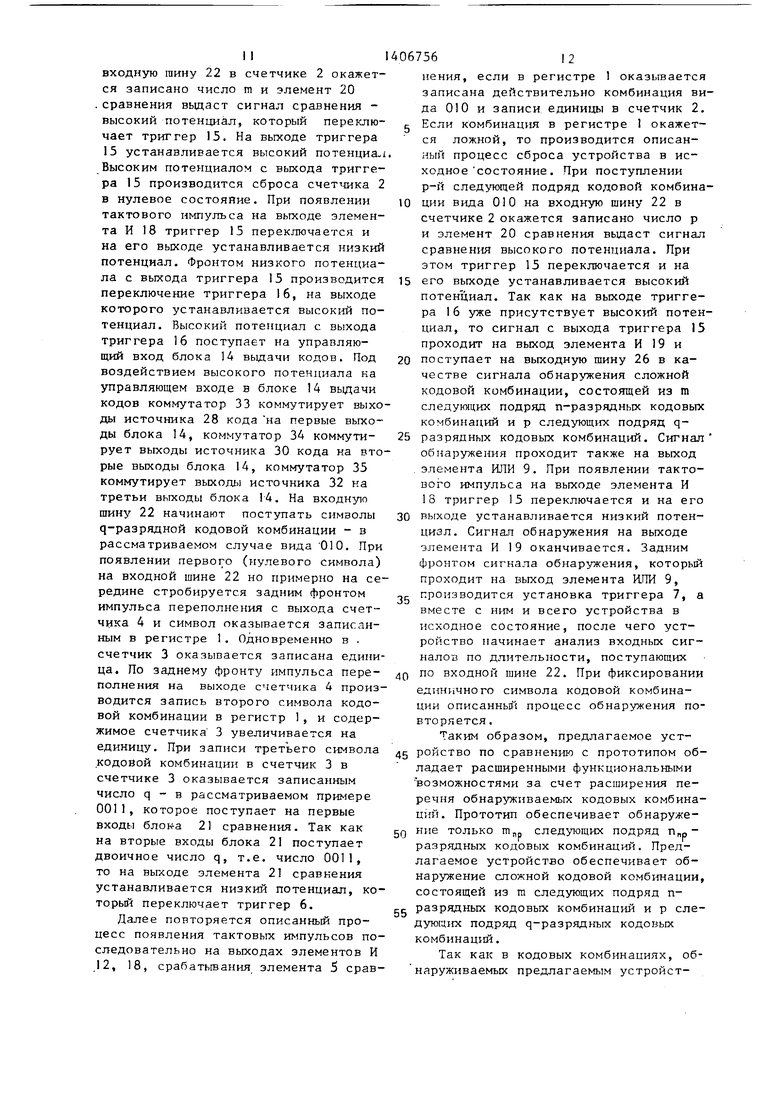

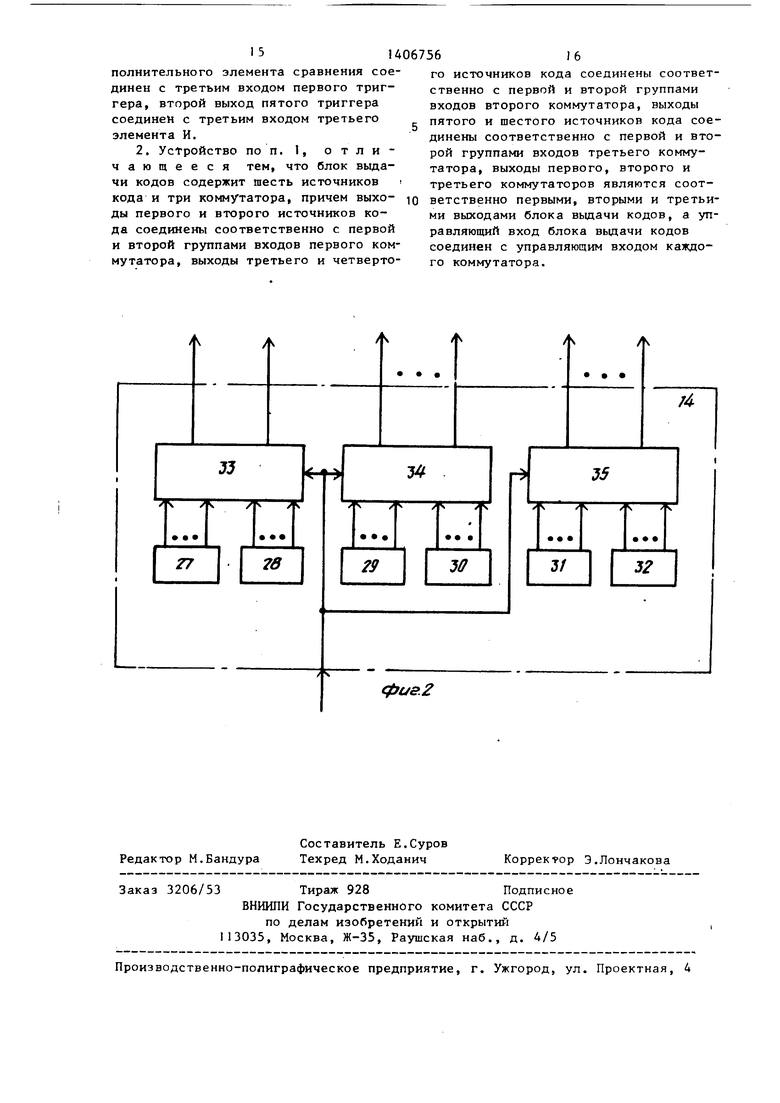

На фиг.1 показана структурная злектрическая схема предлагаемого устройства; на фиг.2 - структурная злектрическая схема блока выдачи кодов (вариант выполнения).

Устройство для обнаружения им- пульсных кодовых комбинаций содержит регистр 1 сдвига, первый счетчик 2 импульсов, второй счетчик 3 импульсов, третий счетчик 4 импульсов, элемент 5 сравнения, первый триггер 6, второй триггер 7, первый элемент ИЛИ 8, второй элемент ИЛИ 9, первый элемент И 10, второй элемент И 11, третий элемент И 12, инвертор 13, блок 14 выдачи кодов, третий триггер 15, четвертый триггер 16, пятый триггер 17, четвертый элемент И 18, пятый элемент И 19, первый дополнительный элемент 20 сравнения, второй дополниПервый вход второго триггера 7 со динен с выходом второго элемента 9. Первый вход элемента ИЛИ 9 сое нен с выходом второго элемента И а второй вход - с выходной шиной Второй вход второго триггера 7 со динен с тактовым входом регистра сдвига, со счетным входом второго счетчика 3 импульсов и с выходом тьего счетчика 4 импульсов. Ин(Ьор ционные входы третьего счетчика 4 пульсов подключены к установочным входам 24 устройства. Первые вход элемента 5 сравнения соединены с ходами регистра 1 сдвига. Вход 25 чальной установки-устройства соед с третьим входом второго триггера Первые выходы блока 14 выдачи код соединены с первыми входами перво дополнительного элемента 20 сравн ния. Вторые входы блока 14 выдачи дов соединены с вторыми входами эл мента 5 сравнения. Выходы первого счетчика 2 импульсов соединены с в рыми входами первого дополнительно элемента 20 сравнения. Выход перв дополнительного элемента 20 сравн соединен с первым входом третьего

тельный элемент 21 сравнения, входную 30 триггера 15. Второй вход третьего

шину 22, шину 23 тактовой частоты,. установочные входы 24 устройства-, вход 25 начальной установки, выходную I шину 26.

Блок 14 выдачи кодов (фиг.2) со- 35 держит, например, источники 27-32 кода и коммутаторы 33-35.

Выход первого элемента И 10 соединен со счетным входом первого счетчика 2 импульсов. Выход элемента 5 40 сравнения соединен с первым входом первого элемента И 10 и через инвертор 13 - с первым входом второго элемента И 11, второй вход которого соетриггера 15 соединен с вторуым вход первого элемента ИПИ 8, с первым дом четвертого триггера 16, с пер входом сброса второго счетчика 3 пульсов, с первым входом сброса р гистра 1 сдвига, с первым входом п того триггера 17 и с первым входо первого триггера 6. Второй вход пе вого триггера 6 соединен с вторым входом сброса второго счетчика 3 и пульсов, с вторым входом сброса ре гистра 1 сдвига, с третьим входом третьего триггера 15, с выходом че вертого элемента И 18 и с вторым в

динен с вторым входом первого элемен-дз Д пятого триггера 17. Первый вход

та И 10 и с выходом третьего элемента И 12. Выход первого триггера 6 соединен с первым входом третьего элемента И 12, второй вход которого подключен к шине 23 тактовой частоты и к счетному входу счетчика 4 импульсов. Вход записи третьего счетчика 4 соединен с выходом первого элемента ИЛИ 8. Первый вход первого элемента ИПИ 8 подключен к входной шине 22 и к информационному входу регистра 1 сдвига, а второй вход - к первому входу сброса первого счетчика 2 импульсов и выходу второго триггера 7.

Первый вход второго триггера 7 соединен с выходом второго элемента ИЛИ 9. Первый вход элемента ИЛИ 9 соединен с выходом второго элемента И 11, а второй вход - с выходной шиной 26. Второй вход второго триггера 7 соединен с тактовым входом регистра 1 сдвига, со счетным входом второго счетчика 3 импульсов и с выходом третьего счетчика 4 импульсов. Ин(Ьорма- ционные входы третьего счетчика 4 импульсов подключены к установочным входам 24 устройства. Первые входы элемента 5 сравнения соединены с выходами регистра 1 сдвига. Вход 25 начальной установки-устройства соединен с третьим входом второго триггера 7. Первые выходы блока 14 выдачи кодов соединены с первыми входами первого дополнительного элемента 20 сравнения. Вторые входы блока 14 выдачи кодов соединены с вторыми входами элемента 5 сравнения. Выходы первого счетчика 2 импульсов соединены с вторыми входами первого дополнительного элемента 20 сравнения. Выход первого дополнительного элемента 20 сравнения соединен с первым входом третьего

триггера 15. Второй вход третьего

триггера 15 соединен с вторуым входом первого элемента ИПИ 8, с первым входом четвертого триггера 16, с первым входом сброса второго счетчика 3 импульсов, с первым входом сброса регистра 1 сдвига, с первым входом пятого триггера 17 и с первым входом первого триггера 6. Второй вход первого триггера 6 соединен с вторым входом сброса второго счетчика 3 импульсов, с вторым входом сброса регистра 1 сдвига, с третьим входом третьего триггера 15, с выходом четвертого элемента И 18 и с вторым вхотого

четвертого элемента И 18 подключен к шине 23 тактовой частоты. Второй вход четвертого элемента И 18 соединен с первым выходом пятого триггера 17. Третий вход пятого триггера 17 соединен с выходом третьего элемента И 12. Выход третьего триггера 15 соединен с вторым входом сброса первого счетчика 2 импульсов, с первым входом пяэлемента И 19 и соединен с вторым входом четвертого триггера 16. Выход четвертого триггера 16 соединен с вт(5рым входом пятого элемента И 19 и с управляющим входом блока 14

10

15

20

25

вьщачи кодов. Выход пятого элемента И 1 9 подключен к выходной шине 26. Выходы второго счетчика 3 импульсов соединены с первыми входами второго дополнительного элемента 21 сравнения. Вторые входы второго дополнительного элемента 21 сравнения соединены с третьими выходами блока 14 выдачи кодов, выход второго дополнительного элемента 21 сравнения соединен с третьим входом первого триггера 6. Второй выход пятого триггера 17 соединен с третьим входом третьего элемента И 18.

В блоке 14 выдачи кодов выходы первого и второго источников 27 и 28 кода соединены соответственно с первой и второй группами входов первого коммутатора 33. Выходы третьего и четвертого источников 29 и 30 кода соединены соответственно с первой и второй группами входов второго коммутатора 34. Выходы пятого и шестого источников 31 и 32 кода соединены соответственно с первой и второй ; группами входов третьего коммутатора 35. Выходы первого, второго и третьего коммутаторов 33, 34 и 35 являются соответственно первыми, вторыми и третьими выходами блока i4 выдачи КОДОВ,а управляющий вход блока 14 выдачи кодов соединен с управляющим входом каждого коммутатора 33-35.

Регистр 1 сдвига может быть выпол- 35 иен по схеме сдвигающего регистра, содержащей синхронные триггеры, например 133 ТМ2. В указанную схему сдвигающего регистра дополнительно вводятся элемент ИЛИ-НЕ и инвертор. Вход D1 схемы является информационным входом регистра 1. Тактовый вход регистра 1 соединен с входом С1 схемы. Выход дополнительно введенного элемента ИПИ-НЕ соединен с входом R схемы. Первый вход дополнительно введенного элемента ИПИ-НЕ является вторым входом сброса регистра 1. Первый вход сброса регистра 1 через доинверторе, причем ныход

. микросхе мы может быть соединен с нходом Г,2 микросхемы, так что счетчик являе ся четырехразрядным. Счетный вход счетчика 2 соединен с входом С1 ми росхемы 133ИЕ5. Вход инвертора соед нен с первым входом сброса счетчика 2, а выход инвертора - с первым вхо дом элемента ИЛИ, второй вход котор го является вторым входом сброса счетчика 2. Выход элемента ИЛИ соед нен с входами сброса RO(1) и R0(2) микросхемы 133ИЕ5. Выходы мик росхемы 1ЗЗИЕ5 являются выходами счетчика 2.

Счетчик 3 импульсов является дво ичным счетчиком и выполнен, наприме на микросхеме 133ИЕ5, элементе ИЛИ и двух инверторах, причем выход Q, микросхемы может быть соединен с вх дом С2 микросхемы, так что счетчик является четырехразрядным. Счетный вход счетчика 3 через первый инвертор соединен с входом С1 микросхемы 133ИЕ5. Первый вход сброса счетчика 3 через второй инвертор соединен с первым входом элемента ИЛИ, второй вход которого является вторым входо сброса счетчика 3. Выход элемента ИЛИ соединен с входами сброса R0(l) и R0(2) микросхемы 133ИЕ5. Выходы микросхемы 1ЗЗИЕЗлявляются вы ходами счетчика 3.

Счетчик 4 импульсов является сче чиком импульсов с возможностью параллельного ввода информации. Счетчик 4 может быть построен на микросхемах 133ИЕ7, например на двух, яв 40 ляющихся четырехразрядными двоичным синхронными счетчиками с возможностью параллельного ввода информации, и инверторе. Счетный вход €1 первой микросхемы 133ИЕ7 через инвертор со динен со счетным входом счетчика 4. Выход переноса Р1 первой микросхемы 1ЗЗИЕ7 соединен со счетным входом С второй микросхемы 133ИЕ7. Выход пер носа Р1 второй микросхемы 133ИЕ7 я

30

45

полнительно введенный инвертор соеди- 50 ляется выходом счетчика 4. Выходы

сброса первой и второй микросхем 133ИЕ7 объединены. Операция счета реализуется при наличии низкого пои55

нен с вторым входом дополнительно введенного элемента ИЛИ-НЕ. Выходы Q,-Q4 схемы являются выходами регистра I . На вход С2 схемы постоянно подан низкий потенциал.

тенциапа на входе сброса и высокого потенциала на входе разрешения записи V микросхем 133ИЕ7. Информационные входы D1, D2, D4, D8 микросхем 133ИЕ7 являются первыми входами счетчика 4. Входы разрешения записи

I

Счетчик 2 импульсов является двоичным счетч)1ком и выполнен, например, на микросхеме 133Ж5, элементе ИЛИ и

10

15

20

25

. 3506756

инверторе, причем ныход

. микросхемы может быть соединен с нходом Г,2 микросхемы, так что счетчик является четырехразрядным. Счетный вход счетчика 2 соединен с входом С1 микросхемы 133ИЕ5. Вход инвертора соединен с первым входом сброса счетчика 2, а выход инвертора - с первым входом элемента ИЛИ, второй вход которого является вторым входом сброса счетчика 2. Выход элемента ИЛИ соединен с входами сброса RO(1) и R0(2) микросхемы 133ИЕ5. Выходы микросхемы 1ЗЗИЕ5 являются выходами счетчика 2.

Счетчик 3 импульсов является двоичным счетчиком и выполнен, например, на микросхеме 133ИЕ5, элементе ИЛИ и двух инверторах, причем выход Q, микросхемы может быть соединен с входом С2 микросхемы, так что счетчик является четырехразрядным. Счетный вход счетчика 3 через первый инвертор соединен с входом С1 микросхемы 133ИЕ5. Первый вход сброса счетчика 3 через второй инвертор соединен с первым входом элемента ИЛИ, второй вход которого является вторым входом сброса счетчика 3. Выход элемента ИЛИ соединен с входами сброса R0(l) и R0(2) микросхемы 133ИЕ5. Выходы микросхемы 1ЗЗИЕЗлявляются выходами счетчика 3.

Счетчик 4 импульсов является счетчиком импульсов с возможностью параллельного ввода информации. Счетчик 4 может быть построен на микросхемах 133ИЕ7, например на двух, яв- 40 ляющихся четырехразрядными двоичными синхронными счетчиками с возможностью параллельного ввода информации, и инверторе. Счетный вход €1 первой микросхемы 133ИЕ7 через инвертор соединен со счетным входом счетчика 4. Выход переноса Р1 первой микросхемы 1ЗЗИЕ7 соединен со счетным входом С1 второй микросхемы 133ИЕ7. Выход переноса Р1 второй микросхемы 133ИЕ7 яв30

45

и

тенциапа на входе сброса и высокого потенциала на входе разрешения записи V микросхем 133ИЕ7. Информационные входы D1, D2, D4, D8 микросхем 133ИЕ7 являются первыми входами счетчика 4. Входы разрешения записи

V микросхем 1ЗЗИЕ7 объединены и соединены с входом записи счетчика А. Изменение состояния микросхем 133ИЕ7 происходит по фронту счетного импульса.

Элемент 5 сравнения обеспечивает выдачу выходного сигнала (высокого потенциала) при равенстве кодовых комбинаций, поступающих на первые и вторые входы элемента 5 сравнения. Элемент 5 сравнения выполнен, например, по схеме, содержащей инверторы, элементы И-ИЛИ-НЕ и элемент И.

Триггер 6 является синхронным триггером и построен, например, на D-триггере микросхемы 133ТМ2, элементе И и инверторе. Первый вход триггера 6 соединен с первым входом элемента И.Второй вход триггера 6 соединен через инвертор с вторым входом элемента И, выход которого соединен с R-входом D-триггера микросхемы 1ЗЗТМ2. Сйнхровход С D-триггера микросхемы 133ТМ2 соединен с третьим входом триггера 6. Выход QD-триггера микросхемы 133ТМ2 соединен с выходом триггера 6. На S и D-входы D-триггера микросхемы постоянно подан высокий потенциал.

Триггер 7 является синхронным триггером и построен, например, на D-триггере микросхемы 133ТМ2 и двух инверторах. Вход первого инвертора является первым входом триггера 7, а вькод первого инвертора соединен с синхровходом CD-триггера микросхемы 133ТМ2. R-вход D-триггера микросхемы 133ТМ2 является вторым входом триггера 7. Вход второго инвертора является третьим входом триггера 7, а выход второго инвертора соединен с S входом В-триггера 133ТМ2. Инверсньй выход Q D-триггера микросхемы 133ТМ2 является выходом триггера 7.

Триггер 15 является синхронным триггером и построен, например, на D-триггере микросхемы 133ТМ2, инверторе и элементе И. Первый вход триггера 15 соединен с синхровходом С D-триггера микросхемы 133ТМ2. Первый вход элемента И является вторым входом триггера 15, третий вход триггера 15 через инве ртор соединен с вторым входом элемента И, а выход элемента И соединен с R-входом D-триггера микросхемы 133ТМ2. Выход Q D-триггера микросхемы соединен с выходом триггера 15. На D- и S-входы

5

0

5

0

D-триггера микросхемы 1ЗЗТМ2 постоянно подан высокий потенциал.

Триггер 16 является синхронным триггером и построен, например, на D-триггере микросхемы 133ТМ2 и инверторе. Первый вход триггера 16 соединен с R-входом D-триггера микросхемы 1ЗЗТМ2. Второй вход триггера 16 через инвертор соединен с синхровходом CD-триггера микросхемы 133ТМ2. Выход триггера 16 соединен с выходом Q D-триггера микросхемы 133ТМ2. На D- и S-входы D-триггера микросхемы IЗЗТМ2 постоянно подан высокий потенциал.

Триггер 17 является счетлым триггером и построен на D-триггере микросхемы I33TM2 и элементе ИЛИ-НЕ. Первый вход триггера 17 соединен с R-входом D-триггера микросхемы 133ТМ2. Второй вход триггера 17 соединен с первым входом элемента ИЛИ- НЕ, третий вход триггера 17 соединеи с вторым входом элемента ИЛИ-НЕ. Выход элемента ИЛИ-НВ соединен с С-вхо- дом D-триггера микросхемы 133ТМ2. Прямой выход Q D-триггера микросхемы 133ТМ2 соединен с первым входом триггера 17. Инверсный выход Q D-триггера микросхемы 1ЗЗТМ2 соединен со своим D-входом и подключен к второму выходу триггера 17. На S-вход D-триггера микросхемы 133ТМ2 постоянно подан 5 высокий потенциал.

Элементы 20, 21 сравнения выполнены аналогично элементу 5 сравнения.

Источник 27 кода является источником двоичного кода и содержит, напри- 0 мер, набор переключателей, например, типа ПКБ. Вькодной код источника 27 определяется соотношением нажатых и отжатых кнопок ПКБ.

Источники 28-32 кода выполнены 5 аналогично источнику 27 кода.

Коммутатор 33 обеспечивает коммутацию одной из двух групп входов. Коммутируемая группа входов определяется видом управляющего сигнала. В 0 качестве коммутатора 33 может быть использована микросхема 531 КПП - че тырехразрядный селектор 2-1. На вход микросхемы 531КПМ постоянно подан низкий потенциал. А вход микросхемы 5 531КП11 является управляющим входом коммутатора 33. Входы Х„, Х,, Х,,, Х, микросхемы 531КП11 являются первой группой входов коммутатора 33. Входы Х,г, , }{, микросхемы 531КП1

являются второй группой входов коммутатора 33. Выходы микросхемы 531КП11 являются выходами коммутатора 33.

Коммутаторы ЗА, 35 выполнены аналогично коммутатору 33.

Устройство для обнаружения импуль- сньсх кодовых комбинаций работает следующим образом.

I

Устройство обнаруживает сложную импульсную кодовую комбинацию, состоящую из п следующих подряд одинаковых п-разрядных кодовых комбинаций и р следующих подряд одинаковых q- разрядных кодовых комбинаций, поступающих на входную шину 22, и вьщает сигнал обнаружения на выходную шину 26. Пусть для определенности п 4 и кодовая комбинация вида 1000, q 3 и кодовая комбинация вида 010.

Перед началом работы (при включении источника питания) на вход 25 начальной установки устройства подается импульс высокого потенциала, который устанавливает устройство в исходное состояние. Регистр I сдвига и счетчики 2, 3 импульсов обнулены, на выходе триггеров 6, 7, 15, 16, на первом выходе триггера 17, на выходе элементов И 10, 11, 12, 18, 19, на выходе элементов ИЛИ 8, 9, на выходе элементов 5, 20, 21 сравнения, на входной шине 22 присутствует низкий

потенциал, а на выходе счетчика 4 им- 35 4, то это импульс помехи. В этом слу- пульсов и на втором выходе триггера чае, при окончании импульса помехи 17 присутствует высокий потенциал. на входной шине 22, на выходе элемен- По шине 23 тактовой частоты поступают тактовые импульсы. На установочных

та ИЛИ 8 устанавливается низкий потенциал, который переводит счетчик 4

входах 24 устройства устанавливается двоичное число, примерно равное половине емкости счетчика 4 импульсов. Так как с выхода элемента ИЛу 8 на вход записи счетчика 4 импульсов поступает низкий потенциал, то счетчик .находится в режиме записи и двоичное число с установочных входов 24 устройства заносится в счетчик 4. В блоке 14 выдачи кодов на выходах источника 27 кода устанавливается двоичное число п, на вькодах источника 28 кода устанавливается двоичное число р, на выходе источника 29 кода устанавливается п-разрядная комбинация - в рассматриваемом примере 1000, на выходе источника 30 кода устанавливается q-разрядная кодовая комбинация, дополненная до разрядов нулевыми битами - Б рассматриваемом приме067568

ре 0010, на выходе источника 31 кода устанавливается двоичное число п в рассматриваемом примере 0100, на 5 выходе источника 32 кода устанавливается двоичное число q - в рассматриваемом примере ООП. Так как на управляющий вход блока 14 вьщачи кодов поступает низкий потенциал (с выхода

10 триггера 16), то коммутатор 33 коммутирует выходы источника 27 кода на первые выходы блока 14 выдачи кодов, коммутатор 34 коммутирует выходы источника 29 кода на вторые выходы

15 блока 14 выдачи кодов, коммутатор 35 коммутирует выходы источника 31 кода на вторые выходы блока 14 выдачи кодов. Таким образом, устройство оказывается подготовленным к работе.

2 На входную щину 22 устройства начинают поступать импульсы кодовых комбинаций, в том числе и помехи из канала связи. При появлении на входной гаине 22 импульса высокого потен- циала, на выходе элемента ИЛИ 8 появляется ВЫСОКИ потенциал, переводящий счетчик 4 в режим счета.Счетчик 4 начинает считать тактовые импульсы, поступающие по шине 23 тактовой час30 тоты. Тем самым осуществляется контроль по длительности поступившего на входную шину 22 импульса. Если импульс на входной шине 22 заканчивается раньше, чем заполнится счетчик

4, то это импульс помехи. В этом слу- чае, при окончании импульса помехи на входной шине 22, на выходе элемен-

та ИЛИ 8 устанавливается низкий потенциал, который переводит счетчик 4

в режим записи. Устройство оказывается в исход1 ом состоянии. Описанный процесс повторяется каждый раз после поступления импульса помехи. Таким образом, импульсы помехи подавляются устройством.

При поступлении на входную шину 22 импульса единичного символа кодовой комбинации вида 1000 на выходе элемента ИЛИ 8 появляется высокий потенциал, который переводит счетчик 4 в режим счета. Емкость счетчика 4 в период тактовых импульсов выбрана таким образом, чтобы счетчик 4 заполнялся от нулевого.состояния через интервал времени, равный номинальной длительности символов разрешенных кодовых комбинаций. Так как в исходном состоянии счетчик 4 заполнен наполовину, то, следовательно, появление импульса переполнения (низкого потенциала) на выходе счетчика 4 придется на середину единичного символа кодовой комбинации. При этом производится переключение триггера 7, на выходе которого устанавливается высокий потенциал, запрещающий перевод счетчика 4 в режим запи- .

си при поступлении на входную шину 22 Q в этом случае тактовый импульс прохоследующих символов кодовой комбинации и разрешающий поступление информации в регистр 1, счетчики 2,3. По заднему фронту импульса переполнения на выходе счетчика 4 производится запись единичного символа кодовой комбинации в регистр 1 сдвига. Одновременно в счетчик 3 заносится единица. При окончании импульса переполдит на выход элемента И ГО и в счетчик 2 записывается единица. Поступаю щий вслед за этим второй тактовый им пульс по шине 23 тактовой частоты 15 проходит на выход элемента И 18 и сбрасывает счетчик 3 и регистр 1 в нулевое состояние. Задним фронтом тактового импульса с выхода элемента И 18 производится установка тригнения счетчик 4 оказывается в нулевом 2Q геров 6, 17 в исходное состояние, состоянии, после чего продолжает счет ЕСЛИ кодовая комбинация, записанная

тактовых импульсов. Появление следующего импульса переполнения придется примерно на середину следующего (нулевого) символа кодовой комбинации. По заднему фронту импульса переполнения на выходе счетчика 4 производится запись второго символа кодовой комбинации в регистр 1 и содержимое счетчика 3 увеличивается на единицу. Таким образом, производится ввод символов импульсной кодовой комбинации с входной щиПы 22 в регистр 1 сдвига и подсчет счетчиком 3 количества символов кодовой комбинации. По заднему фронту п-го в общем случае, а в данном примере четвертого импульса переполнения, поступающего с выхода счетчика 4, на выходах счетчика 3 устанавливается двоичное число п - в рассматриваемом примере 0100, которое поступает на первые входы элемента 21 сравнения. Так как на вторые входы элемента 21 сравнения также поступает двоичное число, т.е. число 0100, то на выходе элемента 21 сравнения устанавливается высокий потенциал, который переключает триггер 6. На выходе триггера 6 устанавливается высокий потенциал, который раз- gQ га и записи количества символов в рещает прохождение тактового импуль- счетчик 3 повторяется, после чего в са следующего по шине 23 тактовой счетчик 2 добавляется единица. Таким частоты на выход элемента И 12. Так- образом счетчик 2 осуществляет подсчет следующих подряд кодовых комбина- gc ций вида 1 000 Если одна из кодовых ком- бинаций окажется ложной,то устройство

товый импульс с выхода элемента И 12 поступает на второй вход элементов И 10,11. Если в регистре сдвига к этому времени записана п-разрядная кодовая комбинация, т.е. в рассматриваемом случае крмбиНация 1000, то

возвращается в исходное состояние.

При по.ступлении т-й следующей подряд к(здовой комбинации вида 1000 на

675610

на выходе элемента 5 сравнения присутствует высокий потенциал, свродетельствующий о равенстве двоичных чисел на первых и вторых входах элемента 5 сравнения. Поэтому на выходе инвертора 13 присутствует низкий потенциал, запрещающий прохождение тактового импульса на выход элемента И 11,

дит на выход элемента И ГО и в счетчик 2 записывается единица. Поступающий вслед за этим второй тактовый импульс по шине 23 тактовой частоты проходит на выход элемента И 18 и сбрасывает счетчик 3 и регистр 1 в нулевое состояние. Задним фронтом тактового импульса с выхода элемента И 18 производится установка триггеров 6, 17 в исходное состояние, ЕСЛИ кодовая комбинация, записанная

в регистре 1 сдвига к моменту выдачи тактового импульса элементом И 12, отличается от разрещенной, т.е. является ложной, то в этом случае на

выходе элемента 3 сравнения будет низкий потенциал. Низкий потенциал на пьрсоде элемента 5 сравнения за- преща ;т прохождение тактового импульса на выход элемента И 10, а значит и срабатывание счетчика 2, но разрешает прохождение тактового импульса на выход элемента И 1I и далее на выход элемента ИЛИ 9, По заднему фронту тактового импульса производится сброс триггера 7 в исходное состояние. При этом на регистр 1, счетчики 2, 3, триггеры 6, 17 поступает сигнал сброса. Появление низкого потенциапа

на выходе триггера 7 вызывает появление низкого потенциала на выходе элемента ИЛИ 8, Счетчик 4 переводится в режим записи. Устройство оказывается в исходном состоянии. Если первая коовая комбинация была вида 1000, то при поступлении на входную шину 22 второй кодовой комбинации вида 1000 описанный процесс записи символов кодовой комбинации в регистр 1 сдвивозвращается в исходное состояние.

При по.ступлении т-й следующей подряд к(здовой комбинации вида 1000 на

11

входную гаину 22 в счетчике 2 окажется записано число m и элемент 20 .сравнения выдаст сигнал сравнения - высокий потенциал, который переключает триггер 15. На выходе триггера 15 устанавливается высокий потенциа-i Высоким потенциалом с выхода триггера 15 производится сброса счетчика 2 в нулевое состояние. При появлении тактового импульса на выходе элемента И 18 триггер 15 переключается и на его выходе устанавливается низкий потенциал. Фронтом низкого потенциала с выхода триггера 15 производится переключение триггера 16, на выходе которого устанавливается высокий потенциал. Высокий потенциал с выхода триггера 16 поступает на управляющий вход блока 14 выдачи кодов. Под воздействием высокого потенциала ка управляющем входе в блоке 14 выдачи кодов коммутатор 33 коммутирует выходы источника 28 кода на первые выходы блока 14, коммутатор 34 коммутирует выходы источника 30 кода на вторые выходы блока 14, коммутатор 35 коммутирует выходы источника 32 на третьи выходы блока 14. На входную шину 22 начинают поступать символы q-разрядной кодовой комбинации - в рассматриваемом случае вида 010. При появлении первого (нулевого символа) на входной шине 22 но примерно на середине стробируется задним фронтом импульса переполнения с выхода счетчика 4 и символ оказывается записанным в регистре 1. Одновременно в . счетчик 3 оказывается записана единица. По заднему фронту импульса переполнения на выходе счетчика 4 производится запись второго символа кодовой комбинации в регистр 1, и содержимое счетчика 3 увеличивается на единицу. При записи третьего символа кодовой комбинации в счетчик 3 в счетчике 3 оказывается записанным число q - в рассматриваемом примере ООП, которое поступает на первые входы блока 21 сравнения. Так как на вторые входы блока 21 поступает двоичное число q, т.е. число ООП, то на выходе элемента 21 сравнения устанавливается низкий потенциал, ко- торьй переключает триггер 6.

Далее повторяется описанный процесс появления тактовых импульсов последовательно на выходах элементов И .12, 18, срабатьшания элемента 5 срав0675612

)1ения, если в регистре 1 оказьшается записана действительно комбинация вида 010 и записи единицы в счетчик 2. g Если комбинация в регистре 1 окажется ложной, то производится описанный процесс сброса устройства в исходное состояние . При поступлении р-й следующей подряд кодовой комбина- 10 ции вида 010 на входную шину 22 в счетчике 2 окажется записано число р и элемент 20 сравнения выдаст сигнал сравнения высокого потенциала. При этом триггер 15 переключается и на 15 его выходе устанавливается высокий потенциал. Так как на выходе триггера 16 уже присутствует высокий потенциал, то сигнал с выхода триггера 15 проходит на выход элемента И 19 и 20 поступает на выходную шину 26 в качестве сигнала обнаружения сложной кодовой комбинации, состоящей из m следую1цих подряд п-разрядных кодовых комбинаций и р следующих подряд q- 25 разрядных кодовых комбинаций. Сигнал обнаружения проходит также на выход элемента ИЛИ 9. При появлении тактового импульса на выходе элемента И 18 триггер 15 переключается и на его 30 выходе устанавливается низкий потенциал. Сигнал обнаружения на выходе элемента И 19 оканчивается. Задним фронтом сигнала обнаружения, который проходит на выход элемента ИЛИ 9, -,- производится установка триггера 7, а вместе с ним и всего устройства в исходное состояние, после чего устройство начинает анализ входных сигналов по длительности, поступающих 4Q по входной шине 22. При фиксировании един ;чного символа кодовой комбинации описанньгй процесс обнаружения повторяется .

Таким образом, предлагаемое уст- 45 ройство по сравнению с прототипом обладает расширенными функциональными возможностями за счет расширения перечня обнаруживаемых кодовых комбинаций. Прототип обеспечивает обнаруже- Q ние только т. следующих подряд п„р- разрядных кодовых комбинаций. Предлагаемое устройство обеспечивает обнаружение сложной кодовой комбинации, состоящей из га следующих подряд п- Ес разрядных кодовых комбинаций и р следующих подряд q-разрядньгх кодовых комбинаций.

Так как в кодовых комбинациях, обнаруживаемых предлагаемым устройстBOM, могут изменяться четыре параметра: га, п, р, q, а в кодовых комбина- цихя, обнаруживаемых прототипом, два параметра: ninp ripp , то, следовательно, перечень обнаруживаемых предлагаемым устройством кодовых комбинаций шире, чем у прототипа. Так, например в частном случае, выбрав m Ш пр

Р -2 Ч , получим,

что сложная кодовая комбинация, обнаруживаемая предлагаемым устройством, соответствует кодовой комбинации, обнаруживаемой прототипом. Во всех других случаях сложная кодовая комбинация, обнаруживаемая предлагаемым устройством,не может быть обнаружена прототипом, т.е. предлагаемое устройство обеспечивает обнаружение как кодовых комбинаций, обнаруживаемых прототипом, так и обнаружение сложных кодовых комбинаций, которые не могут быть обнаружены прототипом.

Формула изобретения

35

Ю

второго триггера соединен с тактовым входом регистра сдвига, со счетным

45

50

55

5

0

5

5

о

5

0

5

входом второго сче,тчика импульсов и выходом третьего счетчика импульсов, информационные входы которого подключены к установочным входам устройства, первые входы элемента сравнения соединены с выходами регистра сдвига, вход начальной установки устройства соединен с третьим входом второго триггера, отличающееся тем, что, с целью расширения диапазона обнаруживаемых импульсных кодовых комбинаций, введены два дополнительных элемента сравнения, третий, четвертый и пятый триггеры, четвертый и пятый элементы И и блок выдачи кодов, первые выходы которого соединены с перв.1ми входами первого дополнительного элемента сравнения, вторые выходы блока выдачи кодов соединены с вторьг-ш входами элемента сравнения, Bbixoniii первого счетчика импульсов соединены с вторыми входами первого дополнительного элемента сравнения, выход которого соединен с первым входом третьего триггера, второй вход .которого соединен с вторым входом первого элемента ИЛИ,с первым входом четвертого триггера, первым входом сброса второго счетчика импульсов, первым входом сброса регистра сдвига, нзрвьгм входом Пятого триггера и первым входом первого триггера, второй вход которого соединен с вторым входом сброса второго счетчика импульсов, вторым входом сброса регистра сдпига, третьим входом третьего триггера, выходом четвертого элемента И и и юрым входом пятого триггера, гшрЕый вход четвертого элемента И,- подключен к шине тактовой частоты, вторюй вход четвертого элемента И соединен с первым выходом пятого триггера,, третий вход которого соединен с выходом третьего элемента И, пьгхс Д третьего триггера соединен с HTopi.iM входом сброса первого счетчика импульсов, первым входом пятого элемента И и вторым входом четвертого триггера, выход которого соединен с вторым входом пятого элемента И и управляющим входом блока выдачи кодов, выход пятого элемента И подключен к выходной шине, выходы второго счетчика импульсов соединены с первыми входами второго дополнительного элемента сравнения, вторые входы которого соединены с третьими выходами блока выДачи кодов, выход второго дополнительного элемента сравнения соединен с третьим входом первого триггера, второй выход пятого триггера соединен с третьим входом третьего элемента И.

фиг.2

Авторы

Даты

1988-06-30—Публикация

1986-12-18—Подача