(Sk) УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обработки информации | 1979 |

|

SU858059A1 |

| Приемник тональных сигналов | 1989 |

|

SU1635288A1 |

| Генератор синусоидальных колебаний | 1989 |

|

SU1786634A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ ПОМЕХ | 1988 |

|

SU1841099A1 |

| Устройство для приема и контролядОСТОВЕРНОСТи иМпульСНыХ СигНАлОВ | 1979 |

|

SU851444A1 |

| УСТРОЙСТВО ОХРАННОЙ СИГНАЛИЗАЦИИ | 1991 |

|

RU2031445C1 |

| Селектор импульсов по длительности | 1982 |

|

SU1088108A2 |

| Устройство для выделения импульсныхСигНАлОВ | 1979 |

|

SU824483A1 |

| Система для передачи цифровой информации по проводным каналам связи | 1985 |

|

SU1256233A1 |

| МОДУЛЬ ВЫСОКОВОЛЬТНОГО КЛЮЧЕВОГО УСИЛИТЕЛЯ МОЩНОСТИ | 2018 |

|

RU2716041C1 |

Изобретение относится к телеметрии, передаче и обработке информации и предназначено для подавления импульсных и флуктуационных помех. Известно устройство защиты от помех, содержащее селектор импульсо выход которого соединен с регенератором импульсного сигнала l. Недостатком этого устройства является низкая точность сохранения формы сигнала при выделении его из помех. Известно также устройство защиты от помех, содержащее усилитель, элемент задержки, формирователь импульсов малой длительности и элемент сов падения, первый вход которого соединен с выходом формирователя импуль сов малой длительности, вход которог соединен с выходом элемента задержки вход Kotoporo соединен с вторым входом элемента совпадения и выходом усилителя, вход которого соединен с входом устройства С 2J. Недостатком известного устройства является сравнительно низкая помехоустойчивость. Цель изобретения - повышение помехоустойчивости . Поставленная цель достигается тем, что в устройство защиты от помех, содержащее усилитель, элемент задерж ки, формирователь импульсов малой длительности и элемент совпадения, первый вход которого соединен с выходом формирователя импульсов малой длительности, вход которого соединен с выходом элемента задержки, вход которого соединен с вторым входом элемента совпадения и выходом усилителя, вход которого соединен с входом устройства, введены регулируемый элемент задержки, инвертор, сумматор, элемент разделения полярности импульсов, первый и второй дополнительные формирователи импульсов малой длительности, емкостной накопитель, дополнительный элемент совпадения, триггер, дополнительный инвертор и дополнительный триггер, выход которо го соединен с первым входом дополнительного элемента совпадения, выход, второй и третий входы которого соединены соответственно с выходом устройства защиты от помех, прямым выходом триггера и выходом емкостного накопителя, первый вход которого соединен с входом первого дополнительного формирователя импульсов малой длительности и первым выходом элемента разделения полярности импульсов, второй выход которого соединен с входом дополнительного инвертора , выход которого соединен с входом второго дополнительного формирователя импульсов малой длительности, выход которого соединен с первым входом триггера, второй вход и инверсный выход которого соединены соответственно с выходом первого дополнительного формирователя импульсов малой длительности и вторым входом емкостного накопителя, который соединен с первым входом дополнитель ного триггера,второй вход которого соединен с выходом элемента совпадения, а вход элемента разделения поля ности импульсов соединен с выходом сумматора, первый и второй входы кот торого соединены соответственно с вы ходом инвертора и выходом элемента задержки, который соединен с первым входом регулируемого элемента ,задерж ки , выход и второй вход которого сое динен соответственно с входом инвертора и вторым входом устройства защи

ты от помех.

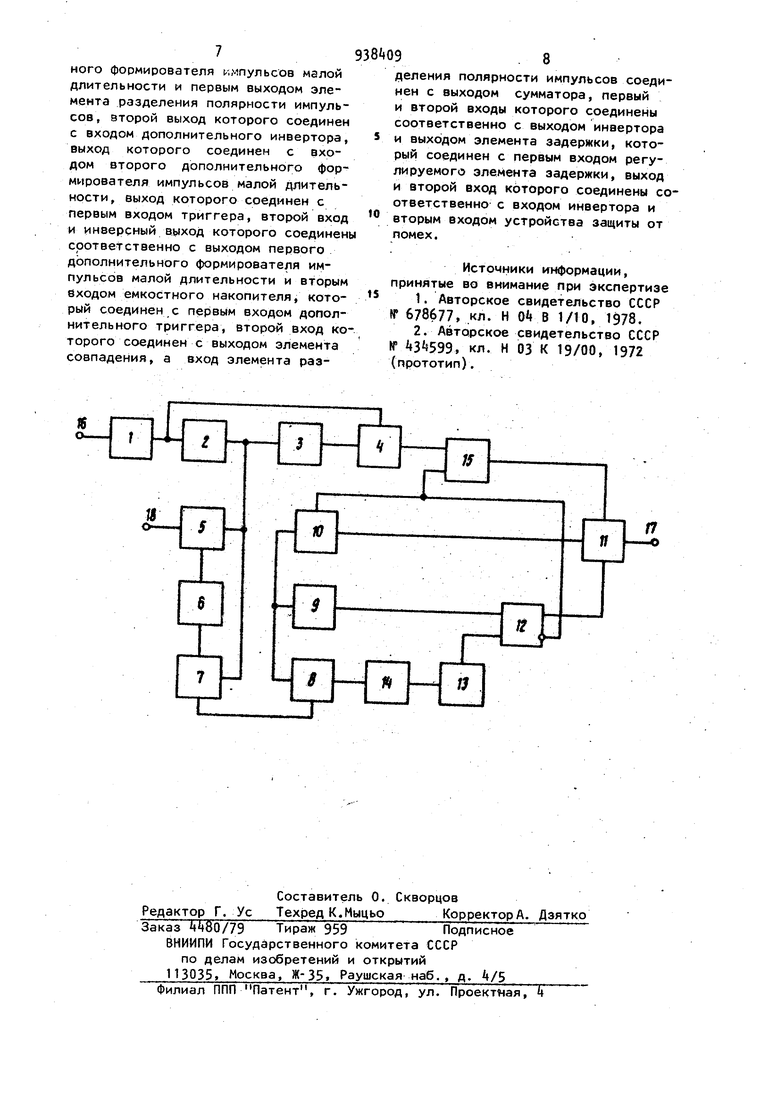

На чертеже показана структурная схема устройства защиты от помех.

Устройство защиты от помех содержит усилитель 1, элемент 2 задержки, формирователь 3 импульсов малой длительности, элемент А совпадения, регулируемый элемент 5 задержки, инвертор 6, сумматор 7 элемент 8 разделения полярности импульсов, пер-50 вый дополнительный формирователь 9 импульсов малой длительности, емкостной накопитель 10, дополнительный элемент 11 совпадения, триггер 12, второй дополнительный формирователь 13 импульсов малой длительности, дополнительный инвертор 14 и дополнительный триггер 15, первый вход

держки, который соединен с первым входом регулируемого элемента 5 задержки, выход и второй вход которого соединены соответственно с входо инвертора 6 и вторым входом 18 устройства защиты от помех. I . . -

Устройство защиты от помех работает следующим образом.

Пройдя через усилитель 1, смесь 55 элемента Ц совпадения соединен с выходом формирователя импульсов малой длительности 3i вход которого соединен с выходом элемента 2 задержки, вход которого соединен с вторым входом элемента Ц совпадения и выходом усилителя i, вход которого соединен с входом 16 устройства, выход дополнительного триггера 15 соединен с первым входом дополнительного элемента 11 совпадения, выход, второй и третий входы которого соединены.соответственно с выходом 17 устройства защиты от помех, прямым выходом триггера 12 и выходом емкостного накопи/ теля 10, первый вход которого соединен с входом первого дополнительного формирователя 9 импульсов малой длительности и первым выходом элемента 8 разделения полярности импульсов, второй выход которого соединен с входом дополнительного инвертора 14, выход которого соединен с входом второго дополнительного формирователя 13 импульсов малой длительности, выход которого соединен с первым входом триггера 12, второй вход и инверсный выход каторого соединены соответственно с выходом первого дополнительного формирователя 9 импульсов малой длительности и вторым входом емкостного накопителя 10, который соединен с первым входом дополнительного триггера 15, второй вход которого соединен с выходом элемента 4 совпадения, а вход элемента i8 разделения полярности импульсов соединен с выходом сумматора 7, первый и второй входы которого соединены соответственно с выходом инвертора 6 и выходом элемента 2 заимпульсов полезного и помехового сигналов и флуктуационных помех поступает на вход элемента 2 задержки и на один из входов элемента 4 совпадения. Время задержки элемента 2 задержки немного меньше длительности импульсов полезного сигнала. Из задержанного на время сигнала формирователь 3 импульсов малой длительности формирует короткие импульсы, совпадающие по времени с передними фронтами импул сов сигнала. На выход элемента k с впадения проходят короткие импульсы только в том случае, если длительность соответствующих входных импульсов превышает длительность времени задержки Т элемента 2 задержки. Таким образом, импульсы помех, длительность которых меньше времен задержки , на выход элемента А совпадения не приходят. Каждый из импульсов переводит триггер 15 в единичное состояние. Через управляющий вход 18 оператор устанавливает необходимую длительность времени задержки C,.per регулируемого элемента 5 задержки. Время задержки 7Гэ, Устанавливается оператором меньше времени корреляции флуктуационных помех. Инвертор 6 изменяет полярность выходного сигнала регулируемой линии элемента 5 задержки. Инвертированны сигнал с выхода инвертора 6 поступает на вход сумматора 7. В результате сложения сигналов на. выходе сумматора 7 появляется биполярная последовательность импульсов, а флуктуационные помехи компенсируются. Элемент 8 разделения полярности импульсов осуществляет разделение биполярных импульсов на положительные и отрицательные, а амплитуда каждой пары разнополярных импульсов равна амплитуде соответствующего импульса входного сигнала. Из положительных импульсов емкостный накопитель 10 формирует расширенные импульсы. Длительность переднего фронта импульсов не превышает длите ности времени задержки/C adper Формирователь 9 импульсов малой дли тельности фсзрмирует короткие импуль сы, каждым из которых триггер 12 переводится в единичное состояние. Инвертор 1 изменяет полярность отрицательных импульсов, а из инвер тированных им импульсов формировате 13 импульсов малой длительности фор мирует короткие импульсы,: которыми осуществляется перевод триггера 12 в нулееое состояние. Передними фрон тами импульсов с выхода триггера 11 осуществляется перевод триггера 15 ОЭ« в нулевое состояние и быстрый разряд емкостного накопителя 10. При совпадении по времени информационного импульса и управляющих импульсов с выхода триггера 15 и импульса с выхода триггера 12 на выходе элемента совпадения 11 появляется ммпульс, амплитуда которого равна амплитуде соответствующего информационного импульса выходного сигнала, а длительность равна длительности соответствующего импульса входного сигнала триггера 12, что соответствует длительности соответствующего полезного импульса входного сигнала:Таким образом, предлагаемое устрой:Ство защиты от. помех позволяет .подавать короткие импульсные помехи и флуктуационные помехи, что обеспечивает значительное повышение помехоустойчивости устройства и повышение Достоверности восстановления результатов сообщений. Формула изобретения Устройство защиты от помех, содержащее усилитель, элемент задержки, формирователь импульсов малой длительности и элемент, совпадения, первый вход которого соединен с выходом формирователя импульсов малой длительности, вход которого соединен с выходом элемента, задержки, вход которого соединен с вторым входом элемента совпадения и выходом усилителя, вход которого соединен с входом устройства, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены регулируемый элемент задержки, инвертор, сумматор, элемент разделения полярности импульсов, первый и второй дополнительные формирователи импуЛьсов малой длительности, емкостной накопитель, дополнительный элемент совпадения, Триггер, дополнительный инвертор и дополнительный триггер, выход которого соединен с переым входом дополнительного элемента совпадения, выход, второй и третий входы которого соединены соответственно с выходом устройства защиты от помех, прямым выходом триггера и выходом емкостного накопителя, первый вход которого соединен с входом.первого дополнительиого формирователя ,мпyльcoв малой длительности и первым выходом элемента разделения полярности импульсов, второй выход которого соединен с входом дополнительного инвертора, выход которого соединен с входом второго дополнительного формирователя импульсов малой длительности , выход которого соединен с первым входом триггера, второй вход и инверсный выход которого соединены соответственно с выходом первого дополнительного формирователя импульсов малой длительности и вторым входом емкостного накопителя, который соединен с первым входом дополнительного триггера, второй вход которого соединен с выходом элемента совпадения, а вход элемента разделения полярности импульсов соединен с выходом сумматора, первый и второй входы которого соединены соответственно с выходом инвертора и выходом элемента задержки, который соединен с первым входом регулируемого элемента задержки, выход и второй вход которого соединены соответственно с входом инвертора и вторым входом устройства защиты от помех.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 678677, кл. Н 0 В 1/10, 1978.

Авторы

Даты

1982-06-23—Публикация

1980-08-12—Подача