Предлагаемое устройство относится к области радиолокации. Оно может быть использовано в радиолокационных приемниках для защиты от помех.

Известен компенсатор боковых лепестков, содержащий основной канал, компенсационный канал, коррелятор, генератор, полосовые фильтры, вычитатель и перемножители [1].

В вычитателе известного компенсатора происходит вычитание помех основного и компенсационного каналов путем управления комплексными частотными характеристиками компенсационного канала при помощи модуляторов и квадратурного фазовращателя.

Одним из недостатков известного компенсатора является корреляционный характер цепи обратной связи. Это ограничивает возможность применения известного компенсатора на СВЧ и затрудняет встраивание его в антенные решетки.

Известен автокомпенсатор, содержащий балансные устройства, усилитель, вычитатель, фазовращатель, детектор, перемножители, интеграторы, сумматоры и генератор поисковых колебаний [2].

В таком автокомпенсаторе вместо цепей когерентного опорного сигнала введен генератор поисковых колебаний, что позволяет отказаться от корреляционной цепи обратной связи на несущей частоте. Это упрощает реализацию устройства на СВЧ и расширяет возможности его применения.

Однако известному автокомпенсатору присущ недостаток - необходимо из сигнала ошибки выделять и накапливать спектральные составляющие поисковых колебаний относительно небольшого уровня, что обуславливает низкую устойчивость и малое быстродействие автокомпенсатора. Малое быстродействие делает автокомпенсатор неэффективным в сложной помеховой обстановке, особенно при воздействии переключающихся помех от нескольких пространственно разнесенных источников.

Из известных устройств компенсации помех наиболее близким к заявляемому устройству является экстремальный автокомпенсатор, содержащий сумматор, фазовращатель, регуляторы амплитуды, интеграторы, ключи, детектор, устройство задержки и вычитатель [3; (с. 71, рис. 3)].

В таком устройстве регулирование компенсационным каналом, в который входит два регулятора амплитуды и фазовращатель, осуществляется релейной цепью обратной связи по экстремальному алгоритму. Это упрощает устройство и повышает его устойчивость и степень подавления помех.

Однако в известном устройстве вследствие постоянства шага управления компенсационным каналом, присущего релейным схемам, сохраняется низкое быстродействие подавления помех. Это затягивает длительность неэффективной работы автокомпенсатора в переходном режиме и ограничивает использование известного автокомпенсатора в сложной помеховой обстановке, особенно в условиях кратковременных помех, выдаваемых последовательно несколькими засинхронизированными постановщиками помех с разных пространственных направлений, - так называемых «переключающихся» или «мерцающих» помех, - наиболее вероятных в современных условиях.

Таким образом, недостатком известных устройств подавления помех является низкое быстродействие.

Целью предлагаемого изобретения является повышение быстродействия устройства подавления помех.

Поставленная цель достигается тем, что в устройство, содержащее последовательно включенные сумматор, первый вход которого является основным входом устройства, а выход которого является выходом устройства, детектор, фильтр низкой частоты, блок выборки-хранения и компаратор, второй вход которого объединен со входом блока выборки-хранения, первый регулятор амплитуд вход которого является компенсационным входом устройства, а выход подключен ко второму входу сумматора, фазовращатель, второй регулятор амплитуды, выход которого подключен к третьему входу сумматора, а вход через фазовращатель подключен к компенсационному входу устройства, два интегратора и два ключа, причем выходы первого и второго ключей через интеграторы подключены к управляющим входам первого и второго регуляторов амплитуды, управляющие входы первого и второго ключей подключены к управляющим входам устройства, а тактовый вход блока выборки-хранения подключен к входу тактовых синхроимпульсов устройства, введены последовательно включенные преобразователь напряжение-длительность импульса, первая схема совпадения, инвертор полярности импульсов и третий ключ, генератор импульсов, выход которого подключен ко второму входу первой схемы совпадения, четвертый ключ, вход которого подключен к выходу первой схемы совпадения, последовательно включенные вторая схема совпадения и счетный триггер, прямой и инверсный выходы которого подключены к управляющим входам третьего и четвертого ключей, причем выходы третьего и четвертого ключей объединены и подключены к объединенным входам первого и второго ключей, выход компаратора подключен ко входу второй схемы совпадения, а второй вход второй схемы совпадения и запускающий вход преобразователя напряжение-длительность импульса подключены к входам тактовых синхроимпульсов устройства.

Введенный преобразователь напряжение-длительность импульса служит для пропорционального преобразования уровня продетектированного и сглаженного фильтром низкой частоты выходного сигнала ошибки устройства в длительность импульса, поступающего на первую схему совпадения.

Генератор служит для генерации импульсов, поступающих на первую схему совпадения.

Схемой совпадения формируется пачка импульсов, длительность которой пропорциональна уровню сигнала ошибки устройства.

Инвертор полярности импульсов обеспечивает подачу на вход третьего ключа импульсов той же амплитуды и длительности, что и на вход четвертого ключа, но противоположной полярности.

Вторая схема совпадения обеспечивает поступление на вход счетного триггера тактового синхроимпульса только при срабатывании компаратора, т.е. при увеличении сигнала ошибки на входе компаратора, по сравнению с запомненным в блоке выборки-хранения значением сигнала ошибки предыдущего такта.

Счетный триггер по приходу на его вход тактового синхроимпульса меняет состояние своих выходов на противоположное, переключая третий и четвертый ключи.

Третий и четвертый ключи служат для подачи на входы первого и второго ключей импульсов, изменяющих управляющие напряжения регуляторов амплитуды, той или другой полярности в зависимости от состояния счетного триггера.

В своей совокупности все узлы предлагаемого устройства обеспечивают изменение длительности пачек импульсов, управляющих регуляторами амплитуды (величину шагов регулирования), пропорционально уровню нескомпенсированной выходной помехи и, таким образом, повышение быстродействия устройства.

Совокупность отличительных признаков, предложенных в данном изобретении, авторам не известна.

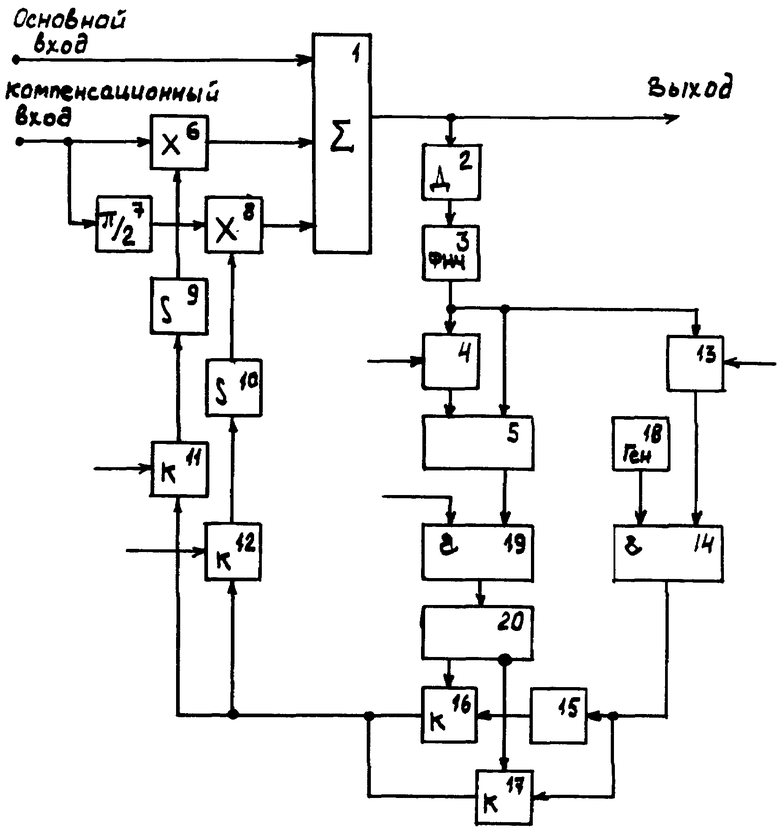

На чертеже представлена функциональная схема устройства.

Устройство компенсации помех содержит сумматор 1, детектор 2, фильтр низкой частоты 3, блок выборки-хранения 4, компаратор 5, первый регулятор амплитуды 6, фазовращатель 7, второй регулятор амплитуды 8, первый и второй интеграторы 9, 10, первый и второй ключи 11, 12, преобразователь напряжение-длительность импульса 13, первую схему совпадения 14, инвертор полярности импульсов 15, третий и четвертый ключи 16, 17, генератор импульсов 18, вторую схему совпадения 19 и счетный триггер 20.

Ключи 16, 17 выполнены на мультиплексорах типа 561 КП1, допускающих коммутацию сигналов обеих полярностей и объединение по выходу при противофазном управлении [4; (с. 34, рис. 4)].

Преобразователь напряжение-длительность импульса 13 выполнен по известной схеме [5; (с. 105, рис. 5.6)].

Генератор импульсов 18 выполнен по известной схеме [6; (с. 310, рис. 14,6б)]. В качестве схемы совпадения 14, 19 можно использовать логические элементы [6; (с. 318-120)], в предлагаемом устройстве использована микросхема 155ЛАЗ.

Инвертор полярности импульсов 15 выполнен на операционном усилителе по известной схеме [5; (с. 32. рис. 2.1б)]

В качестве счетного триггера 20 можно использовать известным образом включенный универсальный триггер [6; с. 324)], конкретно использован 155ТМ2.

Предлагаемое устройство компенсаций помех работает следующим образом.

На основной вход устройства поступают полезные сигналы и помехи, на компенсационный вход поступают главным образом помехи. В сумматоре 1 происходит вычитание помех основного и компенсационного входов. Совместное регулирование амплитуд и фаз помех для их дальнейшего вычитания обеспечивается регуляторами амплитуды 6, 8 и квадратурным фазовращателем 7.

Управляющие напряжения регуляторов 6, 8 поступают с выходов интеграторов 9, 10. Двустороннее изменение управляющих напряжений происходит вследствие накопления интеграторами 9, 10 управляющих импульсов положительной либо отрицательной полярности. Последовательность управления регуляторами 6 и 8 определяется переключением первого и второго ключей 11, 12 в соответствии с выбранным алгоритмом настройки.

Нескомпенсированный остаток помехи на выходе устройства, после детектирования в детекторе 2 и сглаживания в фильтре низкой частоты 3, является сигналом ошибки петли обратной связи устройства.

Запоминание уровня сигнала ошибки в блоке выборки-хранения 4 на один такт регулирования позволяет при помощи компаратора 5 оценить направление изменения сигнала ошибки - его увеличение или уменьшение. Уменьшение сигнала ошибки обуславливает сохранение выбранного направления изменения управляющего напряжения регулятора амплитуды 6 или 8 на следующий такт регулирования, увеличение сигнала ошибки обуславливает изменение этого направления, а практически - изменение полярности управляющих импульсов на обратное.

Управляющие импульсы формируются в генераторе импульсов 18 и поступают на вход схемы совпадения 14.

Преобразователь напряжение-длительность импульса 13 в каждом такте формирования по приходу синхроимпульса вырабатывает импульс, длительность которого зависит от уровня сигнала ошибки, и который поступает на второй вход схемы совпадения 14. Таким образом на выходе схемы совпадения 14 формируются пачки регулирующих импульсов, причем количество импульсов в пачке соответствует уровню сигнала ошибки. Минимальному сигналу ошибки соответствует минимальное количество импульсов в пачке, определяющее наименьший шаг изменения управляющих напряжений и в конечном счете величину минимально достижимого остатка помех. Наибольшему уровню сигнала ошибки соответствует наибольшее количество импульсов в пачке, определяемое из требований устойчивости устройства, и, соответственно наибольший шаг перестройки регуляторов амплитуды 6 и 8. Вследствие такой зависимости в начальном периоде настройки, когда уровень сигнала ошибки большой, регулирование производится большими шагами, обеспечивая быструю грубую настройку устройства, а с уменьшением сигнала ошибки шаг настройки уменьшается до минимального, обеспечивая необходимую точность компенсации помех.

Полярность накапливаемых интеграторами 9 и 10 управляющих импульсов в каждом такте регулирования определяется состоянием счетного триггера 20, выходными напряжениями которого поочередно открывается один из ключей 16, 17.

Изменение состояния счетного триггера 20 происходит следующим образом. Перед приходом на тактовый вход блока выборки-хранения тактового синхроимпульса на одном входе компаратора 5 действует текущее значение сигнала ошибки с выхода фильтра низкой частоты 3, а на другом - выборка этого сигнала ошибки, сделанная блоком выборки-хранения по предыдущему тактовому синхроимпульсу. Разрешающий уровень для второй схемы совпадения 19 на выходе компаратора 5 вырабатывается при превышении текущим значением сигнала ошибки выборки этого сигнала за предыдущий такт. Таким образом, тактовый синхроимпульс проходит через вторую схему совпадения 19 и изменяет состояние счетного триггера 20 тогда, когда уровень сигнала ошибки за такт регулирования увеличивается, т.е. когда направление регулирования оказывается неправильным с точки зрения подавления помех. Изменение состояния счетного триггера 20 вызывает переключение третьего 16 и четвертого 17 ключей, трансляцию на входы ключей 11, 12 и далее на интегратор 9 или 10 импульсов противоположной полярности и, соответственно, изменение направления регулирования регулятора амплитуды 6 или 8.

Совместная работа вновь введенных блоков обеспечивает регулирование амплитуд и фаз помех компенсационного входа устройства шагами, величина которых зависит от уровня некомпенсированной помехи. На начальном этапе настройки эти шаги большие и обеспечивают высокую скорость сходимости процесса компенсации помех, а на конечном этапе они малые и обеспечивают необходимую точность компенсации помех.

Таким образом, в предлагаемом устройстве обеспечивается повышение быстродействия компенсации помех без ухудшения точности их компенсации.

Техническая эффективность предлагаемого устройства заключается в повышении быстродействия компенсации помех. Это позволяет увеличить время эффективной работы РЛС, даже в условиях переключающихся помех.

Экономическая эффективность предлагаемого устройства заключается в том, что для достижения такого же увеличения подпомеховой видимости РЛС (в среднем, при воздействии переключающихся активных помех), например, путем повышения мощности передатчика, требуются гораздо большие затраты.

Литература

1. Патент США №3881177, 1975 г., т. 933, № 5.

2. Р.И. Колотушкин "Автокомпенсатор с поисковыми колебаниями". Вопросы специальной радиоэлектроники. Сер. РЛТ. вып. 21, 1984 г., с. 130-136.

3. М.А. Лейких "О компенсации помех с помощью поискового экстремального автокомпенсатора". Вопросы специальной радиоэлектроники. Сер. РЛТ, вып.1, 1984 г.

4. «Радио» №11, 1986 г.

5. В.И. Щербаков, Г.И. Грездов. "Электронные схемы на операционных усилителях. Киев, "Техника", 1983 г.

6. Справочник по схемотехнике для радиолюбителя. Под ред. В.П. Боровского, Киев, "Техника", 1987 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь неэлектрических величин в цифровой код | 1976 |

|

SU639140A2 |

| Устройство для активного подавления шума | 1988 |

|

SU1642512A1 |

| ПРИЕМО-ПЕРЕДАЮЩЕЕ УСТРОЙСТВО РАДИОЛОКАТОРА | 1985 |

|

SU1841065A1 |

| Устройство для считывания информации из доменной памяти | 1988 |

|

SU1558226A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИГНАЛОВ В ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКЕ | 1983 |

|

RU2035097C1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПОМЕХ ДЛЯ ПРИЕМНИКОВ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2003 |

|

RU2253183C1 |

| Устройство для управления вентильным преобразователем | 1991 |

|

SU1774446A1 |

| Регулятор электрической мощности переменного тока(его варианты) | 1981 |

|

SU983690A1 |

| Умножитель частоты | 1982 |

|

SU1083330A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 1999 |

|

RU2163380C1 |

Изобретение относится к области радиолокации и может быть использовано в радиолокационных приемниках для защиты от помех. Устройство компенсации помех содержит последовательно включенные сумматор, первый вход которого является основным входом устройства, а выход является выходом устройства, детектор, фильтр низкой частоты, блок выборки-хранения, тактовый вход которого подключен ко входу тактовых синхроимпульсов устройства, и компаратор, второй вход которого объединен со входом блока выборки-хранения, первый регулятор амплитуды, вход которого является компенсационным входом устройства, а выход подключен ко второму входу сумматора, фазовращатель, второй регулятор амплитуды, два интегратора и два ключа. Также в устройство введены преобразователь напряжение-длительность импульса, первая схема совпадения, инвертор полярности импульсов и третий ключ, генератор импульсов, четвертый ключ, последовательно включенные вторая схема совпадения и счетный триггер, прямой и инверсный входы которого подключены к управляющим входам третьего и четвертого ключей. Технический результат - повышение быстродействия устройства. 1 ил.

Устройство компенсации помех, содержащее последовательно соединенные сумматор, первый вход которого является основным входом устройства, а выход является выходом устройства, детектор, и фильтр низкой частоты, блок выборки-хранения, информационный вход которого соединен с выходом фильтра низкой частоты, компаратор, информационный вход которого соединен с выходом блока выборки-хранения, а вход опорного напряжения соединен со входом блока выборки-хранения, фазовращатель на π-2, вход которого является компенсационным входом устройства, первый и второй регуляторы амплитуды, сигнальные входы которых соединены, соответственно, с первым и вторым выходами фазорасщепителя на π-2, а выходы соединены, соответственно, со вторым и третьим входами сумматора, первый и второй ключи, первый и второй интеграторы, входы которых соединены с выходами соответствующих ключей, а выходы соединены с управляющими входами соответствующих регуляторов амплитуды, управляющие входы первого и второго ключей являются, соответственно, первым и вторым управлявшими входами устройства, а синхровход блока выборки-хранения является синхровходом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены преобразователь напряжение-длительность импульса, информационный вход которого соединен с выходом фильтра низкой частоты, первый элемент И, первый вход которого соединен с выходом преобразователя напряжение-длительность импульса, третий ключ, инвертор полярности импульсов, вход которого соединен с выходом первого элемента И, а выход соединен с информационным входом третьего ключа, генератор импульсов, выход которого соединен со вторым входом первого элемента И, четвертый ключ, информационный вход которого соединен с выходом первого элемента И, последовательно соединенные второй элемент И, первый вход которого соединен с выходом компаратора, и счетный триггер, прямой и инверсный выходы которого соединены, соответственно, с управляющими входами третьего и четвертого ключей, выходы третьего и четвертого ключей соединены с соединенными параллельно информационными входами первого и второго ключей, а второй вход второго элемента И и запускающий вход преобразователя напряжение-длительность импульса соединены с синхровходом устройства.

| Лейких М.А | |||

| О компенсации помех с помощью поискового экстремального автокомпенсатора // Вопросы специальной радиоэлектроники, сер | |||

| РЛТ - Вып | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент №3881177, США G01S 7/36, Компенсатор боковых лепестков, 1975 г. | |||

Авторы

Даты

2015-06-10—Публикация

1988-12-23—Подача