(5) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДИСПЛЕЯ

1

Изобретение относится к электронным дискретным устройствам автоматики, телемеханики и вычислительной техники, и предназначено для повышения достоверности отображения информации при выводе ее на телевизион.ный индикатор. Изображение монет быть использовано в системах отображения информации, использующих телевизионные индикаторы.

Известно устройство для контроля дисплея, содержащее последовательно соединенные клавишную панель, шифратор, схему формирования видеосигналов и блок управления передачей, соединенный с линией связи через демодулирукицее устройство, буферную память и индикаторный блок, связанный с управляющим блоком, предназначенным для переключения оконечного устройства tl.

Недостатком этого устройства является то, что решение о правильности (достоверности) информации

принимает человек-оператор, наблюдающий эту информацию на экране. Это увеличивает загрузку оператора и снижает достоверность контроля сложных изображений, насыщенных цифровой информацией.

Наиболее близким к предлагаемому по техническому решению является устройство для обнаружения сбоев информации дисплея, содержащее оперативную память, выходы которой соединены с входами узла контроля четности и формирователя видеосигнала, выход которого через видеоусилитель соединен с входом индикатора, генератор импульсов, элемент НЕ-ИЛИ, входы которого соединены с выходами узла контроля четности и генератора импульсов, а выход - с управляющим входом видеоусилителя 2.

Недостатком известного устрой ства является то, что контролем охвачена только оперативная память, а формирователь видеосигнала и узлы блока синхронизации и управления, относящиеся к формирователю видеосигнала, контролем не охвачены. Это существенно снижает надежность устройства и достоверность отображаемой информации, так как формирователь видеосигнала и его управление являются одними из самых сложных узлов дисплея. Цель изобретения - повышение надежности устройства и достоверности отображаемой информации. Поставпениая цель достигается тем, что устройство для контроля ди плея, содержащее последовательно соединенные блок памяти, формирователь видеосигналов и телевизионный индикатор, управляющие входы которы подключены к соответствующим выходам блока управления, содержит блок задания этапов контроля, соединенный двухсторонней связью с блоком управления, вход которого подключен к выходу блока памяти, и блок обработки избыточных кодов, входы которого соединены с выходами блока пам ти, формирователя видеосигналов, бл ка задания этапов контроля и соотве ствующим выходом блока управления, Блок задания этапов контроля содержит первый счетчик, первый вход которого соединен с первым входом первого регистра и является соответ ствующим входом блока, второй вход подключен к второму входу первого регистра и первому выходу первого д

шифратора, второй вход которого соединен с третьим входом первого регистра, первым входом второго дешифратора и является соответствующим входом блока, третий вход подключен к четвертому входу первого регистра и выходу первого счетчика, а четвертый вход - к выходу второго дешифратора, второй вход которого соединен с выводом первого регистра, а второй и третий выходы первого дешифратора являются соответствующими выходами блока.

При этом блок обработки избыточных кодов содержит третий дешифратор, вход которого подключен к первым входам второго и третьего регистров и схемы сравнения и является соответствующим входом .блока, а выход подключен к первому входу коммутатора , второй вход которого соединен с вторым входом схемы сравнения и выходом второго регистра, а выход - 9

блока.

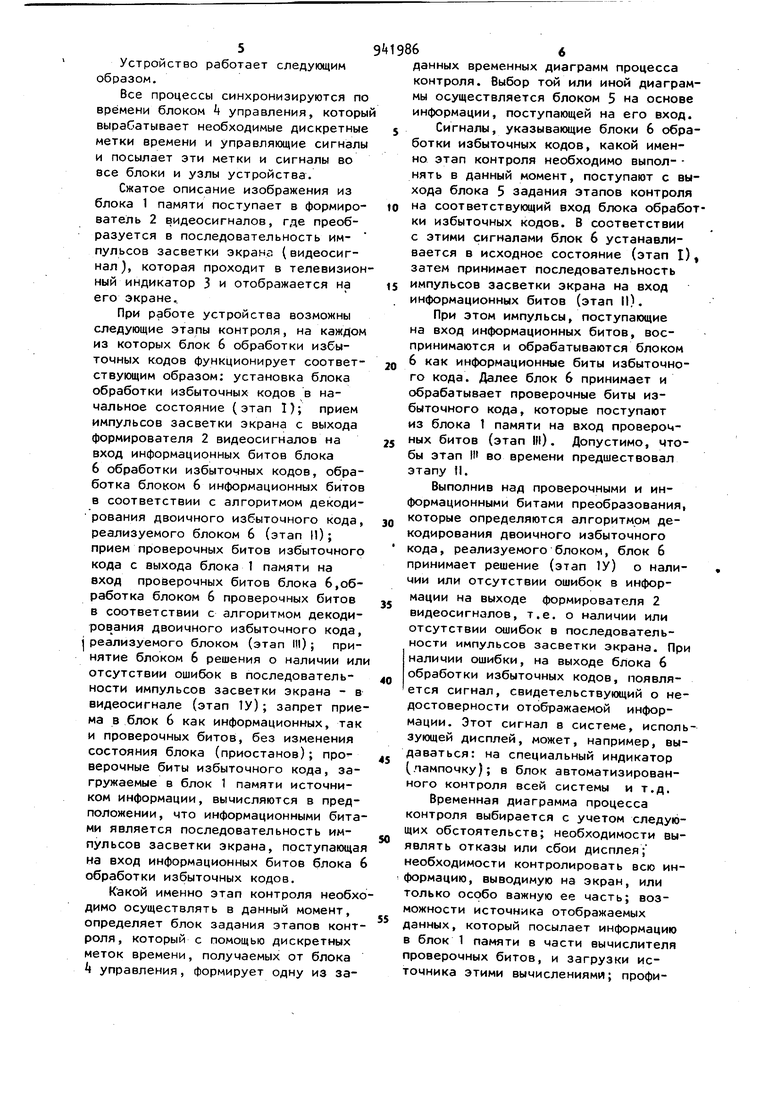

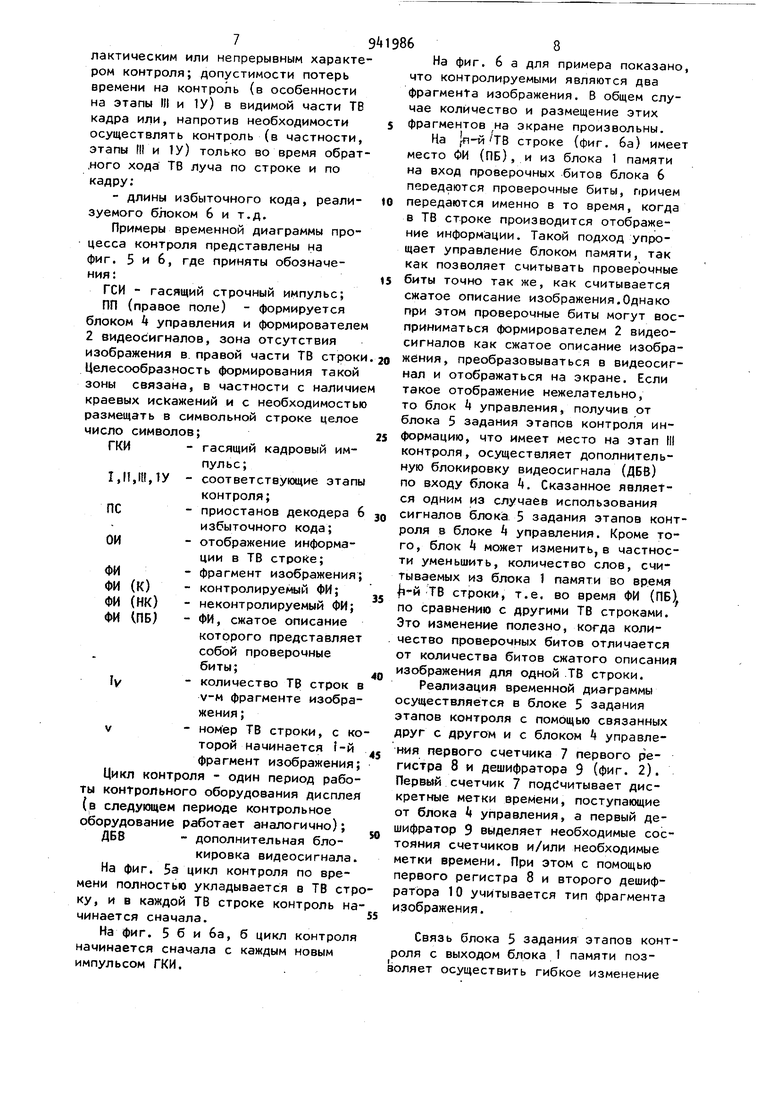

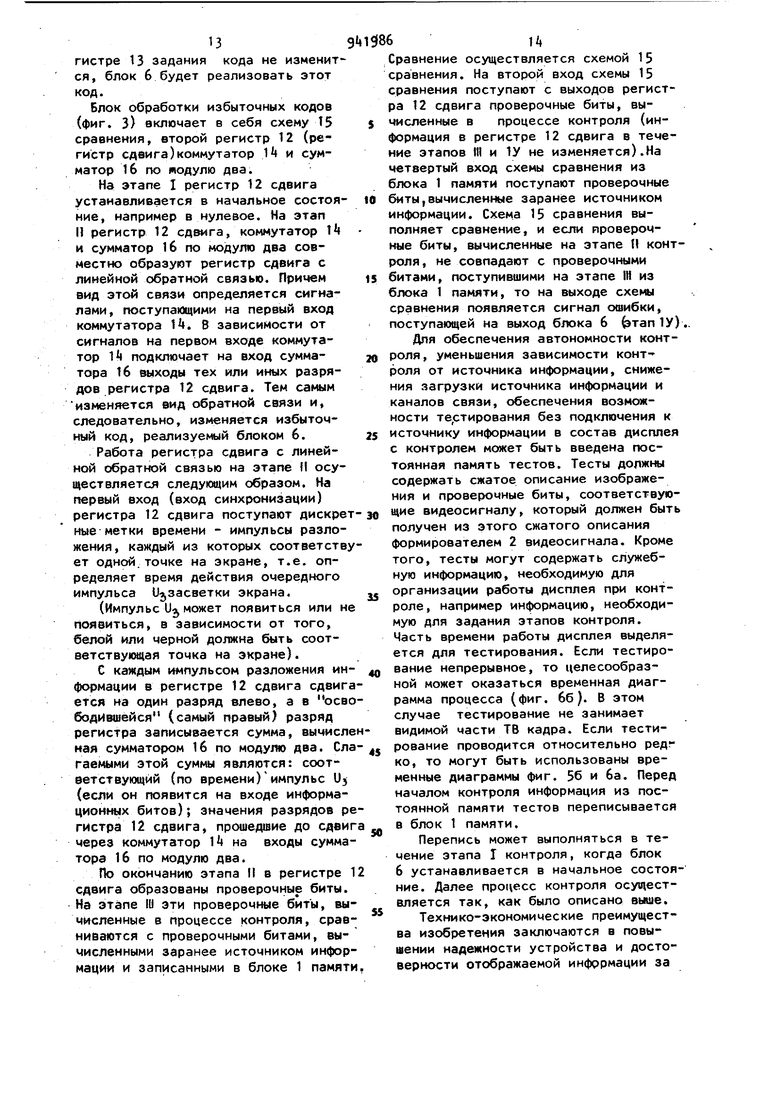

На фиг. 1-6 представлены блок-схема устройства, функциональные схемы блоков устройства и временные диаграммы работы устройства.

Устройство содержит блок 1 памяти, формирователь 2 видеосигналов, телевизионный индикатор 3, блок управления, блок 5 задания этапов контроля, блок 6 обработки избыточных кодов, первый счетС|ик 7, первый регистр 8, первый дешифратор 9, второй дешифратор 10, третий дешифратор 11, второй регистр 12, третий регистр 13) коммутатор It, схему 15 сравнения, сумматор t6 по модулю два, генератор 17 опорной частоты, второй счетчик 18,четвертый дешифратор 19, первый формирователь 20 синхроимпульсов, узел 21 блокировки видеосигналов, второй формирователь 22 синхроимпульсов и третий формирователь 23 синхроимпульсов. 4 с первым входом сумматора по модулю два, второй вход которого является соответствующим входом блока, а выход подключен к второму входу второго регистра, третий вход которого соединен с третьим входом схемы сравнения, вторым входом третьего регистра и является соответствующим входом блока, четвертый вход схемы сравнения подключен к третьему входу третьего, регистра и является соответствущим входом блока, а выход - выходом блока. Кроме того, блок управления содержит последовательно соединенные генератор опорной частоты, второй счетчик и четвертый дешифратор, выход которого подключен к входу первого формирователя синхроимпульсов и первому входу узла блокировки видеосигналов, второй вход которого соединен с первым входом второго формирователя синхроимпульсов и является входом блока,. а третий вход с выходом Третьего формирователя синхроимпульсов и является одним из выходов блока, один из выходов первого формирователя синхросигналов подключен к второму входу второго формирователя синхроимпульсов, третий вход которого соединен с входом третьего формирователя синхроимпульсов и выходу генератора опорной частоты, выходы формирователей синхросигналов и узла блокировки видеосигналов яв;,я,д-гся соответствующими выходами Устройство работает следующим образом. Все процессы синхронизируются по времени блоком 4 управления, которы вырабатывает необходимые дискретные метки времени и управляющие сигналы и посылает эти метки и сигналы во все блоки и узлы устройства. Сжатое описание изображения из блока 1 памяти поступает в формирователь 2 видеосигналов, где преобразуется в последовательность импульсов засветки экрана (видеосигнал), которая проходит в телевизион ный индикатор 3 и отображается на его экране. При работе устройства возможны следующие этапы контроля, на каждом из которых блок 6 обработки избыточных кодов функционирует соответствующим образом; установка блока обработки избыточных кодов в начальное состояние (этап 1); прием импульсов засветки экрана с выхода формирователя 2 видеосигналов на вход информационных битов блока 6 обработки избыточных кодов, обработка блоком 6 информационных битов в соответствии с алгоритмом декодирования двоичного избыточного кода, реализуемого блоком 6 (этап II); прием проверочных битов избыточного кода с выхода блока 1 памяти на вход проверочных битов блока 6,обработка блоком 6 проверочных битов в соответствии с алгоритмом декодиров ания двоичного избыточного кода, I реализуемого блоком (этап III) ; принятие блоком 6 решения о наличии ил отсутствии ошибок в последовательности импульсов засветки экрана - в видеосигнале (этап 1У); запрет прие ма в блок 6 как информационных, так и проверочных битов, без изменения состояния блока (приостанов); проверочные биты избыточного кода, загружаемые в блок 1 памяти источником информации, вычисляются в предположении, что информационными бита ми является последовательность импульсов засветки экрана, поступающа на вход информационных битов блока обработки избыточных кодов, Какой именно этап контроля необх димо осуществлять в данный момент, определяет блок задания этапов конт роля, который с помощью дискретных меток времени, получаемых от блока k управления, формирует одну из заe 6 данных временных диаграмм процесса контроля. Выбор той или иной диаграммы осуществляется блоком 5 на основе информации, поступающей на его вход. Сигналы, указывающие блоки 6 обработки избыточных кодов, какой именно этап контроля необходимо выпол- нять в данный момент, поступают с выхода блока 5 задания этапов контроля на соответствующий вход блока обработки избыточных кодов. В соответствии с этими сигналами блок 6 устанавливается в исходное состояние (этап I) затем принимает последовательность импульсов засветки экрана на вход информационных битов (этап II), При этом импульсы, поступающие на вход информационных битов, воспринимаются и обрабатываются блоком 6 как информационные биты избыточного кода. Далее блок 6 принимает и обрабатывает проверочные биты избыточного кода, которые поступают из блока 1 памяти на вход проверочных битов (этап III). Допустимо, чтобы этап III во времени предшествовал этапу 11, Выполнив над проверочными и информационными битами преобразования, которые определяются алгоритмом декодирования двоичного избыточного кода, реализуемого блоком, блок 6 принимает решение (этап 1У) о наличии или отсутствии ошибок в информации на выходе формирователя 2 видеосигналов, т,е, о наличии или отсутствии ошибок в последовательности импульсов засветки экрана. При наличии ошибки, на выходе блока 6 обработки избыточных кодов, появляется сигнал, свидетельствующий о недостоверности отображаемой информации. Этот сигнал а системе, использующей дисплей, может, например, выдаваться: на специальный индикатор (лампочку); в блок автоматизированного контроля всей системы и т,д. Временная диаграмма процесса контроля выбирается с учетом следующих обстоятельств; необходимости выявлять отказы или сбои дисплея; необходимости контролировать всю информацию, выводимую на экран, или только особо важную ее часть; возможности источника отображаемых данных, который посылает информацию в блок 1 памяти в части вычислителя проверочных битов, и загрузки источника этими вычислениями; профи7лактическим или непрерывным характе ром контроля; допустимости потерь времени на контроль (в особенности на этапы III и 1У) в видимой части ТВ кадра или, напротив необходимости осуществлять контроль (в частности, этапы III и 1У) только во время обрат .ного хода ТВ луча по строке и по кадру; - длины избыточного кода, реализуемого блоком 6 и т.д. Примеры временной диаграммы процесса контроля представлены на фиг. 5 и 6, где приняты обозначения:геи - гасящий строчный импульс; ПП (правое поле) - формируется блоком 4 управления и формирователе 2 видеосигналов, зона отсутствия изображения в правой части ТВ строки Целесообразность формирования такой зоны связана, в частности с наличием краевых искажений и с необходимостью размещать в символьной строке целое число символов; ГКИ -гасящий кадровый импульс;I,lf,ltl,iy - соответствующие этапы контроля; -приостанов декодера 6 избыточного кода; -отображение информации в ТВ строке; -фрагмент изображения; ФИ(К) -контролируемый ФИ; ФИ(НК) -неконтролируемый ФИ; ФИ(ПБ) -ФИ, сжатое описание которого представляет собой проверочные биты; -количество ТВ строк в V-M фрагменте изображения ; V - номер ТВ строки, с ко торой начинается i-й фра гмент изображения; Цикл контроля - один период работы контрольного оборудования дисплея (в следующем периоде контрольное оборудование работает аналогично); ДБВ - дополнительная блокировка видеосигнала. На фиг. 5з цикл контроля по времени полностью укладывается в ТВ стр ку, и в каждой ТВ строке контроль на чинается сначала. На фиг. 5 б и 6а, б цикл контроля начинается сначала с каждым новым импульсом ГКИ. 6 На фиг. 6 а для примера показано, что контролируемыми являются два фрагмента изображения. В общем случае количество и размещение этих фрагментов .на экране произвольны. На (fi-й/ТВ строке (фиг. 6а) имеет место ФИ (ПБ), и из блока 1 памяти на вход проверочных битов блока 6 пеоедаются проверочные биты, причем передаются именно в то время, когда в ТВ строке производится отображение информации. Такой подход упрощает управление блоком памяти, так как позволяет считывать проверочные биты точно так же, как считывается сжатое описание изображения.Однако при этом проверочные биты могут восприниматься формирователем 2 видеосигналов как сжатое описание изображения, преобразовываться в видеосигнал и отображаться на экране. Если такое отображение нежелательно, то блок Ц управления, получив от блока 5 задания этапов контроля информацию, что имеет место на этап II контроля, осуществляет дополнительную блокировку видеосигнала (ДБВ) по входу блока 4. Сказанное является одним из случаев использования сигналов блока 5 задания этапов контроля в блоке управления. Кроме того, блок может изменить, в частности уменьшить, количество слов, считываемых из блока 1 памяти во время ч-й ТВ строки, т.е. во время ФИ (ПБ) по сравнению с другими ТВ строками. Это изменение полезно, когда количество проверочных битов отличается от количества битов сжатого описания изображения для одной ТВ строки. Реализация временной диаграммы осуществляется в блоке 5 задания этапов контроля с помощью связанных друг с другом и с блоком f управления первого счетчика 7 первого регистра 8 и дешифратора 9 (фиг. 2). Первый счетчик 7 подсчитывает дискретные метки времени, поступающие от блока i управления, а первый дешифратор 9 выделяет необходимые состояния счетчиков и/или необходимые метки времени. При этом с помощью первого регистра 8 и второго дешифратора 10 учитывается тип фрагмента изображения. Связь блока 5 задания этапов контроля с выходом блока 1 памяти позоляет осуществить гибкое изменение 9 временной диаграммы контроля в процессе функционирования дисплея. Работа блока 5 (фиг. 5) рассматривается на примере реализации временной диаграммы процесса контроля (фиг. 6а). Изображение в этом случа разделяется на фрагменты (ФИ), каждый из которых включает целое число ТВ строк, i-му фрагменту изо ражения в блоке 1 памяти соответствует следующая информация: А. i-e управляющее слово, включающее: - длину -го фрагмента изображения (количество ТВ строк в i-M ФИ);, код типа i-ro фрагмента изображения(ФИ (К), ФИ (НК), ФИ (ПБ), необходимость ДБВ). Б. i-й фрагмент сжатого описания изображения.. Пример кодирования типа фрагмента изображения приведен в таблице (сокращения такие же, как на фиг.ба).

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Устройство для контроля видеосигнала | 1982 |

|

SU1069190A1 |

| Устройство для вывода графической информации | 1988 |

|

SU1615787A1 |

| Устройство для вывода графической информации | 1988 |

|

SU1615786A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство для воспроизведения изображения | 1980 |

|

SU1085014A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1984 |

|

SU1354181A1 |

| Устройство для исправления ошибок в блоках памяти | 1983 |

|

SU1100639A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

Контролируемый фрагмент и ображения (ФИ) без дополнительной блокировки видеосигнала (ДБВ) ФИ Контролируемый ФИ с ДБВ Неконтролируемый ФИ без ДБВ ФИ, сжатое описание которого представляет собой проверочные биты (с ДБВ) -ФИ

в дисплее может быть предусмотрено изменение режима отображения информации (смена масштабов,изменение способа сжатия изображения, изменение количества знакомест в строке и т.д.). В этом случае изменение режима отображения удобно осуществлять в начале нового фрагмента изображение. В частности можно включать в i-e управляющее слово код режима отображения i-ro фрагмента.

Временная диаграмма (фиг. 6а) реализуется следующим образом. Импульс ГКИ поступает из блока управления на вход синхронизации блока 5 задания этапов контроля и выделяется первым дешифратором 9, который в течение действия ГКИ выдает на выходе блока 5 задания этапов контроля информацию о том, что имеет место этап 1 процесса контроля. ГКИ на вход синхронизации из блока управления (в числе прочих необходимых импульсов) поступают импульсы геи и импульсы, соответствующие ПП. Импульс геи и импульс ПП выделяются первым дешифратором, который в течение действия этих импульсов (независимо от типа фрагмента) выдает на ФИ ФИ

ВЫХОД блока 5 информацию о том, что имеет место приостанов блока 6. Исключение составляет импульс ПП во время фрагмента ФИ (ПБ), когда первым дешифратором 9 выдается сигнал о том, что имеет место этап 1У.

Во время первого (после окончания ГКИ) импульса ГСИ из блока 1 памяти в блок 5 задания этапов контроля загружается t-e управляющее

слово, при этом код типа 1-го фрагмента загружается в первый регистр (регистр типа фрагмента), а длина Т 1-го фрагмента в первый счетчик 7 (счетчик длины фрагмента).

Счетчик 7 длины фрагмента, получая на счетный вход из блока импульсы ГСИ, вырабатывает через L ТВ строк сигнал, что 1-й фрагмент закончен. Этот сигнал поступает в регистр 8 типа фрагмента и первый дешифратор 9 который сообщает об окончании фрагмента блоку k управления. Во время (Ц+ 1)-го импульса ГСИ из блока 1 памяти в блок 5 задания этапов контроля загружается 2-е управляющее слово (код типа 2-го фрагмента загружается в регистр 8). Через ТБ строк после второй за(К) 00 (К,БВ) 01 (НК) 10 (ПБ) 11 грузки счетчик 7 длины фрагмента вырабатываег сигнал, что 2-й фрагмент закончен, и в блок 5 во время(Ц + + 1/1 - 1)-го импульса ГСИ загружается 3-е управляющее слово. Загрузка последующих управляющих слов в блок 5 производится аналогично - счетчик 7, имея соответствующее начальное состояние и получая на счетный вход импульсы ГСИ, вырабатывает через 1{ ТВ строк после начала i-ro фрагмента сигнал об окончании i-ro фраг мента. Во время первого ГСИ после этого сигнала в блок 5 загружается ( + 1)-е управляющее слово. Таким образом, в течение действия каждого ФИ в регистре 8 типа фрагмента хранится код типа этого ФИ. Код типа фрагмента дешифрируется вторым дешифратором 10 (дешифратором типа фрагмента). Результаты дешифрации поступают в первый дешифратор 9, ко торый, используя эти результаты и получая от блока Ц управления импул сы, соответствующие ПП, ОИ и ГСИ, формирует и выдает на выходы блока 5 задания этапов контроля информации о том, что имеет место этап II или III или 1У процесса контроля (см. таблицу). Кроме того, первый дешифратор 9 выдает блоку Ц управления информацию о необходимости дополнительной блокировки видеосигнала во время ОИ (для типов 01, 11). Отметим, что ДБВ для фрагмента ФИ (к, БВ) может быть целесообразна если это - специальный тестовый фра1 мент, несообщающий оператору информации. Вместо количества 1 ТВ строк в (-М фрагменте изображения в счетчик длины фрагмента можно загружать (в качестве длины фрагмента) количес во слов блока 1 памяти, составляющих f-й фрагмент сжатого описания изображения. В этом случае на отчетный вход счетчика 7 необходимо подавать из блока t импульсы, опрашивающие блок 1 памяти. Структура блока 5 ост нется такой же. Рассмотрим работу блока 4 управления (фиг. Ц). Генератор 17 опорной частоты, второй счетчик 18 и четвертый дешифратор 19 в совокупности позволяют получить метки времени, по которым первый формирователь 20 синхроимпульсов вырабатывает ТВ синхроимпульсы ХГКИ, ГСИ, второй формирова тель 22 синхроимпульсов вь(дает коман на обращение к блоку 1 памяти, а третий формирователь 23 синхроимпульсов вырабатывает импульсы разложения по строке. Узел 21 блокировки видеосигналов блокирует видеосигнал во время обратного хода луча по строке и по кадру, а также по сигналу, поступающему на его вход. Второй ормирователь 22 синхроимпульсов в своей работе также учитывает этапы контроля. Для повышения вероятности обнаруеиия ошибки в последовательности импульсов засветки экрана и, следовательно, для повышения достоверности отображения информации целесообразно заложить в блок 6 возможность реализации не одного, а двух и более различных избыточных кодов. Указанные коды могут быть ориентированы на обнаружение ошибок разных типов, например один код ориентирован на обнаружение независимых ошибок, а другой - на обнаружение пакетов ошибок. Для реализации указанной возможности блок б содержит(фиг. 5) третий регистр 13 (регистр задания кода ) и третий дешифратор 11 (дешифратор кода). При этом из блока 1 памяти третий регистр 13 в определенные моменты времени, задаваемые блоком Ц управления и блоком 5, получают информацию, позволяющую этому узлу решить, какой именно код (из заложенных в блок 6) следует реализовать в данный момент. Рассмотрим процесс выбора кода блоком 6 для примера в случае, KOI- да реализуется временная диаграмма прюцесса контроля вида рис.ба. В этом случае в i-e управляющее слово, кроме информации о длине и типе фрагмента, вводится номер реализуемого кода. 3 момент, ко;-да блок 5 задания этапов контроля загружается длина код типа i-ro фрагмента, в регистр 13 задания кода загружается часть управляющего слова, являющегося номером кода, который нужно реализовать во время i-ro фрагмента. Момент загрузки определяется в блоке 5 задания этапов контроля и сообщается на второй вход регистра 13 задания кода. Дешифратор 11 выбора кода преобразует номер кода в вид, удобный для управления коммутатором И. До тех пор, пока номер кода в регистре 13 задания кода не изменит ся, блок 6 будет реализовать этот код. Блок обработки избыточных кодов (фиг. З) включает в себя схему 15 сравнения, второй регистр 12 (регистр сдайга)коммутатор 14 и сумматор 16 по иодулю два. Нз этапе I регистр 12 сдвига устанавливается в начальное состояние, например в нулевое. На этап П регистр 12 сдвига, коммутатор I и сумматор 16 по модулю два совместно образуют регистр сдвига с линейной обратной связью. Причем вид этой связи определяется сигналами, поступающими на первый вход коммутатора 14. В зависимости от сигналов на первом входе коммутатор 14 подключает на вход сумматора 16 выходы тех или иных разрядов регистра 12 сдвига. Тем самым изменяется вид обратной связи и, следовательно, изменяется избыточный код, реализуемый блоком 6. Работа регистра сдвига с линейной обратной связью на этапе II осуществляется следущим образом. На первый вход (вход синхронизации) регистра 12 сдвига поступают дискре ные метки времени - импульсы разложения, каждый из которых соответств ет одной.точке на экране, т.е. определяет время действия очередного импульса и засветки экрана. (Импульс иJ может появиться или н появиться, в зависимости от того, белой или черной должна быть соответствующая точка на экране). С каждым импульсом разложения ин формации в регистре 12 сдвига сдвиг ется на один разряд влево, а в осв бодившейся (самый правый) разряд регистра записывается сумма, вычисл ная сумматором 16 по модулю два. Сл гаемыми этой суммы являются: соответствующий (по времени)импульс 1)5 (если он появится на входе информационных битов); значения разрядов р гистра 12 сдвига, прошедшие до сдви через коммутатор 14 на входы сумма тора 16 по модулю два. По окончанию этапа II в регистре сдвига образованы проверочные биты. На этапе Ш эти проверочные биты, вы численные в процессе контроля, срав ниваются с проверочными битами, вычисленными заранее источником инфор мации и записанными в блоке 1 памят Сравнение осуществляется схемой 15 сравнения. На второй вход схемы 15 сравнения поступают с выходов регистра 12 сдвига проверочные биты, вычисленные в процессе контроля (информация в регистре 12 сдвига в течение этапов Ш и 1У не изменяется).На четвертый вход схемы сравнения из блока 1 памяти поступают проверочные ,вычисленные заранее источником информации. Схема 15 сравнения выполняет сравнение, и если проверочные биты, вычисленные на этапе II контроля, не совпадают с проверочными битами, поступившими на этапе 1Н из блока 1 памяти, то на выходе cxeMJ сравнения появляется сигнал ошибки, поступающей на выход блока 6 тап 1У).. Для обеспечения автономности контроля, уменьшения зависимости конт- роля от источника информации, снижения загрузки источника информации и каналов связи, обеспечения возможности те стирования без подключения к источнику информации в состав дисплея с контролем может быть введена постоянная память тестов. Тесты должны содержать сжатое описание изображения и проверочные биты, соответствующие видеосигналу, который должен быть получен из этого сжатого описания формирователем 2 видеосигнала. Кроме того, тесты могут содержать служебную информацию, необходимую для организации работы дисплея при контроле, например информацию, необходимую для задания этапов контроля. Часть времени работы дисплея выделяется для тестирования. Если тестирование непрерывное, то целесообразной может оказаться временная диаграмма процесса (фиг. 6б). В этом случае тестирование не занимает видимой части ТВ кадра. Если тестирование проводится относительно редг ко, то могут быть использованы временные диаграммы фиг. 56 и 6а. Перед началом контроля информация из постоянной памяти тестов переписывается в блок 1 памяти. Перепись может выполняться в течение этапа I контроля, когда блок 6 устанавливается в начальное состояние. Далее процесс контроля осуществляется так, как было описано выше. Технико-экономические преимущества изобретения заключаются в повышении надежности устройства и достоверности отображаемой информации за 15 счет более полного охвата контролем оборудования дисплея. Формула изобретения 1.Устройство для контроля диспл содержащее последовательно соединенные блок памяти, формирователь видеосигналов и телевизионный индикатор, управляющие входы которых подключены к соответствующим выходам блока управления, отличаю Д е е с я тем, что, с целью повышения надежности устройства и достоверности отображаемой информации, оно содержит блок задания этапов контроля, соединенный двухсторонней связью с блоком управления, вход которого подключен к выходу блока памяти, и блок обработки избыточных кодов, входы которого соединены с в ходами блока памяти, формирователя видеосигналов, блока задания этапов контроля и соответствующим выходом блока управления. 2.Устройство по п. 1, о т л ичающееся тем, что блок задания этапов контроля содержит первый счетчик, первый вход которого соединен с первым входом первого регистра и является соответствующим входом блока, второй вход подключен к второму входу первого регистра и первому выходу,первого дешифратора, второй вход которого соединен с тре тьим входом первого регистра, первы входом второго дешифратора и является соответствующим входом блока, третий вход подключен к четвертому входу первого регистра и выходу пер вого счетчика, а четвертый вход к выходу второго дешифратора, второ вход которого соединен с выходом пе вого регистра, а второй и третий вы ходы первого дешифратора являются соответствующими выходами блока. 3.Устройство по п. 1, о т л и чающееся тем, что блок обработки избыточных кодов содержит третий дешифратор, вход которого по ключен к первым входам второго и e третьего регистров и схемы сравнения и является соответствующим входом блока, ё выход подключен к первому входу коммутатора, второй вход которого соединен с вторым входом схемы сравнения и выходом второго регистра, а выход - с первым входом сумматора по модулю два, второй вход которого является соответствующим входом блока, а выход подключен к второму входу второго регистра, третий вход которого соединен с третьим входом схемы сравнения, вторУм третьего регистра и является соответствующим входом блока, четвертый вход схемы сравнения подключен к третьему входу третьего регистра и является соответствующим входом блока, а выход - выходом блока. 4. Устройство по п. 1, о т л и чающееся тем, что блок управления содержит последовательно соединенные генератор опорной частоты, второй счетчик и четвертый дешифратор, выход которого подключен к входу первого формирователя синхроимпульсов и первому входу узла блокировки видеосигналов, второй вход которого соединен с первым входом второго формирователя синхроимпульсов является входом блока, а третий вход - с гыходом третьего формирователя синхроимпульсов и является одним из выходов блока, один из выходов первого формирователя синхросигналов подключен к второму входу формирователя синхроимпульсов, третий вход которого соединен с входом третьего формирователя синхроимпульсов и выходом генератора опорной частоты, выходы формирователей синхросигналов и узла блокировки видео сигналов являются соответствующими выходами блока. Источники информации, принятые во внимание при экспертизе 1.Патент Японии № , кл. 97/7, 1979. 2.Авторское свидетельство СССР № 55l6i 5, кл. G 06 К 15/20, 197 (прототип).

Фиг. 2

фиг. i.

Авторы

Даты

1982-07-07—Публикация

1980-04-29—Подача