135А

Цель достигается введением в устройство шинного формирователя 16, блока 9 управления, дешифратора 23, вычитающего счетчика 22 триггера 7, блока 10 памяти программ п графики символов, блока 11 памяти кодов символов и 1ультиплексора 6 и соответст- в ующих функциональных связей, В уст- /ройстве имеется возможность изменения матриф разложения символа, что су

Изобретение относится к,вычислительной технике и мозкет быть исполь-- зовано при разработке универсальных устройств отображения знаковой и графической информации.

Цель изобретения - расширение области применения устройства путем возможности отображения информации с оперативно-изменяемыми параметрами растра.

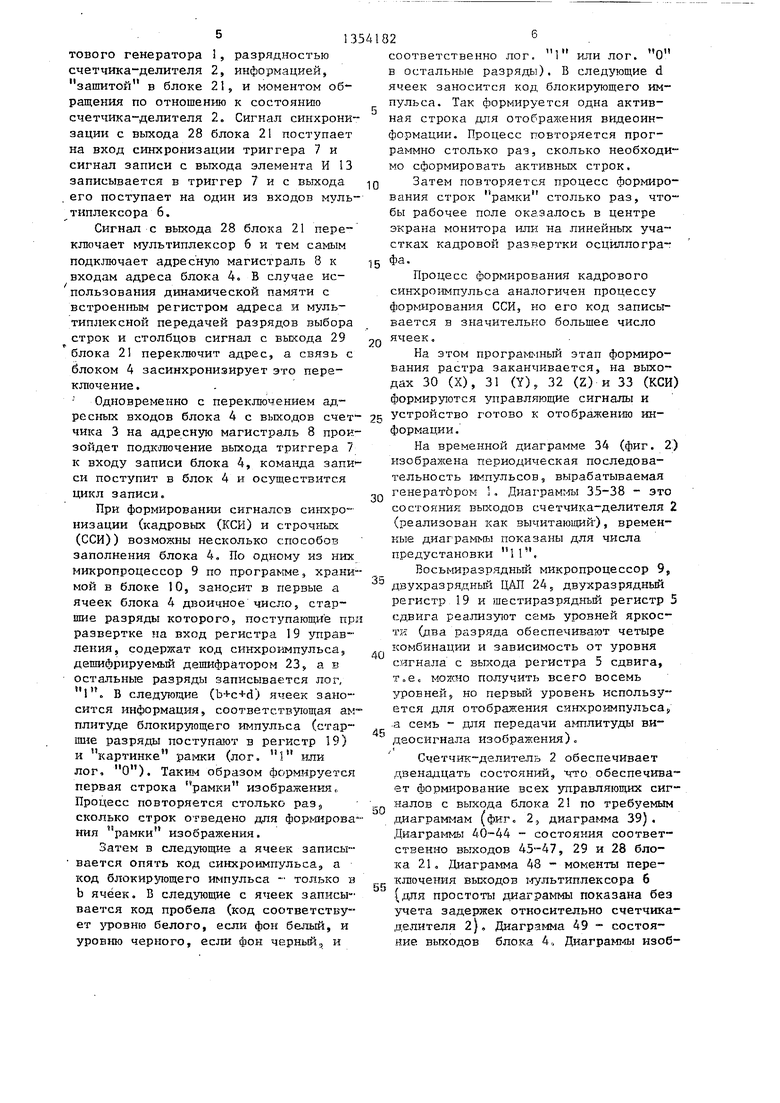

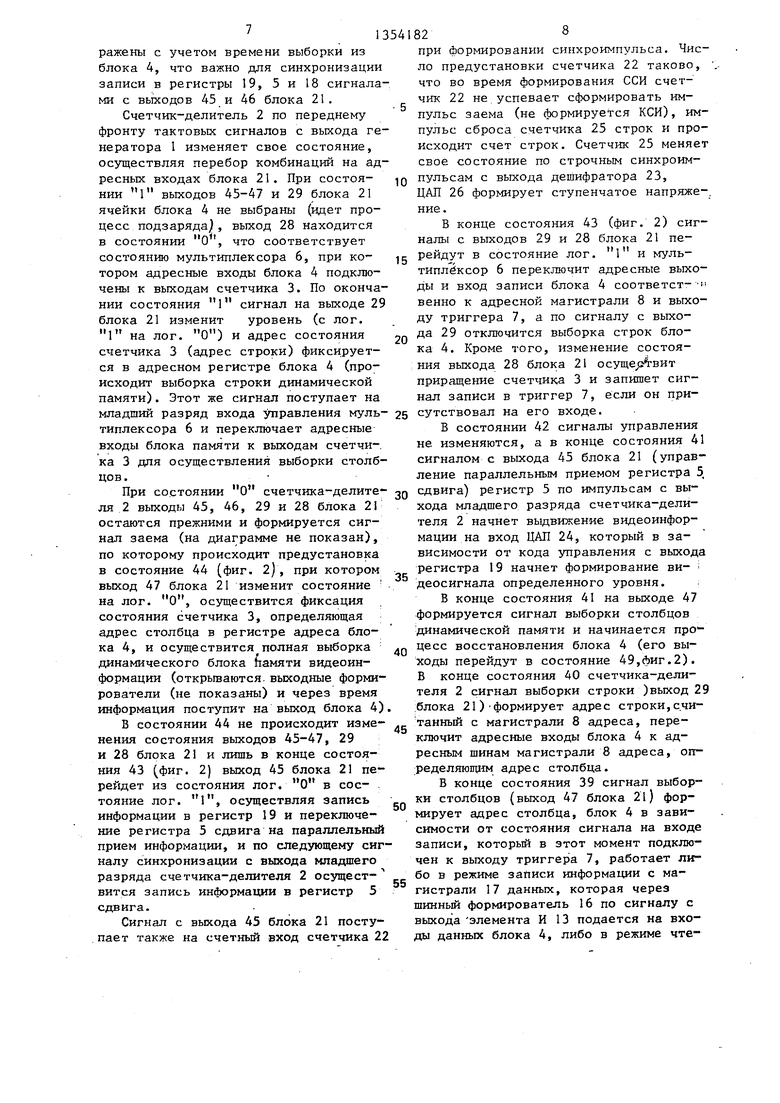

На фиг.1 представлена функциональная схема устройства; на фиг.2 - вре- меь;кые диаграммы рэ.боты устройства.

Устройство содержит тактовый генератор 1, двоичный счетчик - делитель частоты, счетчик 3 знаков, строк и рядов, блок 4 памяти видеоинформации регистр 5 сдвига, мультиплексор 6, триггер 7 (D-триггер), адресную магистраль 8., блок 9 управления (микропроцессор), блок 10 памяти прог- и графики символов, блок I I, па- M5iTH кодов символов, селектор 12 адреса, элементы И 13 и 14., шину 15 записи ншнный формирователь 16, магистраль 17 данньж, регистры 18 и 19э И1ину 20 готовностм, блок 21 синхронизации, вычитающий счетчик 22, дешифратор 23, цифреаналоговьш преобразователь (ЦАП) 24, счетчик 25 строк, ЦДЛ 26, источник 27 опорного напряжения .

Тактовы-й генератор 1 вырабатывает- прямоугольные импульсы с частотой следования F () Гц, где № число ячеек блока 4 памяти ви,цеоин- формации, М - число бит информации в слове блока 4 памяти видеоинформации несутчкгк; 1« формаци о о видеосигнале (разрядность регистра 5 сдвига), К82

щественно повышает гибкость устройства (позволяет отображать буквы различных алфавитов и иероглифы), улучшает эргономические характеристики, а возможность программного изменения п&раметров растра позволяет использовать устройство практически с любыми мониторами. Использующими растровую развертку, и осцшшографами, 2 ил.

5

5

максимальная частота кадров или полукадров .

Множитель 2 присутствует в формуле по той причине, что цикл обращения к блокз 4 состоит из двух циклов: цикла считывания информации в регистр 5 сдвига и цикла передачи или приема информации из (или в)1 блока 9 управления.

Такор повышение частоты тактового генератора несколько повьшает требование к параметрам отдельных блоков, но в то же время гарантирует вы сокое качество изображения, так как процесс обмена информацией с микропроцессором 9 не влияет на процесс отображения информации.

Разрядность счетчика-делителя 2 частоты, выполненного в виде сч етчи- ка, и объем паг-шти блока 21 зависят от типа используемой памяти видеоинформации ,

Разрядность счетчика 3 знаков, строк и рядов определяется как логарифм по основанию два от числа ячеек в блоке 4 требуемьй объем которого рассчитывается по формуле

NE (а+Ы-c+d) (e+f+g+j),

N - число ячеек памяти блока 4;

Cjd-- числа ячеек блока 4, отведенных для фор дарования строчного синхроимпульса максимальной длительности, левого бланкирующего импульса ма1 симальной длительности,правого бланкирующего импульса максимахсь- ной длительное-ЕЙ 5 строки видеосигнала соответственно

313

(таким образом, сумма а,Ь, c,d - максимальное число ячеек блока 4, отведенных для формирования строки видеосигнала, синхронизирующих и бланкирующих строчны импульсов);

е - число рабочих строк монитора с максимальным числом рабочих строк;

f - число строк, используемых для формирования местоположения нижней рабочей строки на экране монитора (мак симальное);

g - число строк, используемых для задержки формирования изображения, для исключения нелинейности кадровой раз- вертки (максимальное); j - число строк, используемых для формирования кадрового синхроимпульса.Разрядность регистра 5 сдвига вы- бирается такой, чтобы в сумме с разрядностью регистра 19 получилась разрядность микропроцессора 9. Разрядность регистра 19 равна целому числу N 1о§2(К + 2), где К - число необ- ходимых градаций яркости, слагаемое 2 резервирует два уровня для формирования синхронизирующих и бланкирующих импульсов (N должно быть увеличено до ближайшего целого числа). Число дис- кретизации ЦАП 24 видеосигнала равно (К + 2), где К - число градаций яркости.

.Дешифратор 23 осуществляет выбор одного значения из (К +2). Число предустановки вычитающего счетчика 22 равно 1, при этом должно выполняться условие L а, где а - число ячеек 1 блока 4, отведенных для формирования строчного синхроимпульса максималь- ной длительности.

Разрядность счетчика 25 строк равна N iogi(e + f + g + j) (N должно быть увеличено до ближайшего целого числа, ае, f, g, j определены выше),

Число дискретизаций ЦАП 26 (вертикального отклонения) должно быть равно сумме е, f, g, j. Разрядность регистра 18 (данных) равна разрядности микропроцессора 9 и блока 4.

Работу устройства можно разбить на этапы: задание режима работы, формирование растра и отображение инфор- маци11.

5

1

to

15

0

25 О g

О

п

5

82

При включении питания микропроцессор 9 начинает выполнять программу инициализации, считывая коды команд из блока 10. Микропроцессор 9 под управлением программы инициализации опрашивает состояние переключателей (не показаны) или осуществляет переход на задания стандартного режима работы. Задание стандартного режима работы или задание режима работы после анализа состояния переключателей режима включает задание параметров растра (а, Ь, с, d, е, f, g, j) и за,дания состояния регистра состояния (его роль может выполнять один из регистров общего назначения микропроцессора либо одна из ячеек ОЗУ, .которое может входить в состав микропроцессора или подключено к нему обычным образом и поэтому не показано).

Регистр состояния может иметь следующие поля: поле кода яркости и поле признаков режима отображения (позитив/негатив, мигания, цвет, код матрицы разложения 1ши код графичес- кого дисплея и т.д.) . После задания режима работы микропроцессор 9 пере- , ходит на программу формирования растра, которая осуществляется путем заполнения блока 4 по программе, хранящейся в блоке 10, вид которой зависит, от параметров растра . и состояния регистра состояния.

Запись информации в блок 4 осуществляется следующим образом.

Микропроцессор 9 выставляет на адресную магистраль 8 адрес, а на магистраль 17 данных - информацию, предназначенную дпя записи. Селектор 12 адреса при совпадении адреса блока 4 памяти видеоинформации с адресом, установленным на адресной магистрали 8, вырабатывает сигнал выбора, который с выхода селектора 12 адреса поступает на входы элементов И 13 и 14,разрешая тем самым прохождение сигнала по второму входу.

Микропроцессор 9 после выставки адреса и данных переводит шину 15 записи в активное состояние, подавая , тем самым команду записи, которая проходит через элемент И 13 и с выхода его поступает на D-вход триггера 7 и переключает шинный формирователь 16 в режим передачи информации с магистрали 17 данных на входы блока 4 через время, определяемое частотой та.

тового генератора 1, разрядностью

четчика-делителя 2, информацией, зашитой в блоке 21, и моментом обащения по отношению к состоянию четчика-делителя 2. Сигнал синхрониации с выхода 28 блока 21 поступает а вход синхронизации триггера 7 и сигнал записи с выхода элемента И 13 записывается в триггер Тис выхода его поступает на один из входов мультиплексора 6.

Сигнал с выхода 28 блока 21 переключает мультиплексор б к тем самым подключает адресную магистраль 8 к входам адреса блока 4. В случае использования динамической памяти с встроенным регистром адреса и мультиплексной передачей разрядов выбора строк и столбцов сигнал с выхода 29 блока 21 переключит адрес, а связь с блоком 4 засинхронизирует это переключение.

Одновременно с переключением адресных входов блока 4 с выходов счетчика 3 на адресную магистраль 8 произойдет подключение выхода триггера 7 к входу записи блока 4, команда си поступит в блок 4 и осуществится цикл записи.

При формировании сигналов синхронизации (кадровых (КСИ) и строчных (ССИ)) возможны несколько способов заполнения блока 4, По одному из них микропроцессор 9 по программе, хранимой в блоке 10, зано.сит в первые а ячеек блока 4 двоичное число, старшие разряды которого, поступающие при развертке на вход регистра 19 управления, содержат код синхроимпульса, дешифрируемый дешифратором 23, а в остальные разряды записывается лог, l. В следующие (b+c+d) ячеек заносится информация, соответствутащая ак плитуде блокирующего импульса (стар- шне разряды поступают в регистр 19) и картинке рамки (лог, l или лог, о). Таким образом формируется первая строка рамки изображения. Процесс повторяется столько разд сколько строк отведено для формирования рамки изображения.

Затем в следующие а ячеек записы- вается опять код синхроимпульса, а код блокир пощего импульса - только в b ячеек. В следующие с ячеек записывается код пробела (код соответствует фовню белого, если фон белый, и уровню черного, если фон черный, и

54182°

соответственно лог. 1 или лог. О в остальные разряды). В следующие d ячеек заносится код блокирующего импульса. Так формируется одна активная строка для отображения видеоинформации. Процесс повторяется программно столько раз, сколько необходимо сформировать активных строк.

Затем повторяется процесс формиро20

30

10

вания строк рамки столько раз, чтобы рабочее поле оказалось в центре экрана монитора или на линейных участках кадровой развертки осциллогра15 Ф Процесс формирования кадрового

синхроимпульса аналогичен процессу формирования ССИ, но его код записывается в значительно большее число ячеек.

На этом программный этап формирования растра заканчивается, на выходах 30 (X), 31 (Y), 32 (Z) и 33 (КСИ) формируются управляющие сигналы и

2 устройство готово к отображению информации.

На временной диаграмме 34 (фиг. 2.) изображена периодическая последовательность импульсов, вырабатываемая генератором 1. Диаграмг-гы 35-38 - это состояния выходов счетчика-делителя 2 (реализован как вычитающий ), временные диаграммы показаны для числа предустановки П,,

Восьмиразрядный микропроцессор 9,

двухразрядньй ЦАП 24, двухразрядный регистр 19 и шестиразряднь регистр 5 сдвига реализуют семь уровней яркости (два разряда обеспечивают четыре комбинации и зависимость от уровня сигнала с выхода регистра 5 сдвига, т.вс можно получить всего восемь уровней5 но первый уровень используется для отображения с-япкроумпулъса, .а семь - для передачи амплитуды ви- деосигнала изображения).

Счетчик-делитель 2 обеспечивает двенадцать состоян™, что обеспечивает формирование всех управляющих сиг налов с выхода блока 21 по требуемым ,циаграм1чам (фиг. 2, диаграмма 39) . Диаграммы 40-44 - состояния соответ™ ственно выходов 45-47, 29 и 28 блока 21. Диаграмма 48 - моменты переключения вьЕсодов 1-гультиплексора б (для простоты диаграмьш показана без учета задержек относительно счетчика- делителя 2), Диаграмма 49 - состояние выходов блока 4, Диаграм1« 1 изоб55

1

ражены с учетом времени выборки из блока 4, что важно для синхронизации записи в регистры 19, 5 и 18 сигналами с выходов 45 и 46 блока 21.

Счетчик-делитель 2 по переднему фронту тактовых сигналов с выхода генератора 1 изменяет свое состояние, осуществляя перебор комбинаций на адресных входах блока 21. При состоя- НИИ 1 вькодов 45-47 и 29 блока 21 ячейки блока 4 не выбраны (идет процесс подзаряда , выход 28 находится в состоянии О , что соответствует состоянию мультиплексора 6, при ко- тором адресные входы блока 4 подключены к выходам счетчика 3. По окончании состояния 1 сигнал на выходе 29 блока 21 изменит уровень (с лог. 1 на лог. О) и адрес состояния счетчика 3 (адрес строки) фиксируется в адресном регистре блока 4 (происходит выборка строки динамической памяти). Этот же сигнал поступает на младший разряд входа управления муль- типлексора 6 и переключает адресные входы блока памяти к выходам счетчи-. ка 3 для осуществления выборки столбцов.

При состоянии о счетчика-делите- ля 2 выходы 45, 46, 29 и 28 блока 21- остаются прежними и формируется сигнал заема (на диаграмме не показан), по которому происходит предустановка в состояние 44 (фиг. 2, при котором выход 47 блока 21 изменит состояние на лог. О, осуществится фиксация состояния счетчика 3, определяющая адрес столбца в регистре адреса блока 4, и осуществится полная выборка динамического блока памяти видеоинформации (открьтаются. выходные формирователи (не показаны) и через время информация поступит на выход блока 4) В состоянии 44 не происходит изменения состояния выходов 45-47, 29 и 28 блока 21 и лишь в конце состояния 43 (фиг. 2) выход 45 блока 21 перейдет из состояния лог. О в сое- . тояние лог. 1, осуществляя запись информации в регистр 19 и переключение регистра 5 сдвига на параллельный прием информации, и по следующему сигналу синхронизации с выхода младшего разряда счетчика-делителя 2 осущест- вится запись информации в регистр 5 сдвига.

Сигнал с выхода 45 блока 21 поступает также на счетньй вход счетчика 22

IQ 1g 2о 25

о Q .

45

5

1828

при формировании синхроимпульса. Число предустановки счетчика 22 таково, что во время формирования ССИ счетчик 22 не успевает сформировать импульс заема (не формируется КСИ), импульс сброса счетчика 25 строк и происходит счет строк. Счетчик 25 меняет свое состояние по строчным синхроимпульсам с выхода дешифратора 23, ЦАП 26 формирует ступенчатое напряже-. нне.

В конце состояния 43 (фиг. 2) сигналы с выходов 29 и 28 блока 21 перейдут в состояние лог. l и мультиплексор 6 переключит адресные выходы и вход записи блока 4 соответст- венно к адресной магистрали 8 и выходу триггера 7, а по сигналу с выхода 29 отключится выборка строк блока 4. Кроме того, изменение состояния выхода 28 блока 2 осуще,(Лвит приращение счетчика 3 и запишет сигнал записи в триггер 7, если он присутствовал на его входе.

В состоянии 42 сигналы управления не изменяются, а в конце состояния 41 сигналом с выхода 45 блока 21 (управление параллельным приемом регистра 5, сдвига) регистр 5 по импульсам с выхода младшего разряда счетчика-делителя 2 начнет выдвижение видеоинформации на вход ЦАП 24, который в зависимости от кода управления с выхода регистра 19 начнет формирование ви- i деосигнала определенного уровня.

В конце состояния 41 на выходе 47 формируется сигнал выборки столбцов динамической памяти и начинается процесс восстановления блока 4 (его выходы перейдут в состояние 49,фиг.2). В конце состояния 40 счетчика-делителя 2 сигнал выборки строки )выход 29 :блока 21 ) формирует адрес строки, с.чи- танный с магистрали 8 адреса, переключит адресные входы блока 4 к адресным шинам магистрали 8 адреса, определяющим адрес столбца.

В конце состояния 39 сигнал выборки столбцов (выход 47 блока 21) формирует адрес столбца, блок 4 в зависимости от состояния сигнала на входе записи, который в этот момент подключен к выходу триггера 7, работает либо в режиме записи информации с магистрали 17 данных, которая через шинный формирователь 16 по сигналу с выхода элемента И 13 подается на входы данных блока 4, либо в режиме чтения. Если сигнала записи нет, формирователь 16 подключает к магистрали 17 выходы регистра 18.

Состояния 38 и 37 аналогичны состояниям 44 и 43 (фиг. 2) с той разницей, что в это время адресный регистр блока 4 хранит состояние необходим1)ГХ разрядов адресной магистрали 8.

При сигнале лог. 1 с выхода 46 блока 21 информация запш-ается в регистр 18 (через элемент И 14, если было обращение мшсронродессора 9 к блоку 4, т.е. если сработал селектор 12 адреса). Этот же сигнал посту- нит на шину 20 готовности, что соответствует сообщению микропроцессору 9 о TOMf что на шинах данных информация истекла или что закончился цикл заниси.

При сигнале выбора строки лог. 1 (выход 29 блока 21) начинается подготовка динамической намяти к следующему циклу, а при состоянии лог о о выхода 28 блока 21 адресные входы блока 4 подключены к выходам счетчика 3. По сигналу выборки столбцов в конце состояния 35 (фиг. 2) вьпсоды блока 4 нерейдут в состояние. 36 и окончится цикл работы с микропроцессором 9. Счетчик-делитель 2 нерейдет в состояние 34 и весь процесс повто- ,рится.

Таким образом осуществляется последовательная выдача информации из каждой ячейки блока 4, запись информации о ходе утчравленпя в регистр i для кахгдого выбранного слова вид,ео- информации (6 бит) и преобразование с помощью регистра : и ЦАП 24 в последовательный сигнал, амплитуда которого зависит от состояния регистра 19,

Дешифратор 23 Построен декодирует код, при котором агмплитуда сигнала с выхода ЦлП 24 соответствует амплитуде синкрош-ту.-Госа, Выходные сигкаль дешифратора 23 можно использовать в качестве ОСИ в мониторах с отдельньи входом ОСИ либо в ка честве сигнала внешней синхронизации в случае отображения ш-1формации на оси шлографе.

Счетчик 22 осуществляео вычитание только в случаях, когда деш1фратор 1 де лнфрует код сиг-перо импульса и на выходе ЦАП 24 формируется сигнал с амплитудой синхроимпульса. Если число предустановки счетчика 22 больше мак

5

0

симального числа ячеек блока 4, отве денных для формирования ССИ, сигнал заема со счетчика 22 возникает только при считывании КСИ их блока 4, т.е. счетчик 22 выполняет функции временного селектора, вьоделяющего КСИ, ис- псзльзуемый в мониторах с отдельным входом КСИс

Сигнал заема с выхода счетчика 22 обнуляет счетчик 25 и прекращает фор™ мирование ступенчатого напряжения на выходе ЦАП 26. Период ступенчатого . напряжения на выходе ЦАП 26 равен периоду кадровой частоты и этот сигнал можно использовать в качестве сигнала вертикального отклонения при вьшо де информации на осциллограф.

В любую ячейку блока ,4 можно запн- |Сать произвольную информацию. Так как два старщих бита определяют код яркости, шесть maдшиx отображаются в виде части строки на экране, возможно отображать как цифробуквенную, так и 5 графическую информацию.

Отображение цифробуквенной инфор - мации осуществляется путем занесения в онределенные ячейки блока 4 информации, соответствумщей графике симво- ла в определенной матрице разложения для разложения русского и латинского алфавитов чаще используют матрицу 5x7 или 7x9, а иероглифов 32x32). В некоторых случаях для разлозкения про- писных и строчных б.;ГКБ используют матрицы 7x9 и 5x7, что существенно повышает гибкость устройства {позволяет отображать буквы различных алфави тон к иероглифы), улучшает эргономические характеристики.

В пре,цлагаемом устройстве процесс сз нтеза графики симззола реализуется с помощью микропроцессора 9 но прог- paj-fMB, храни «ой в блоке этом считывается из блока 11 код текущего символа, предназначенного дпя отображения ,

Шжропроцессор 9 анализирует состояние регистра состоянвл (не показан) определяет матрицу разложения и режим отображения (позитив, негатив, мигание и т.д.)s считывает из специальной области блока 10 в зависимости от кода сш«золов словОд соот0

40

55

вой строки графики символа, и перешг- сывает его в блок 4., затек второй строки и т.д. столько paSf сколько строк в матрица разложения символа.

Ч1

В зависимости от режима вывода считанная информация записывается,в блок 4 в прямой или инверсной форме, что соответствует режиму отображения в позитиве или негативе. Если используется матрица разложения 5x7, пять бит строки используются для вывода символа, а один - для реализации пробела. Если число столбцов в матри це разложения больше шести бит, каждая строка символа может быть считана за несколько циклов. Таким образом реализуется возможность отображения символов в различных режимах с различными матрицами разложения.

Так как процесс знакогенерации реализуется программно, для генераци символа с другой графикой либо с дру- гой матрицей разложения достаточно вызвать другую программу либо изменить ее входные параметры. Такая возможность позволяет оперативно изменять используемый алфавит и графику символов и использовать одно устрой- ство для вывода как цифробуквенной, так и графической информации.

Предлагаемое устройство формирует полньш видеосигнал (сигнал с выхода ЦАП 24, содержащий видеосигнал, ССИ и КСИ), который может подаваться на видеовход телевизионного приемника для отображения. На выходах дешифратора 23 и счетчика 22 формируются ССИ и КСИ, что позволяет использовать это устройство для работы с мониторами, имеющими раздельные входы ССИ и КСИ и не имеющими схем селекции этих импульсов из видеосигнала. Наличие ступенчатого сигнала с периодом кад- ровой частоты с выхода ЦАП 26 и раздельных сигналов строчной частоты и видеосигнала при подключении их со- ,ответственно на входы вертикального о 5:клонения, внешней сшгхронизации и управления яркостью позволяет использовать устройство для отображения информации на экране осциллографа.

ормула изобретения

Устройство для отображения информации, содержащее тактовый генератор, выход которого подключен к входу двоичного счетчика-делителя частоты счет-,

чик знаков, строк и рядов,, блок памяти видеоинформации, выходы которого подключены к информационным входам регистра сдвига, первый и второй циф

IQ ig

2о 25

зо Q .

35

Q

О

8212

роаналоговые преобразователи, два регистра, счетчик строк, два элемента И,, селектор адреса, вход опорного напряжения второго цифроаналогового преобразователя соединен с источн1п :ом опорного напряжения, триггер и блок синхронизации, отличающее- с я тем, что, с целью расширения области применения устройства путем обеспечения возможности отображения информации с оперативно изменяе гыми параметрами растра, оно содержит шинный формирователь, блок управления, дешифратор, вычитающий счетчик, блок памяти программ и графики символов, блок памяти кодов символов и мультиплексор, информационные входы первой группы которого с выходами счетчика знаков, строк и рядов, адресный вход - с выходом триггера, адресные входы группы - с выходам первой группы блока управлейия, подк.тю- ченными к адресным входам блоков памяти программ и графики символов и кодов символов, выходы счетчика знаков, строк и рядов соединены с информационными входами мультиплексора, первый выход блока синхронизации сое-, динен с синхровходом первого регистра, управляющим входом регистра сдвига и счетным входом вычитающего счетчика, второй выход - с первым входом первого элемента И, второй вход которого и первый вход второго элемента И подключены к выходу селектора адреса, второй вход второго элемента И соединен с выходом первого элемента И,подключенным к синхровходу второго регистра, управлягошдм входам блока управления и блокам памяти программ и графики символов и кодов символов,третий выход блока синхронизации соединен с входом выборки столбца блока памяти видеоинформации, четвертый выход - с входом выборки строки блока памяти видеоинформации и первьш управляющим входом мультиплексора, пятьт выход - с вторым управляющим входом мультиплексора, счетным входом счетчика знаков , строк и рядов и синхровходом триггера, информационный вход триггера соединен с выходом второго элемента И, подключенным к управляющему . входу шинного формирователя, информационные входы первой группы которого подключены к выходам блока памяти програмй и графики символовs блока управления и блока памяти кодов симво13 13

лов, выходы готовности блока управления и блоков памяти программ и графики символов и кодов символов соединены с вторым входом второго элемента и, выходы регистра сдвига соединены с информационными входами второй группы шинного формирователя, выходы которого подключены к информационным входам блока памяти видеоинформации, выходы которого соединены с информационными входами первого и второго регистров, адресные входы и вход за- писи блока памяти видеоинформации соединены с соот1зетствующими выходами мультиплексора, выход младшего разряда двоичного счетчика-делителя частоты соединен с синхровходом регистра сдвига и младшим разрядом адресного входа блока синхронизации, другие адресные входы которого соединены с соответствующими выходами двоичного

3V -J

35 36

37

39 39

82

14

счетчика-делителя частоты, выходы первого регистра подключены к входам дешифратора и информационным входам первого цифроаналогового преобразователя, вход опорного напряжения кото- рого соединен с выходом регистра сдвига, а выход его является видеовыходом устройства, выход дешифратора является выходом строчных синхроимпульсов устройства и соединен со счетным входом счетчика строк и установочным входом вычитающего счетчика, выход которого является выходом кадровых синхроимпульсов устройства и соединен с входом сброса счетчика строк, выходы которого подключены к информационным входам второго цифро- аналогового преобразователя, выход - которого является выходом сигнала вертикального отклонения луча устройства.

.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране электронно-лучевой трубки | 1984 |

|

SU1256084A1 |

| Устройство для отображения информации | 1987 |

|

SU1493999A2 |

| Устройство для отображения символьной информации на экране видеоконтрольного блока | 1991 |

|

SU1836678A3 |

| УСТРОЙСТВО И СПОСОБ ОТОБРАЖЕНИЯ ТЕЛЕВИЗИОННОЙ ВИДЕОИНФОРМАЦИИ НА ЭКРАНЕ КОМПЬЮТЕРНОГО МОНИТОРА | 2011 |

|

RU2464725C1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1585830A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА-ВЫВОДА ИЗОБРАЖЕНИЙ | 1993 |

|

RU2066928C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1985 |

|

SU1367036A1 |

| Устройство отображения информации на экране телевизионного индикатора | 1986 |

|

SU1425768A1 |

| Устройство для отображения информации | 1989 |

|

SU1741123A1 |

Изобретение относится к вычислительной технике и может быть исполь- . зовано при разработке универсальных устройств отображения знаковой и графической информации. Цель изобретения - расширение области применения устройства путем обеспечения возможности отображения информации с оперативно-изменяемыми параметрами растра. (Л 00 СП 00 ito

Редактор П.Гереши

Составитель И.Загинайко Техред М.йоданнч

Заказ 5694/43 Тираж 671Подписное

ВНИИГГИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-ЗЗ, Раушская Ha6.j д. 4/5

Производственно-полиграфическое предприятие, г, Ужгородр ул. Проектная, 4

Корректор С.Шекмар

| Современные методы и устройства о -ображения информации | |||

| Под ред | |||

| М.И.Кривошеева и А.Ч.Брейтбарда | |||

| М.: Радио и связь, 1981, с | |||

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

| Электроника, 1981, № 25, с | |||

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-11-23—Публикация

1984-12-19—Подача