(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное оперативное запоминающее устройство | 1988 |

|

SU1667155A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1309041A1 |

| Ассоциативное оперативное запоминающее устройство | 1986 |

|

SU1363307A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| Устройство для формирования гистограммы случайных чисел | 1986 |

|

SU1388901A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1735907A1 |

| Устройство для поиска информации в ассоциативной памяти | 1988 |

|

SU1617460A1 |

| Устройство для управления замещением информации | 1975 |

|

SU651413A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1439671A1 |

1

Изобретение относится к вычиспитепьной технике и может быть использовано для построения устройств хранения цифровой информации.

По основному авт. св. Ns 826418 известно запоминающее устройство, содержащее матрицу и-И блоков памяти, где VI - разрядность слова, адресные вхо- . ды которых соединены с вы ЬоДами стар-iо ших разрядов регистра адреса, входы ЕЫбора блоков памяти i -и, где i истроки матрицы подключены к -му выходу, дешифратора, входы которого соединены с выходами младших разрядов регистра адреса, информационные входы блоков памяти 3-го, где 1 s VIстолбца матрицы подключены к j -му выходу входного ре- гистра, а информационные выходы - к j -(Л группе входов основного блока эле-20 ментов ИЛИ, выходы которого соединены со входами выходного регистра, входные коммутаторы, коммутаторы выбора блоков памятм, выходной коммутатор и

дополнительный блок элементов ИЛИ, входы выбора блоков памяти -ой строки матицы подключены к одноименным выходам 1 -го коммутатора выбора, первые входы которого подключены к -му, а вторые - к одноименным выходам дешифратора, информационнь1е входы блоксж па мяти j-ro столбца матрицы соединены с одноименными выходами -го входного коммутатора, первые входы которого подключены к и -му а вторые - к одноименным выходам входного регистра, информационные выходы блоков памяти Л -ой строки матрицы подключены к 1-ой группе входов дополнительного блока элементов ИЛИ, выходы основного блока элементов ИЛИ соединены с первыми, а выходы дополнительного - со вторыми входами выходного коммутатора, выходы которого соединены со входами выходного jperiJCTpa, управляющие входы всех коммутаторов поцключены к дополнительному Ьазряоу регистра ацреса

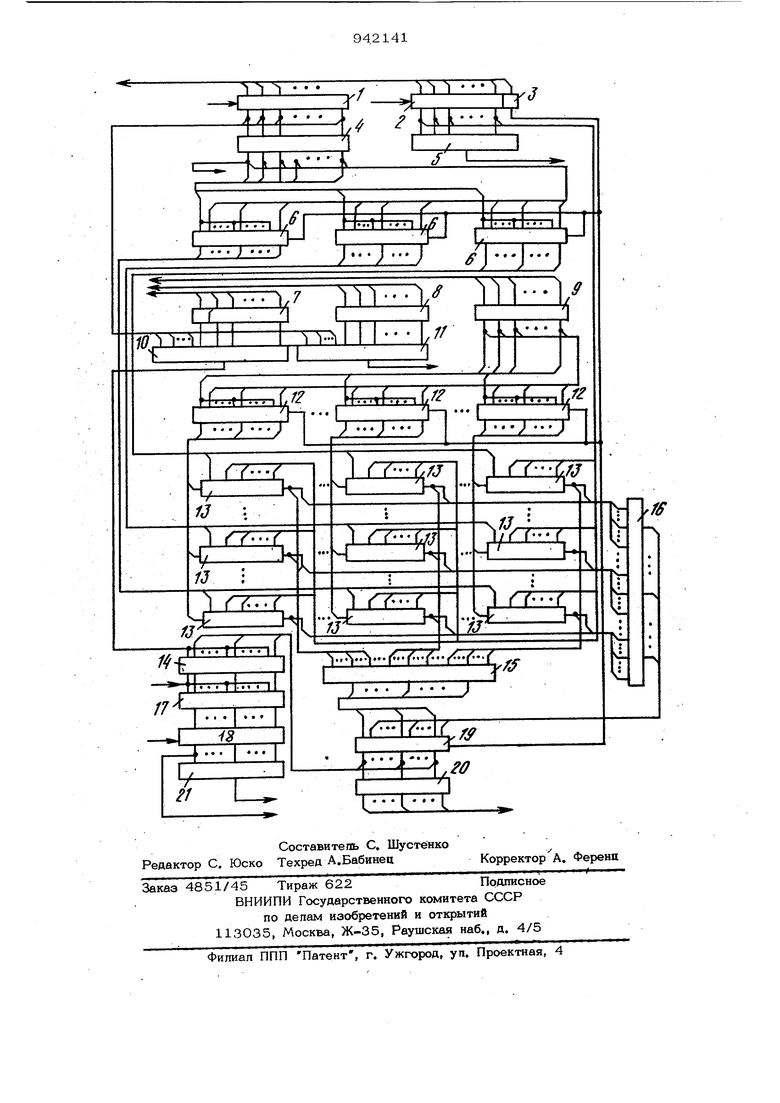

П. 39 Недостатком устройства является невозможность ассоциативного считывания и записи информации по совпадению незамаскированных разрядов спов с заданным признаком. Цепь изобретения - расширение облас ти применения путем ассоциативного счи тывания и записи информации по совпЕЩе нию незамаскированных разрядов спов с заданным признаком.Поставленная цепь достигается тем, что в запоминающее устройство дополнительно введены регистры маски и признака, коммутаторы маски и признака, итоговый регистр сдвига, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ через коммутатор 10 признака поступает сигнал выключены к выходам блока элементов ИС КЛЮЧАЮЩЕЕ ИЛИ, а выходы - к входам итогового регистра сдвига, входы первого элементе ИЛИ подключены к вы ходам старших разрядов адресного регистра, а выход первого элемента ИЛИ является соответствующим управляющим выходом устройства, выходы итогового регистра сдвига подключены к входам вт рого элемента ИЛИ, выход которого яв ляется соответствующим управляющим вы ходом устройства, одни входы блока элементов ИСКЛЮЧАЮЩЕЕ или подкпю чены к выходам выходного коммутатора, а другие входы - к выходу коммутатора при:М%1ш, одни входы которого подключены к выходам младщих разрядов адресного регистра, другие входы - к выходам регистра признака, одни входы коммутатора маски подключены к выходам младших ра;зрядов регистра адреса, а другие входы - к выходам регистра маски, выход коммутатора маски является соответ ствующим управляющим выходом устройства. На чертеже приведена блок-схема запоминающего устройства. Запоминающее устройство содержит регистр-счетчик 1 младщих разрядов регистра адреса, регистр-счетчик 2 старших разрядов регистра адреса, дополнительный разряд регистра 3 адреса, дешиф ратор 4, первый элемент ИЛИ 5, коммутаторы 6 выбора, регистр 7 признака, ре гистр 8 маски, входной регистр 9, коммутатор Ю признака, коммутатор 11 Маски, входные коммутаторы 12, матрицу блоков 13 памяти, блок 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, основной блок 15 элементов ИЛИ, дополнительный блок 16 яломйнтов ИЛИ, бпок 17 элементов И, 1 итоговый регистр 18 сдвига, выходной коммутатор 19, выходной регистр 20 и второй элемент ИЛИ 21. Коммутатор 10 признака и коммутатор 11 маски - коммутаторы с Vl информационными входами и одним выходом. Блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 14 содержит И двухвходовых элементов ИСЦ КЛЮЧАЮЩЕЕ ИЛИ. Первый 5 и второй 21 элементы ИЛИ представляют собой И-входовые элементы ИЛИ, а блок 11 элементов И содержит И двухвходовых элементов И. Предлагаемое устройство может работать в девяти режимах: хранения информации, считывания ц -разрядных чисел, записи И-разрядных чисел, считывания данных,представляющих группу одноименных разрядов у чисел, записи данных, представляющих собой группу одноименных разрядов И чисел, ассоциативного считывания VI-разрядных чисел по совпадению незамаскированных разрядов чисел с заданным признаком, ассоциативной записи и-разрядных чисел, ассоциативного считывания данных, представляющих со:бой группу одноименных разрядов И чисел, по совпадению незамаскированных разр5Щов данных с заданным признаком, ассоциативной записи данных, представляющих собой группу одноименных разрядов чисел.В режиме хранения информации считывание и запись информации не производится. В режиме считывания V)-разрядных чисел устройство работает следующим образом. В регистр адреса (регистр-счетчики 1 младших и старших разрядов) заносится адрес чиспа, одновременно допопни - тельный разряд регистра 3 адреса устанавливается 6 состояние О. Регистр 7 признака, регистр 8 маски, коммутатора 10 признака и 11 маски, блок 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок 17 схем И, первый 5 и Второй 21 элемент ИЛИ и итоговый .регистр 18 сдвига при этом в работе устройства не участвуют. На управляющие входы коммутаторов 6 выбора, входных коммутаторов 12 и выходного коммутатора 19 поступает сигнал логического нуля. При этом через дешифратор 4 и коммутаторы 6 выбора на входы выбора блоков памяти 1-ой строки матрицы блоков 13 (номер строки задается младшими разрядами регистра-счетчика 1 адреса) поступает 59 сигнап погической единицы, на входы вы бора остальных блоков 13 памяти матри цы поступает сигнаа погического нупя. Адресные сигнапы старших разрядов регистра-счетчика 2 адреса поступают на адресные входы всех блоков 13 памяти. Таким образом, оказывается выбранной одна ячейка бпоков памяти -ой строки таблицы. Производится считывание: сигналы считываемого числа с информационных выходов блоков 13 памяти i -ой строки через основной блок 15 схем ИЛИ и выходной коммутатор 19 поступают на вхо ды выходного регистра 20 и соответствуюшие вторые входы блока 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Чиспо из выбранной ячейки памяти записывается в выходной регистр 2О. Запись и -разрядного числа происходит следующим образом. Во входной регистр 9 заносится записываемое число. Также как в режиме записи И-разрядны:1 чисел во входной регистр 9 заносится адрес числа и производится выбор яче ки памяти, в которую необходимо записать число. Производится запись: сигналы записываемого числа с выходов входного регистра 9 через первые входы входных коммутаторов 12 поступают на информационные входы всех блоков памяти и устанавливают запоминающиеэлементы выбранной ячейки в необходимые состояния. В режиме считывания данных, представляющих собой группу одноименных разрядов VI чисел в регистр адреса (ре.гистры-счетчики 1 младших и 2 старших разрядов) заносится адрес данных (чиспа), одновременно дополнительный разряд регистра 3 адреса устанавливается в состояние . Регистр 7 признака, регист 8 маски, коммутаторы 1О признака и 11 маски, первый и второй элементы ИЛИ 5 и 21, блок 17 схем И и итоговый регистр 18 сдвига при этом в работе уст«ройства не участвуют. На управляющие входы коммутаторов 6 выбора, входных коммутаторов 12 и выходного коммутатора 19 поступает сигнал логической единицы. При этом через Дещифратор 4 и коммутаторы 6 выбора на входы выбора блоков памяти j -го столбца матрицы блоков 13 (номер столб, ца задается младщими разрядами регистрасчетчика 1 адреса) поступает сигнап логической единицы, на входы выбора остальных блоков 13 памяти матрицы по41ступает сигнал логического нуля. Адресные сигналы старших разрядов регистрасчетчика 2 ещреса поступают на адресные входы всех блоков 13 памяти. Таким образом, оказывается выбранным набор запоминающих элементов, соответствующих группе j -X разрядов и чисел в блоках памяти j -го столбца матрицы. Производится считывание: сигналы считываемой, группы разрядов с .информационных входов блоков памяти j -го стопбца матрицы бпоков 13 через дополнительный блок 16 элементов ИЛИ и выходной коммутатор 19 поступает на входы выходного регистра 2О и соответствующие вторые входы блока 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Группа одноименных разрядов и чисел из выбранного Ha6opfi запоминающих элементов записывается в вы- ходной регистр 2О. В режиме запись данных, представляющих собой группу одноименных разрядов м чисел, во входной регистр 9 заносится записываемая группа раз рядов данного числа. Так же, как и в пп. 4.1 и 4.2 как и в режиме считывания данных, представляющих собаЛ группу одноименных разрядов и чисел, заносится адрес числа (данных) и производится выбор запоминающих элементов, в которые необходимо записать группу одноименных разрядов И чисел. Производится запись: сигналы записываемых разрядов с выходов входного регистра 9 через вторые входы входных коммутаторов 12 поступают на инфсфмационные входы всех бпоков 13 памяти и устанавливают запоминающие элементы выбранного набора в необходимые состояния. В режиме асссншативного с:читывания П-разрядных чисел по совпадению незамаскированных разрядов чисел с заданным признаком регистры-ч:четчики 1 младщих и 2 старщих разрядов адреса устанавливаются в нулевое состояние (нулевое состояние регистра-счетчика 2 старших разрядов адреса задает первый массив из И, W -разрядных чнсеп), одгновременно дополнительный разряд регистра 3 адреса устанавливается в состот яние 1. В регистр 7 признака заносит ся признак числа (И-разрядный двоичный код), в регистр 8 маски - маска (П-разрядный двоичный код, цифра О, в котором маскирует одноименнь1Й разряд при- . знака, исключая его из рассмотрения), а итоговый регистр 18 сдвига устанавливается в состояние 11...1. Производится опрос-опреДепение адресов чисел заданного массива, незамаскированные разряды которых совпадают с заданным признаком. Для этого на управляющие входы коммутатора 1О признака и коммутатора 11 маски поступают адресные сигналы младших разрядов регистра-счетчика 1 адреса. При этом на первые входы блока 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ через коммутатор 10 признака поступает сигнал выбранного разряда регистра 7 признака, а на вы ходе коммутатора 11 маски появляется сигнал выбранного разряда регистра маски. Если на вь1ходе коммутатора 11 маски устанавливается сигнал 1 (разряд регистра маски не равен О), то также как и в режиме считывания данных, пред ставляющих собой группы одноименных разрядов И чисел, производится выбор запоминающих элементов и считывание группы разрядов м чисел из блоков памяти j-го столбца матрицы. При этом на вторых входах блока 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ появляются сигна лы, соответствующие группе одноимен ных разрядов Л чисел, В случае несо&паденйя каких-либо разрядов считанной группы с разрядом призрака, соответствующие им разряды итогового регистра 18 сдвига через блок 17 элементов И устанавливаются в нулевое состояние. Если на выходе коммутатора 11 маски устанавливается сигнал О , то выбор, считывание и изменение содержимого итогового регистра 18 сдвига не выпол няются. Если на выходе второго элемента ИЛИ 21 единичный сигнал (хотябы один разряд итогового регистра 18 сдрига со хранил единичное состояние), то содержимое регистра-счетчика 1 младших раз рядов адреса увеличивается а единицу, в противном случае осуществляется пере ход к определению номера сле ющего анализируемого массива , У -разрядных чисеп. Если на первом выходе дещи Чратора 4 нулевой сигнал (содержимое регистрасчетчика младших разрядов 1 адреса не равно нулю) то осуществляется переход к опросу-определению адресов чисел данного массива, описанного выше, в противном случае выполняется считывание чисел, незамаскированные разряды которых совпадают с заданным признаком. Для осуществления этого режима допопнительный разряд регистра 3 адреса устанавливается в состояние О. Если младший разряд итогового регистра 18 сдвига в единичном состоянии, то также как и в режиме считывания и-разрядных чисел производится выбор, считывание и занесение считанного числа (незамаскированные разряды которого совпадают с заданным признаком) в выходной регистр 20. В противном случае содержимое регистра-счетчика 1 младших разрядов адреса увепичивается на единицу и содержимое итогового регистра 18 сдвига сдвигается на одан разряд в сторону младших разрядов. Если на выходе второго элемента ИЛИ 21 единичный сигнал, то осуществляется анализ младшего разряда итогового регистра сдвига вышеуказ&нным образом, в противном случае выполняется следующий пункт. Определение номера следующего анализируемого массива и - разрядных чисел. Для осуществления этого режима регистр-счетчик младших разрядов 1 адре-, са устанавливается в нулевое состояние, содержимое регистра-счетчика 2 старших разрядов адреса увеличивается на единицу, а итоговый регистр 18 сдвига устанавшвается в состояние 11...1. Еспи на выходе первого элемента ИЛИ 5 единичный сжгнал (содержимое регистра-счетчика 2 старших разрядов адреса не равно нулю), то осуществляется переход к опросу-определению адресов чисел заданного массива, в противном случае процесс ассоциативного считывания и -разрядных чисел по совпадению незамаскированных разрядов чисел с заданным признаком заканчивается. В режиме ассоциативной записи и разрядных чисел начальные установки и опрос-определение адресов чисел заданного массива в режиме ассоциативной записи Поразрядных чисел осуществляется аналогично режиму ассоциативного считывания VI-разрядных чисел по совпадению с незамаскированными разрядами чисел с заданным признаком. Осуществляется запись чисел по адресам, в которых хранятся числа, незамаскированные разряды KOTOpjix совпадают с заданным признаком. Для этого дополнительный разряд регистра 3 адреса устанавливается в состояние О. Еспи младший разряд итогового регистра 18 сдвига в единичном состоянии, то так же, как и в режиме записи разрядного

числа, производится запись п-разрядного числа; в противном случае содержимое регистра-счетчика 1 младших разрядов адреса увеличивается на единицу и содержимое итогового регистра 18 сдвига сдвигается на один разряд в сторону младших разрядов.

Если на выходе второго элемента ИЛИ 21 единичный сигнал, то осуществляется анагшз младшего разряда итого- ю не выполняются. вого регистра 18 сдвига, в противном случае выполняется определение номера следующего анализируемого, массива Hf И -разрядных чисел. .Если на выходе первой схемы ИДИ 5 единичный сигнал, то осуществляется переход к опросу-определению адресов чисел заданного массива, в противном слу- чае процесс ассоциативной записи vi -разрядных чисел по совпадению незамаски рованных разрядов чисел с заданным признаком заканчивается. В режиме ассоциативного считывания данных, представляющих собой группу ОДГноименных разрядов И чисел по совпадени1р незамаскированных разрядов данных с заданным признаком регистры-счетчики 1 младших и 2 старших разрядов. адреса устанавливаются в нулевое состо(Яние, дополнительный разряд регистра 3 адреса устанавливается в состояние О. Другие начальные установки аналогичны режиму ассоциативного считывания И-раз рядных чис(еп. Производится опрос-определение адресов данных, пpeдcтaвляtoщиx собой группу одноименных разрядов и чисел, незамаскированные разрядь кото рых совпадают с заданным признаком. На управляющие входь коммутатора 1О. признака и крммутатора 11 маски поступают адресные сигналы младших разрядов регистра-счетчика 2 адреса. При этом на первые входь блока 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ через коммутатор 10 признака поступает сигнал выбранного разряда регистра 7 признака, а на выходе коммутатора 11 маски появляется сигнал выбранного разряда регистра маски. Если на вызсоде коммутатора 11 маски устанавливается сигнал , то так же, как в режиме считывания и-разрядных чисел, производится выбор запоминающих элементов и считывание числа, записанного в 1 -ой строке матрицы. При этом на BTOjbix входах блока 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ появляются сигналь:, соответствующие считанному

числу, в случае несовпадения каких-либо разрядов считанного числа с разрядом признака, соответствующие им разряды итогового регистра 18 сдвига через бло«. 17 схем И устанавливаются в нулевое состояние. Если на выходе коммутатора 11 маски устанавливается сигнал О, то выбор, считывание и изменение содержимого итогового регистра 18 сдвига Если на выходе второй схемы ИЛИ 21 единичный сигнал (хотя бы один разряд итогового регистра 18 сдвига сохраняет единичное состояние), то содержимое регистра-счетчика 2 старших разрядов адреса увеличивается на единицу и выполняется следующий пункт, иначе переход к определению номера спедующего анализируемого массива данных, представляющих собой группу одноименных разрядов и чисел, описываемое нижв. Если на выходе схемы ИЛИ 5 единичный сигнал (содержимое регистра-счетчика 2 старщих разрядов адреса не равно нушо), то осуществляется переход к опросу-определению адресов данных, в противном случае выполняется считывание данных, представляющих группу одноименных раз-рядов у чисел, незамаскированные разряды которых совпадают с заданным признаком. Для осуществления этого допопнительный разряд регистра 3 адреса устанавливается в состояние . Если младший разряд итогового регистра 18 сдвига в единичном состоянии, .то так же, как и в режиме считывания данных, представляющих собой группу однояменвых разрядов -И чисел, производится выбор,. считывание и запись считанных данных в выходной регистр 2О, в противном спучае содержимое регистра-счетчика 2 старших разрядов адреса увеличивается на единицу и содержимое итогового регистра 18 сдвига сдвигается на один разряд в сторону младщих разрядов. Есщ на выходе второй схемы ИЛИ 21 единичный сигнал, то осуществляется переход к считыванию данных, в противжяи случае выполняется опредепение номере спедующетх) анализируемого массива Аанных, представляющих собой групйу одноименных разрядов И чисел. Для осуществления этого регистр-счетчик 2 старщих разрядов /адреса устанавливается в нулевое состояние, содержимое регистра-счетчика 1 младших разрядов адреса увеличивается на 1, а итого1194вый регистр 18 сдвига устанавливается в состояние 11,.,1, Если. на первом выходе дешифратора 4 нулевой сигнал (содержимое регистрасчетчика 1 младших разрядов адреса не равно нулю), то осуществляется переход на опрос-опрюделение адресов данных, в противном случае процесс ассоциативного считывания группы данных, представляющих собой группу одноименных разрядов d чисел, по совпадению незамаски рованных разрядов данных с заданным признаком заканчивается. В режиме ассоциативной записи данных, представляющих собой группу одноименных разрядов и чисел, начальные установки и проведение опроса-определения адресов данных аналогично предыдущему режиму. Запись данных, представляющих собой группу одноименных разрядов И чисел, по адресам, в которых хранятся данные незамаскированные разряды которых совпадают с заданным признаком, производится следующим образом. Дополнительный разряд регистра 3 адреса устанавлиЕсли младший вается в состояние разряд итогового регистра 18 сдвига в единичном состоянии, то так же, как и в режиме записи подобных данных, произво дится запись данных, в противном случае происходит увеличение на единицу регист ра-счетчика 2 старших разрядов адреса и сдвига на один разряд в сторону младших разрядов итогового регистра 18 сдвига. Если на выходе второй схемы ИЛИ 21 единичный сигнал, то осуществляется переход к анализу младшего разряда итогового регистра 18 сдвига, в противном случае выполняется определение номера следующего анализируемого массива данных, представляющих собой группу одноименных разрядов И чисел. Для это го производятся начальные установки аналогичные как и при определении номера следующего анализируемого массива данных, представляющих собой группу одноименных разрядов Y чисел.

Если на первом выходе дешифратора 4 нулевой сигнал (содержимое регистрасчетчика 1 младших разрядов адреса не равно нулю), то осуществляется пункт опрос-определения адресов данных, в про- . тивном случае процесс ассоциативной записи данных, представляющих собой группу одноименных разрядов И чисел заканчивается.

ходам регистра признака, одни входы коммутатора маски подключень к выходам младщих разрядов регистра адреса, а другие входы -.к выходам регистра маски, выход коммутатора маски, является соответствующим управляющим выходом устройства.

Источники информации, принятые во внимание при экспертизе

№ 1 Таким образом, в .предлагаемом устройстве наряду с хранением информации, считыванием и записью М-разрядных чисел, считыванием и записью данных, представляющих собой одноименнью разрядь Ч чисел, возможно также выполнение ассо циативного считывания и записи -разрядных чисел и ассоциативного считывания и записке данных, представляющих собой группу одноимен агх разрядов и чисел, что расширяет; область применения запоминающего устройства. Формула и 3 о б р е т е н и я Запоминающее устройство по авт. св. № 826418, отличающееся тем, что, с целью расширения области его применения за счет ассоциативного считывания и записи информации по совпадению незамаскированных разрядов слов с заданным признаком, оно содержит регистры маски и признака, коммутаторы маски и признака, итоговый регистр сдвига, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элементь ИЛИ н блок элементов И, входы которого подключены к выходам блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а выходы к входам итогового регистра сдвига,входы первого элемента ИЛИ подключены к выходам старших разрядов адресного регистра, а выход первого элемента ИЛИ является соответствующим управляющим выходом устройства, выходы итогового регистра сдвига подключены к входам второго элемента ИЛИ, выход которого являе|тся соответствующим управляющим выходом устройства, одни входы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходам выходного коммутатора, а другие входы к выходу коммутатора признака, один входы которого подключены к выходам младших разрядов ресного регистра, другие входы - к

TYT

Авторы

Даты

1982-07-07—Публикация

1980-07-22—Подача