Изобретение относится к вычислительной технике, в частности к устройствам хранения информации, и может быть использовано при построении интегральных микросхем ассоциативной памяти для высокопроизводительных систем параллельной обработки информации.

Цель изобретения - расширение области применения и повышение быстродействия устройства.

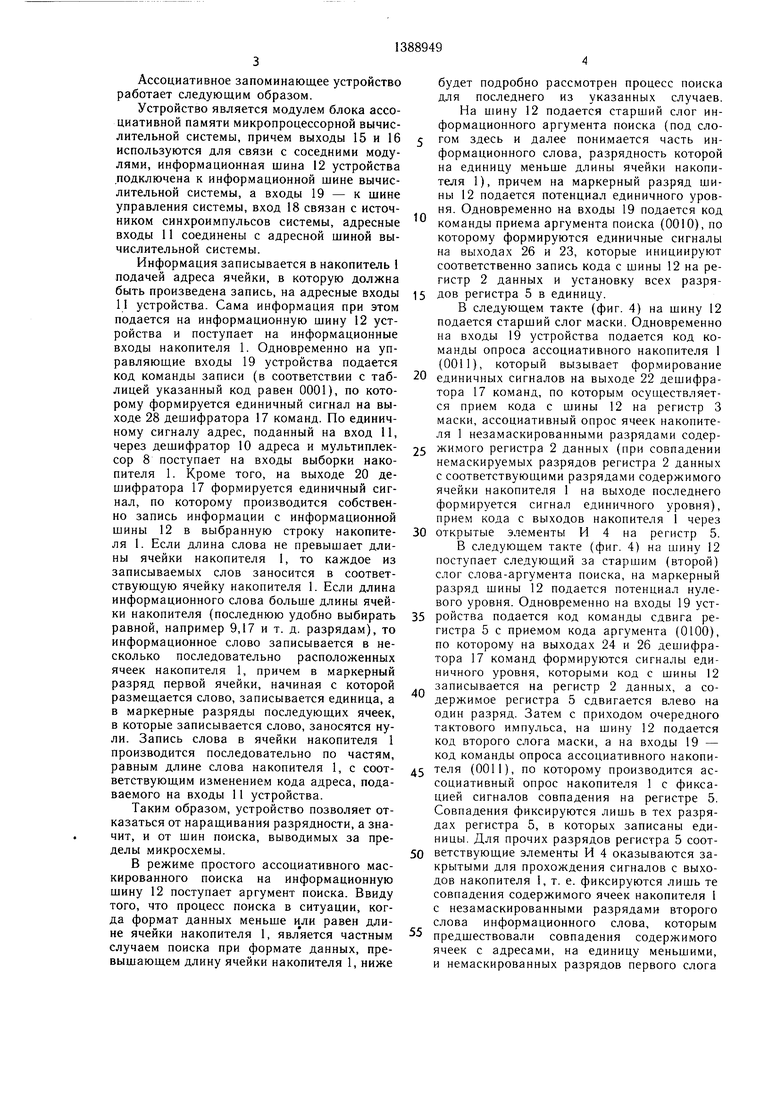

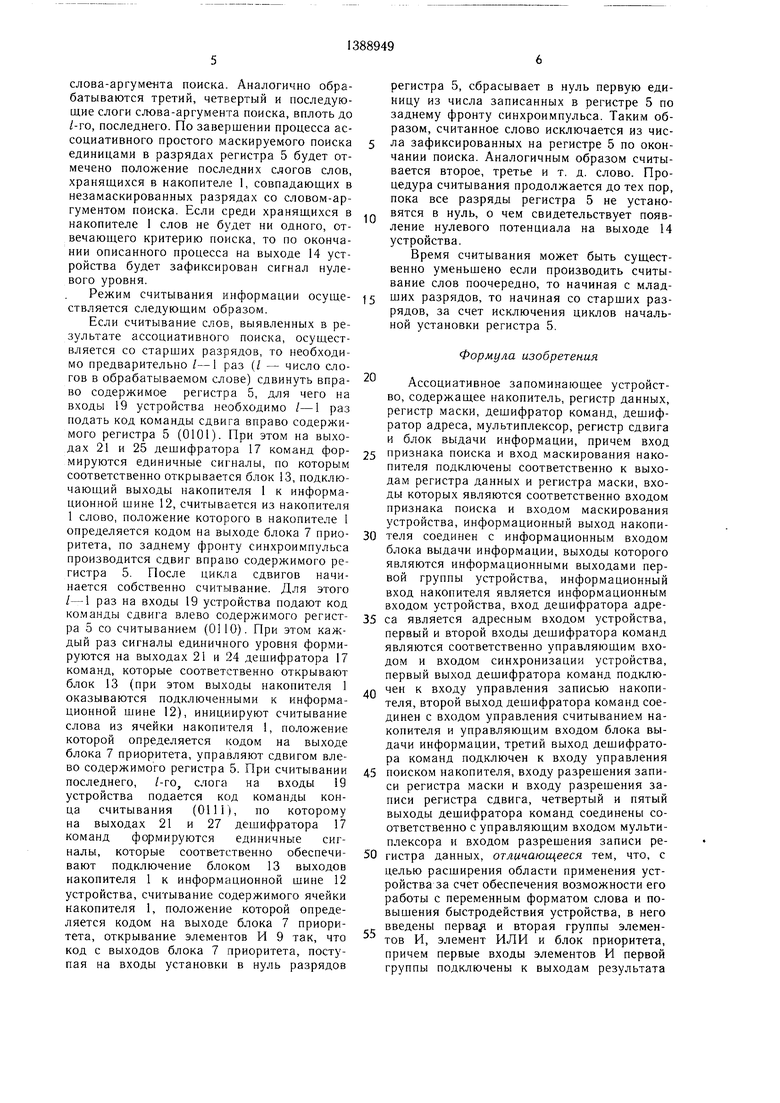

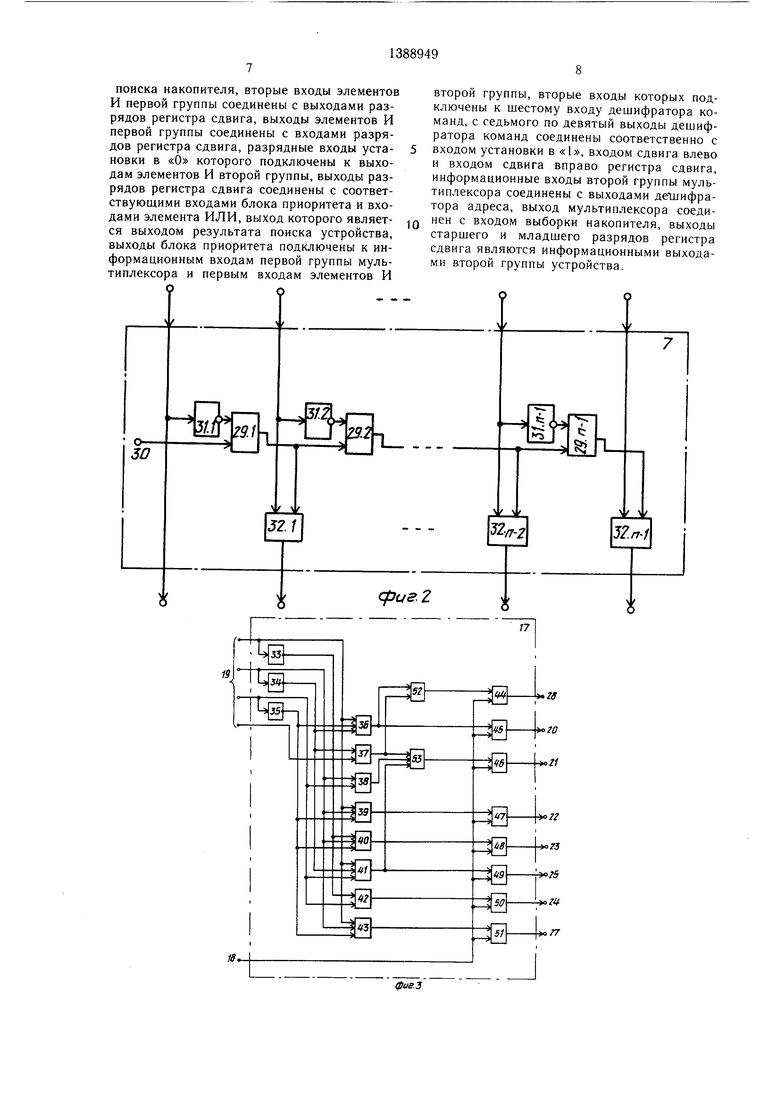

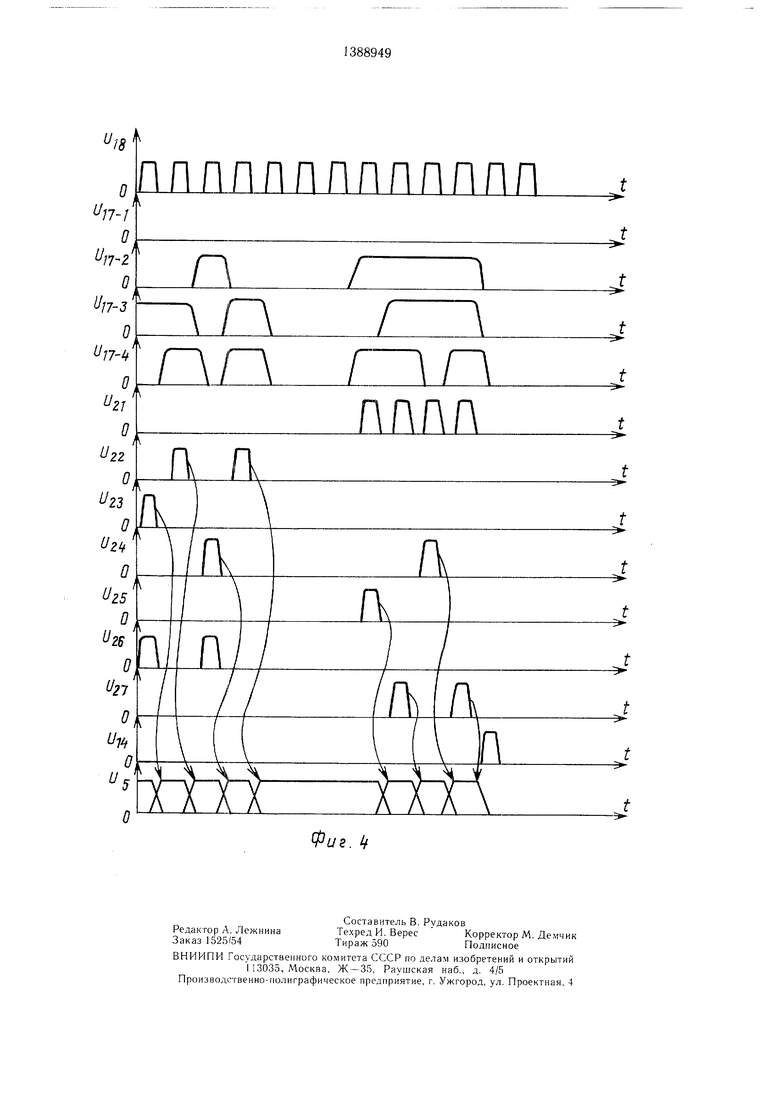

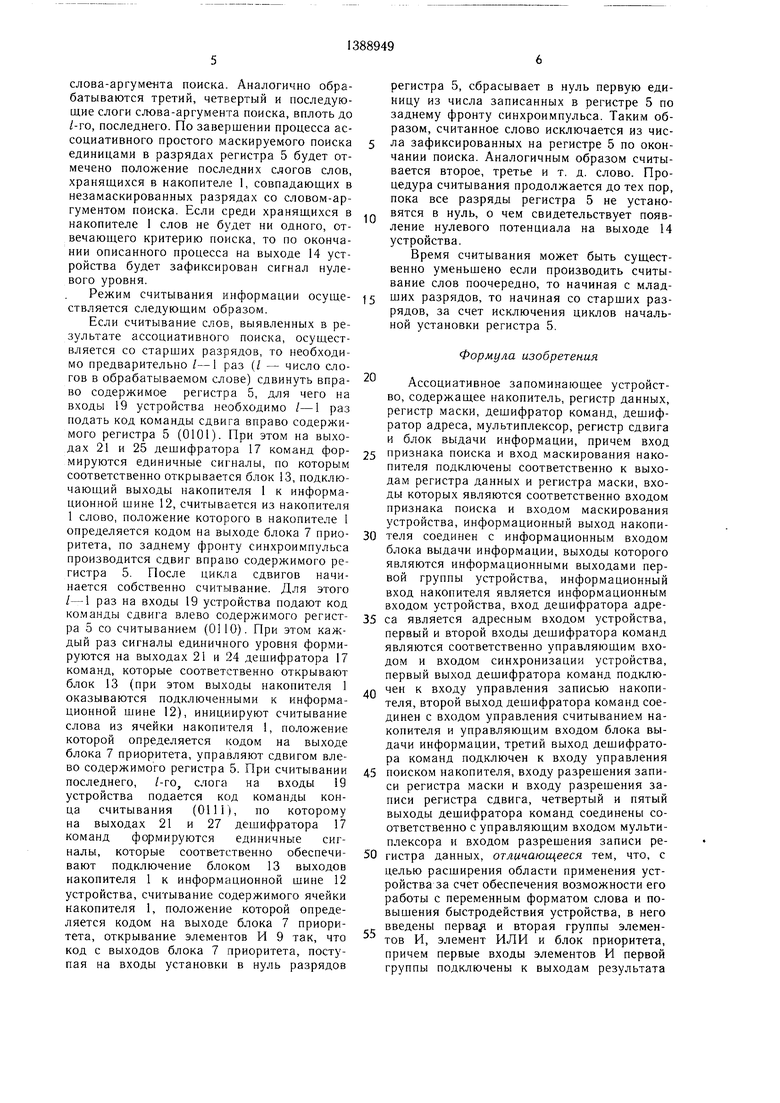

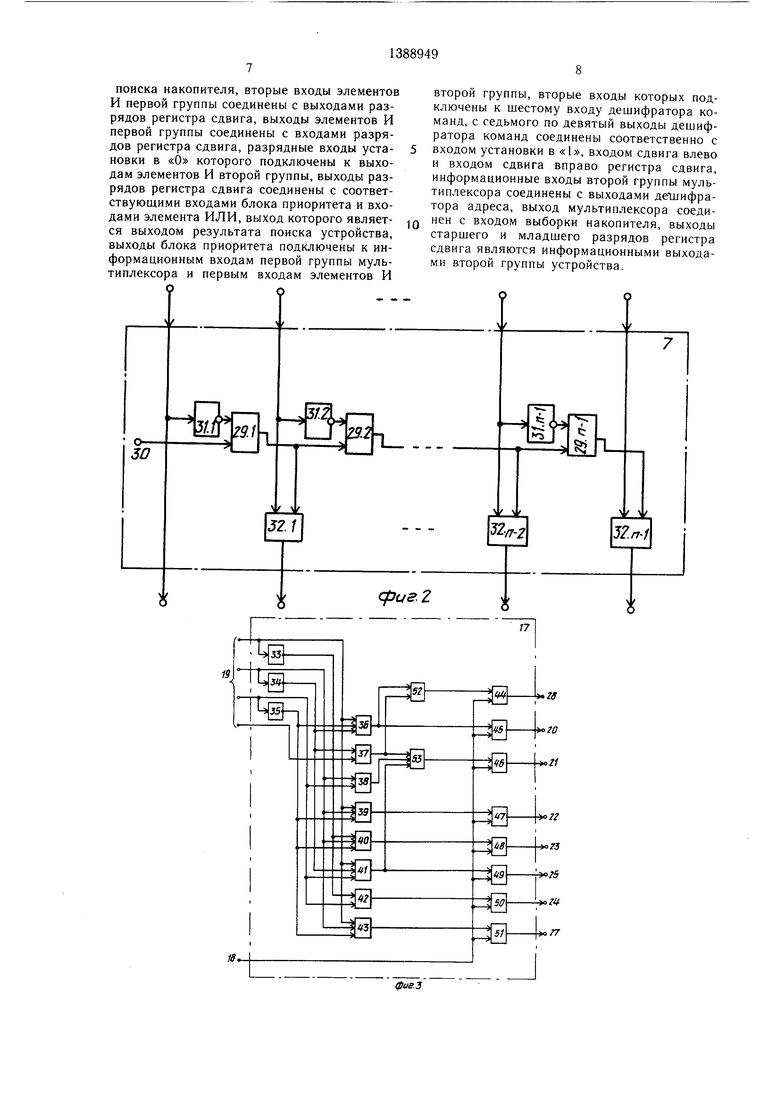

На фиг. 1 представлена структурная схема ассоциативного запоминающего устройства; на фиг. 2 - структурная схема блока приоритета; на фиг. 3 - структурная : схема дешифратора команд; на фиг. 4 - временная диаграмма процесса простого ассоциативного поиска.

Ассоциативное запоминающее устройство (фиг. 1) содержит накопитель 1, регистр 2 данных, регистр 3 маски, первую группу элементов H4i-4т1 (где п - число строк накопителя 1), регистр 5 сдвига, элемент ИЛИ 6, блок 7 приоритета, мультиплексор 8, вторую группу элементов И 9i-9, дешифратор 10 адреса, вход которого являет- ся адресным входом 11 устройства, шину 12 и блок 13 выдачи информации. Устройство имеет выходы 14-16. Устройство также содержит дешифратор 17 команд, имеющий входы 18 и 19 и выходы 20-28.

0

0

Блок 7 приоритета (фиг. 2) представляет собой комбинационную схему, выделяющую в п-разрядном входном слое первую единицу (п - число строк ассоциативного накопителя I). Блок 7 приоритета содержит первую группу элементов И 29i - ), причем вход первого элемента И 29i первой группы подключен к источнику 30 потенциала логической единицы, а другие входы всех элементов И 29 подсоединены к выходам соответствующих элементов НЕ 311-31(n-i), входами которых являются соответствующие входы блока 7 приоритета, причем первый вход блока 7 является первым выходом указанного блока, а остальные входы, с второго по п-й, подключены к входам соответствующих элементов И 32 - 32() второй группы, вторые входы каждого из которых соединены с выходами соответствующего элемента И 29 первой группы.

Дещифратор 17 команд представляет собой комбинационную схему, формирующую набор управляющих сигналов на своих выходах 20-28 под действием 4-разрядного кода команды, подаваемого на управляющие входы 19 устройства. Закон функционирования дешифратора 17 задается таблицей соответствия 4-разрядного кода команды и набора формируемых при этом на выходах 20- 28 дещифратора 17 выходных управляющих сигналов. Указанная таблица является таблицей истинности комбинационной схемы дешифратора 17.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования кодов с одного языка на другой | 1985 |

|

SU1275471A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Ассоциативное оперативное запоминающее устройство | 1988 |

|

SU1667155A1 |

| Ассоциативное запоминающее устройство | 1984 |

|

SU1234880A1 |

| Устройство для поиска информации в памяти | 1988 |

|

SU1520547A1 |

| Ассоциативное запоминающее устройство | 1991 |

|

SU1833917A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1785039A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Устройство для поиска информации в ассоциативной памяти | 1988 |

|

SU1617460A1 |

Изобретение относится к вычислительной технике, в частности к устройствам хранения информации, и может быть использовано при построении интегральных микросхем ассоциативной памяти для высокопро г изводительных систем параллельной обработки информации. Цель изобретения - расширение области применения и повышение быстродействия устройства. Ассоциативное запоминающее устройство содержит накопитель 1, регистр 2 данных, регистр 3 маски, группы элементов И 4i-4т1, 9i-9л (где п - число строк накопителя 1), регистр 5 сдвига, элемент ИЛИ 6, блок 7 приоритета, мультиплексор 8, дешифратор 10 адреса. Устройство является модулем блока ассоциативной памяти микропроцессорной вычислительной системы, причем выходы 15 и 16 используются для связи с соседними модулями, информационная шина 12 устройства подключена к информационной шине вычислительной системы, а входы 19 - к шине управления системы, вход 18 связан с источником синхроимпульсов системы, адресные входы 11 соединены с адресной шиной вычислительной системы. 4 ил. 1 табл. i (Л со 00 оо со 4 СО aius.1

Дешифратор 17 (фиг. 3) содержит соединенные соответствующим образом элементы НЕ 33-35, элементы И 36-51 и элементы ИЛИ 52 и 53.

Ассоциативное запоминающее устройство работает следующим образом.

Устройство является модулем блока ассоциативной памяти микропроцессорной вычислительной системы, причем выходы 15 и 16 используются для связи с соседними модулями, информационная шина 12 устройства подключена к информационной шине вычислительной системы, а входы 19 - к шине управления системы, вход 18 связан с источником синхроимпульсов системы, адресные входы 11 соединены с адресной шиной вычислительной системы.

Информация записывается в накопитель 1 подачей адреса ячейки, в которую должна быть произведена запись, на адресные входы 11 устройства. Сама информация при этом подается на информационную шину 12 устройства и поступает на информационные входы накопителя 1. Одновременно на управляющие входы 19 устройства подается код команды записи (в соответствии с таблицей указанный код равен 0001), по которому формируется единичный сигнал на выходе 28 дешифратора 17 команд. По единичному сигналу адрес, поданный на вход 11, через дешифратор 10 адреса и мультиплексор 8 поступает на входы выборки накопителя 1. Кроме того, на выходе 20 дешифратора 17 формируется единичный сигнал, по которому производится собственно запись информации с информационной шины 12 в выбранную строку накопителя 1. Если длина слова не превышает длины ячейки накопителя I, то каждое из записываемых слов заносится в соответствующую ячейку накопителя 1. Если длина информационного слова больше длины ячейки накопителя (последнюю удобно выбирать равной, например 9,17 и т. д. разрядам), то информационное слово записывается в несколько последовательно расположенных ячеек накопителя 1, причем в маркерный разряд первой ячейки, начиная с которой размещается слово, записывается единица, а в маркерные разряды последующих ячеек, в которые записывается слово, заносятся нули. Запись слова в ячейки накопителя 1 производится последовательно по частям, равным длине слова накопителя 1, с соответствующим изменением кода адреса, подаваемого на входы 11 устройства.

Таким образом, устройство позволяет отказаться от наращивания разрядности, а значит, и от шин поиска, выводимых за пределы микросхемы.

В режиме простого ассоциативного маскированного поиска на информационную щину 12 поступает аргумент поиска. Ввиду того, что процесс поиска в ситуации, когда формат данных меньше или равен длине ячейки накопителя 1, является частным случаем поиска при формате данных, превышающем длину ячейки накопителя 1, ниже

будет подробно рассмотрен процесс поиска для последнего из указанных случаев. На шину 12 подается старший слог информационного аргумента поиска (под слогом здесь и далее понимается часть информационного слова, разрядность которой на единицу меньше длины ячейки накопителя 1), причем на маркерный разряд шины 12 подается потенциал единичного уровня. Одновременно на входы 19 подается код

команды приема аргумента поиска (0010), по которому формируются единичные сигналы на выходах 26 и 23, которые инициируют соответственно запись кода с шины 12 на регистр 2 данных и установку всех разря5 дов регистра 5 в единицу.

В следующем такте (фиг. 4) на шину 12 подается старший слог маски. Одновременно на входы 19 устройства подается код команды опроса ассоциативного накопителя 1 (ООП), который вызывает формирование

0 единичных сигналов на выходе 22 дешифратора 17 команд, по которым осуществляется прием кода с шины 12 на регистр 3 маски, ассоциативный опрос ячеек накопителя 1 незамаскированными разрядами содер5 жимого регистра 2 данных (при совпадении немаскируемых разрядов регистра 2 данных с соответствующими разрядами содержимого ячейки накопителя 1 на выходе последнего формируется сигнал единичного уровня), прием кода с выходов накопителя 1 через

0 открытые элементы И 4 на регистр 5. В следующем такте (фиг. 4) на шину 12 поступает следующий за старшим (второй) слог слова-аргумента поиска, на маркерный разряд шины 12 подается потенциал нулевого уровня. Одновременно на входы 19 уст5 ройства подается код команды сдвига регистра 5 с приемом кода аргумента (0100), по которому на выходах 24 и 26 дешифратора 17 команд формируются сигналы единичного уровня, которыми код с шины 12 записывается на регистр 2 данных, а содержимое регистра 5 сдвигается влево на один разряд. Затем с приходом очередного тактового импульса, на шину 12 подается код второго слога маски, а на входы 19 - код команды опроса ассоциативного накопи5 теля (ООП), по которому производится ассоциативный опрос накопителя 1 с фиксацией сигналов совпадения на регистре 5. Совпадения фиксируются лишь в тех разрядах регистра 5, в которых записаны единицы. Для прочих разрядов регистра 5 соот0 ветствующие элементы И 4 оказываются закрытыми для прохождения сигналов с выходов накопителя 1, т. е. фиксируются лищь те совпадения содержимого ячеек накопителя I с незамаскированными разрядами второго слова информационного слова, которым

5 предшествовали совпадения содержимого ячеек с адресами, на единицу меньшими, и немаскированных разрядов первого слога

0

слова-аргумента поиска. Аналогично обрабатываются третий, четвертый и последующие слоги слова-аргумента поиска, вплоть до /-ГО, последнего. По завершении процесса ассоциативного простого маскируемого поиска единицами в разрядах регистра 5 будет отмечено положение последних слогов слов, хранящихся в накопителе 1, совпадающих в незамаскированных разрядах со словом-аргументом поиска. Если среди хранящихся в накопителе 1 слов не будет ни одного, отвечающего критерию поиска, то по окончании описанного процесса на выходе 14 устройства будет зафиксирован сигнал нулевого уровня.

Режим считывания информации осуществляется следующим образом.

Если считывание слов, выявленных в результате ассоциативного поиска, осуществляется со старщих разрядов, то необходимо предварительно /-1 раз (/ - число слогов в обрабатываемом слове) сдвинуть вправо содержимое регистра 5, для чего на входы 19 устройства необходимо /-1 раз подать код команды сдвига вправо содержимого регистра 5 (0101). При этом на выходах 21 и 25 дешифратора 17 команд формируются единичные сигналы, по которым соответственно открывается блок 13, подключающий выходы накопителя 1 к информационной шине 12, считывается из накопителя 1 слово, положение которого в накопителе 1 определяется кодом на выходе блока 7 приоритета, по заднему фронту синхроимпульса производится сдвиг вправо содержимого регистра 5. После цикла сдвигов начинается собственно считывание. Для этого /-1 раз на входы 19 устройства подают код ко.манды сдвига влево содержимого регистра 5 со считыванием (0110). При этом каждый раз сигналы единичного уровня формируются на выходах 21 и 24 дешифратора 17 команд, которые соответственно открывают блок 13 (при этом выходы накопителя 1 оказываются подключенными к информационной шине 12), инициируют считывание слова из ячейки накопителя 1, положение которой определяется кодом на выходе блока 7 приоритета, управляют сдвигом влево содержимого регистра 5. При считывании последнего, /-го, слога на входы 19 устройства подается код команды конца считывания (0111), по которому на выходах 21 и 27 дешифратора 17 команд формируются единичные сигналы, которые соответственно обеспечивают подключение блоком 13 выходов накопителя 1 к информационной шине 12 устройства, считывание содержимого ячейки накопителя 1, положение которой определяется кодом на выходе блока 7 приоритета, открывание элементов И 9 так, что код с выходов блока 7 приоритета, поступая на входы установки в нуль разрядов

регистра 5, сбрасывает в нуль первую единицу из числа записанных в регистре 5 по заднему фронту синхроимпульса. Таким образом, считанное слово исключается из числа зафиксированных на регистре 5 по окончании поиска. Аналогичным образом считывается второе, третье и т. д. слово. Процедура считывания продолжается до тех пор, пока все разряды регистра 5 не установятся в нуль, о чем свидетельствует появление нулевого потенциала на выходе 14 устройства.

Время считывания может быть существенно уменьшено если производить считывание слов поочередно, то начиная с млад5 ших разрядов, то начиная со старших разрядов, за счет исключения циклов начальной установки регистра 5.

Формула изобретения

Ассоциативное запоминающее устройство, содержащее накопитель, регистр данных, регистр маски, дещифратор команд, дещиф- ратор адреса, мультиплексор, регистр сдвига и блок выдачи информации, причем вход

5 признака поиска и вход маскирования накопителя подключены соответственно к выходам регистра данных и регистра маски, входы которых являются соответственно входом признака поиска и входом маскирования устройства, информационный выход накопи0 теля соединен с информационным входом блока выдачи информации, выходы которого являются информационными выходами первой группы устройства, информационный вход накопителя является информационным входом устройства, вход дешифратора адре5 са является адресным входом устройства, первый и второй входы дешифратора команд являются соответственно управляющим входом и входом синхронизации устройства, первый выход дешифратора команд подклюд чен к входу управления записью накопителя, второй выход дешифратора команд соединен с входом управления считыванием накопителя и управляющим входом блока выдачи информации, третий выход дешифратора команд подключен к входу управления

5 поиском накопителя, входу разрешения записи регистра маски и входу разрешения записи регистра сдвига, четвертый и пятый выходы дешифратора команд соединены соответственно с управляющим входом мультиплексора и входом разрешения записи ре0 гистра данных, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности его работы с переменным форматом слова и повышения быстродействия устройства, в него введены перва и вторая группы элемен- тов И, элемент ИЛИ и блок приоритета, причем первые входы элементов И первой группы подключены к выходам результата

поиска накопителя, вторые входы элементов И первой группы соединены с выходами разрядов регистра сдвига, выходы элементов И первой группы соединены с входами разрядов регистра сдвига, разрядные входы установки в «О которого подключены к выходам элементов И второй группы, выходы разрядов регистра сдвига соединены с соответствующими входами блока приоритета и входами элемента ИЛИ, выход которого является выходом результата поиска устройства, выходы блока приоритета подключены к информационным входам первой группы мультиплексора и первым входам элементов И

18

второй группы, вторые входы которых подключены к шестому входу дешифратора команд, с седьмого по девятый выходы дешифратора команд соединены соответственно с входом установки в «1, входом сдвига влево и входом сдвига вправо регистра сдвига, информационные входы второй группы мультиплексора соединены с выходами деи1ифра- тора адреса, выход мультиплексора соединен с входом выборки накопителя, выходы старшего и младшего разрядов регистра сдвига являются информационными выходами второй группы устройства.

28

%

-/

0

-г

О n-3 f

0

0

и

21

Q и 22

0 23

0 (

0

fJzs 0

U26

0

U27 0

U

0 и

0

ППЛППППППППП

n

/

1

ATI

/

QiDГ }Г

ПППП

iL a

/

| ИНЪЕКЦИОННЫЙ ПРЕПАРАТ ДЛЯ ПОВЫШЕНИЯ СПЕРМОПРОДУКЦИИ ЧЕЛОВЕКА И СПОСОБ ЕГО ПРИМЕНЕНИЯ | 2013 |

|

RU2526571C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| МАТЕРИАЛЫ НА ОСНОВЕ ПОЛИМЕРОВ ДЛЯ ОБРАБОТКИ СПОСОБОМ ПОСЛОЙНОГО СИНТЕЗА | 2017 |

|

RU2712575C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1988-04-15—Публикация

1986-09-01—Подача