(54) УСТРОЙСТВО для СЖАТИЯ ПОЛОСЫ ЧАСТОТ ТЕЛЕВИЗИОННОГО СИГНАЛА

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2004 |

|

RU2287909C2 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ВИДЕОСИГНАЛА | 1992 |

|

RU2042201C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ВИДЕОСИГНАЛА | 1992 |

|

RU2042202C1 |

| Устройство для счета количества изображений объекта | 1987 |

|

SU1494021A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТНЫЙ ДИСКРИМИНАТОР | 1996 |

|

RU2143182C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ВИДЕОСИГНАЛА | 1992 |

|

RU2042203C1 |

| Устройство для определения положения кристалла | 1983 |

|

SU1175304A1 |

| Устройство для контроля видеосигнала | 1982 |

|

SU1069190A1 |

| Стереотелевизионная камера с автоматической фокусировкой | 1989 |

|

SU1774518A1 |

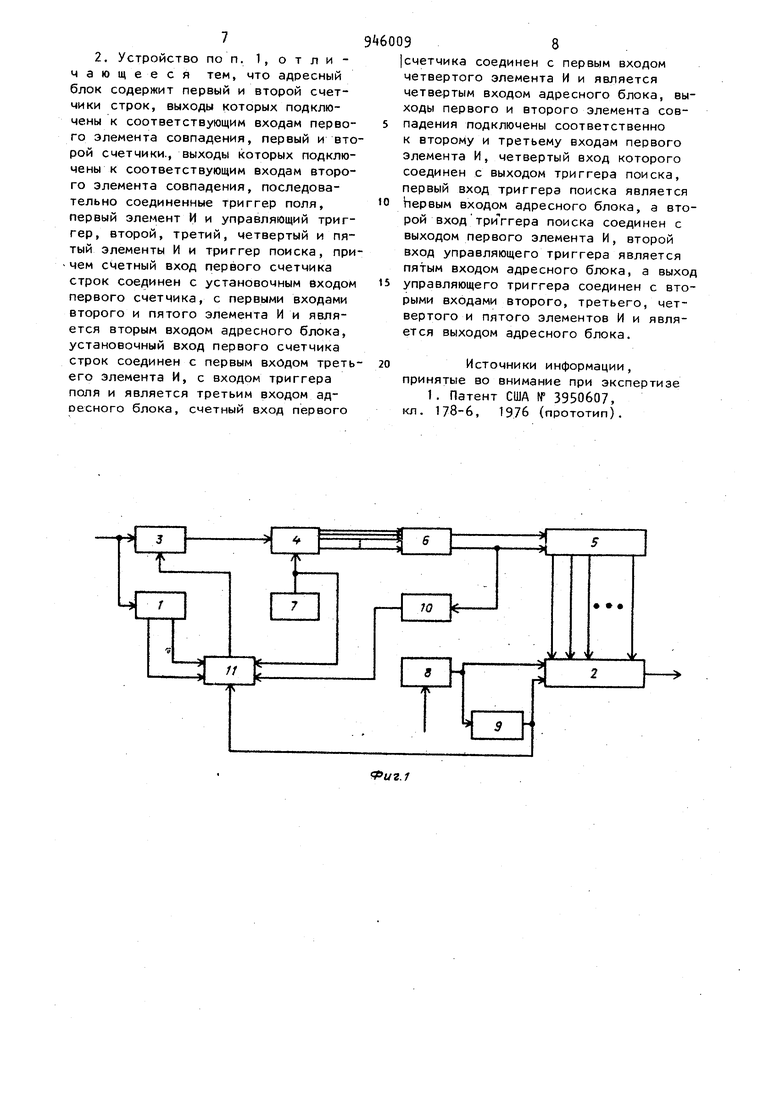

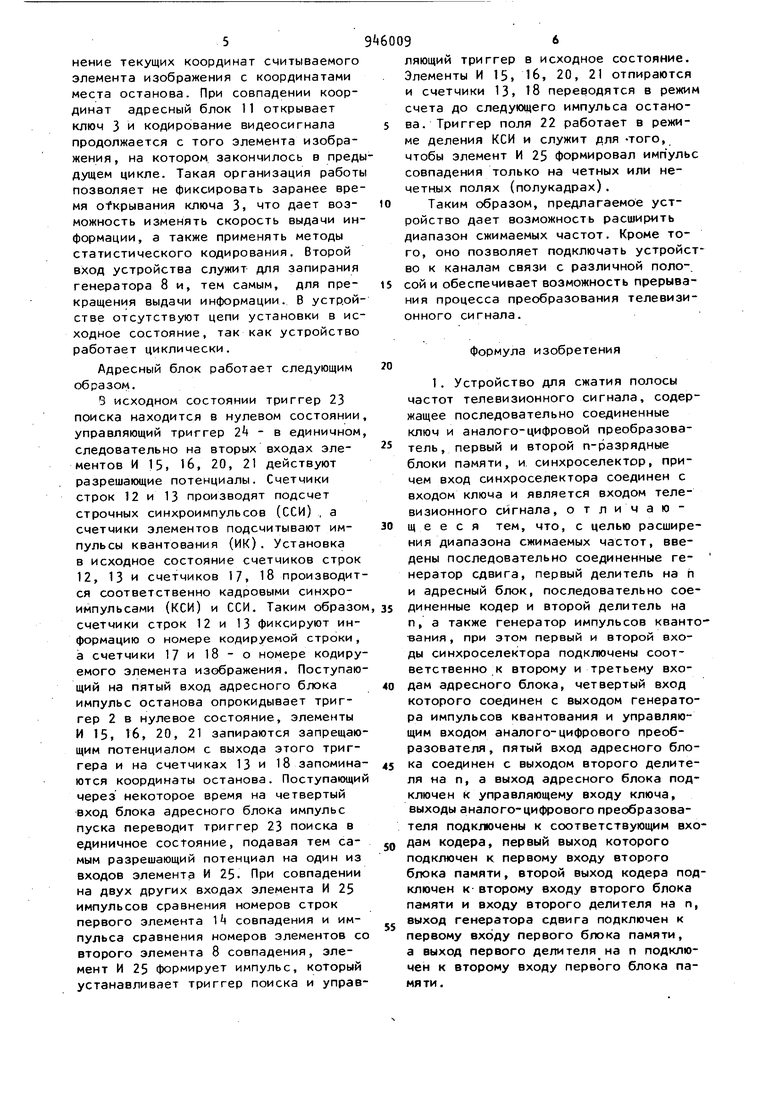

Изобретение относится к телевизионной технике и может быть использовано для передачи по узкополосным каналам связи статических и медленно изменяющихся изображений. Известно устройство для сжатия по лосы частот телевизионного сигнала, содержащее последовательно соединенные ключ и аналого-цифровой преобразователь, первый и второй п-разрядные блоки памяти, и синхроселектор, причем вход синхросилектора соединен с входом ключа и является входом телевизионного сигнала l . Недостатками данного устройства являются (1)иксированная полоса частот выходного сигнала, не позволяющая подключать устройство к каналам связи с различной полосой, а также ограниченный диапазон сжимаемых частот Цель изобретения - расширение диа пазона сжимаемых частот. Поставленная цель достигается тем что в устройство для сжатия полосы частот телевизионного сигнала, содержащее последовательно соединенные ключ и аналого-цифровой преобразователь , первый и второй п-разрядные блоки памяти, и синхроселектор, причем вход синхроселектора соединен с входом ключа и является входом телевизионного сигнала, введены последовательно соединенные генератор сдвига, первый делитель на п и адресный блок, посдедовательно соединенные кодер и второй делитель на п, а также генератор импульсов квантования, при этом первый и второй входы синхроселектора подключены соответственно к второму и третьему входам адресного блока, четвертый вход которого соединен с . выходом генератора импульсов квантования и управляющим входом аналогоцифрового преобразователя, пятый вход адресного блока соединен с выходом второго делителя на п, а выход адресного блока подключен к- управляющему входу ключа, выходы аналого-цифрового преобразователя подключены к соответствующим входам кодера, первый выход которого подключен к перво му входу второго блока памяти, второй выход кодера подключен к второму входу второго блока памяти и входу второго делителя на п, выход генератора сдвига подключен к первому вход первого блока памяти, а выход первог делителя на п подключен к второму входу первого блока памяти. При этом адресный блок содержит первый и второй счетчики строк, выходы которых подключены к соответствующим входам первого элемента совпа дения, первый и второй счетчики, выходы которых подключены к соответствующим входам второго элемента совпадения, последовательно соединенные триггер поля, первый элемент И и управляющий триггер, второй, третий, четвертый и пятый элементы И и триггер поиска, причем счетный вход перв го счетчика строк соединен с установочным входом первого счетчика, с пе выми входами второго и пятого элемента И и является вторым входом адресного блока, установочный .вход первого счетчика строк соединен с первым входом третьего элемента И, с входом триггера поля и является третьим входом адресного блока, счетный вход пер вого счетчика соединен с первым входом четвертого элемента И и является четвертым входом адресного блока, выходы первого и второго элемента совпа дения подключены соответственно к вто рому и третьему входам первого элемента И, четвертый вход которого соединен с выходом триггера поиска, первый вход триггера поиска является первым входом адресного блока, а второй вход триггера поиска соединен с выходом первого элемента И, второй вход управляющего триггера является пятым входом адресного блока, а выход управляющего триггера соединен с вторыми входами второго, третьего, четвертого и пятого элементов И и являет ся выходом адресного блока. На фиг. 1 представлена структурная

схема устройства для сжатия полосы частот телевизионного сигнала; на фиг. 2 - функциональная схема адресного блока.

Устройство для сжатия полосы частот телевизионного сигнала содержит синхроселектор 1, первый блок 2 памяти , ключ 3,аналого-цифровой преобблок 2 памяти.

Время переписки -информации существенно меньше периода следования импульсов сдвига и следовательно информация поступает на выход устройства непрерывно. Импульс пуска первого с делителя на п 9 поступает так же на адресный блок 11, где начинается сравразователь (АЦП) 4, второй блок 5 памяти, кодер 6, генератор 7 импульсов квантования, генератор 8 сдвига, первый делитель на п 9, второй делитель на п 10 и адресный блок 11, причем адресный блок включает в себя первый 12и второй 13 счетчики строк, первый элемент lA совпадения, третий 15 и второй 16 элементы И, первый 17 и второй 18 счетчики, второй элемент 19 совпадения, пятый 20 и четвертый 21 элементы И, триггер 22 поля, триггер 23 поиска, управляющий триггер 2 и первый элемент И 25Устройство для сжатия полосы час-. TQT телевизионного сигнала работает следующим образом. Телевизионный сигнал поступает от источника на ключ 3 и синхроселектор 1. После ключа аналоговый видеосигнал преобразуется АЦП k в цифровую форму и поступает на кодер 6. Генератор 7 импульсов квантования служит для управления временным квантованием сигнала в АЦП 4. Кодер 6 кодирует видеосигнал по одному из известных алгоритмов статистического сжатия. Закодированный сигнал с первого выхода кодера 6 поступает на первый вход второго блока 5 памяти последовательным кодом, а на второй.вход второго блока 5 памяти поступают импульсы сдвига, формируемые кодером 6. После п импульсов сдвига п-разрядный второй блок 5 памяти оказывается заполненным, и второй делитель на п 10 формирует импульс останова, поступающий на адресный блок 11. По этому импульсу адресный блок закрывает ключ 3 и производит запоминание координат места остановки (номер строки и номер элемента разложения на строке). Импульсы генератора 8 сдвига информацию из первого блока 2 памяти списывают последовательным кодом на выход устройства. После очистки первого блока памяти,т.е. после п тактов сдвига, первый делитель на п переводит первый блок памяти в режиме записи и очередная порция информации из второго блока 5 памяти переписывается в первый нение текущих координат считываемого элемента изображения с координатами места останова. При совпадении координат адресный блок 11 открывает ключ 3 и кодирование видеосигнала продолжается с того элемента изображения, на котором, закончилось в пред дущем цикле. Такая организация работ позволяет не фиксировать заранее вре мя ofкpывaния ключа 3. что дает возможность изменять скорость выдачи ин формации, а также применять методы статистического кодирования. Второй вход устройства служит для запирания генератора 8 и, тем самым, для прекращения выдачи информации. В устрой стве отсутствуют цепи установки в ис ходное состояние, так как устройство работает циклически. Адресный блок работает следующим образом. В исходном состоянии триггер 23 поиска находится в нулевом состоянии управляющий триггер Zt - в единичном следовательно на вторых входах элементов И 15, 16, 20, 21 действуют разрешающие потенциалы. Счетчики строк 12 и 13 производят подсчет строчных синхроимпульсов (ССИ) , а счетчики элементов подсчитывают импульсы квантования (ИК). Установка в исходное состояние счетчиков строк 12, 13 и счетчиков 17, 18 производит ся соответственно кадровыми синхроимпульсами (КСИ) и ССИ, Таким образом счетчики строк 12 и 13 фиксируют информацию о номере кодируемой строки, а счетчики 17 и 18 - о номере кодируемого элемента изображения. Поступающий на пятый вход адресного блока импульс останова опрокидывает три|- гер 2 в нулевое состояние, элементы И 15, Тб, 20, 21 запираются запрещающим потенциалом с выхода этого триггера и на счетчиках 13 и 18 запоминаются координаты останова. Поступающий через некоторое время на четвертый вход блока адресного блока импульс пуска переводит триггер 23 поиска в единичное состояние, подавая тем самым разрешающий потенциал на один из входов элемента И 25. При совпадении на двух других входах элемента И 25 импульсов сравнения номеров строк первого элемента совпадения и импульса сравнения номеров элементов со второго элемента 8 совпадения, элемент И 25 формирует импульс, который устанавливает триггер поиска и управляющий триггер в исходное состояние. Элементы И 15, 16, 20, 21 отпираются и счетчики 13, 18 переводятся в режим счета до следующего импульса останова. Триггер поля 22 работает в режиме деления КСИ и служит для -того, чтобы элемент И 25 формировал импульс совпадения только на четных или нечетных полях (полукадрах). Таким образом, предлагаемое устройство дает возможность расширить диапазон сжимаемых частот. Кроме того, оно позволяет подключать устройство к каналам связи с различной поло-, сой и обеспечивает возможность прерывания процесса преобразования телевизионного сигнала. Формула изобретения 1. Устройство для сжатия полосы частот телевизионного сигнала, содержащее последовательно соединенные ключ и аналого-цифровой преобразователь , первый и второй п-разрядные блоки памяти, и синхроселектор, причем вход синхроселектора соединен с входом ключа и является входом телевизионного сигнала, отличающееся тем, что, с целью расширения диапазона сжимаемых частот, введены последовательно соединенные генератор сдвига, первый делитель на h и адресный блок, последовательно соединенные кодер и второй делитель на п, а также генератор импульсов квантования, при этом первый и второй входы синхроселектора подключены соответственно к второму и третьему входам адресного блока, четвертый вход которого соединен с выходом генератора импульсов квантования и управляющим входом аналого-цифрового преобразователя , пятый вход адресного блока соединен с выходом второго делителя на п, а выход адресного блока подключен к управляющему входу ключа, выходы аналого-цифрового преобразователя подключены к соответствующим входам кодера, первый выход которого подключен к первому входу второго блока памяти, второй выход кодера подключен к второму входу второго блока памяти и входу второго делителя на п, выход генератора сдвига подключен к первому входу первого блока памяти, а выход первого делителя на п подключен к второму ВХОДУ первого блока паяти. 7 2. Устройство по п. 1, о т л и чающееся тем, что адресный блок содержит первый и второй счетчики строк, выходы которых подключены к соответствующим входам первого элемента совпадения, первый и вто рой счетчики., выходы которых подключены к соответствующим входам второго элемента совпадения, последовательно соединенные Триггер поля, первый элемент И и управляющий триггер, второй, третий, четвертый и пятый элементы И и триггер поиска, при -чем счетный вход первого сметчика строк соединен с установочным входом первого счетчика, с первыми входами второго и пятого элемента И и является вторым входом адресного блока, установочный вход первого счетчика строк соединен с первым входом треть его элемента И, с входом триггера поля и является третьим входом адоесного блока, счетный вход первого

-г( 9 счетчика соединен с первым входом четвертого элемента И и является четвертым входом адресного блока, выходы первого и второго элемента совпадения подключены соответственно к второму и третьему входам первого элемента И, четвертый вход которого соединен с выходом триггера поиска, первый вход триггера поиска является первым входом адресного блока, а второй вход поиска соединен с выходом первого элемента И, второй вход управляющего триггера является пятым входом адресного блока, а выход управляющего триггера соединен с вторыми входами второго, третьего, четвертого и пятого элементов И и является выходом адресного блока. Источники информации, принятые во внимание при экспертизе 1. Патент США № 3950607, кл. 178-6, 1976 (прототип).

ts м

Авторы

Даты

1982-07-23—Публикация

1981-02-19—Подача