Изобретение относится к рйдейной защите и автоматизации электрических систем с помощью сравнения фаз сигналов и мо/хет бить использовано в реле направления.:мощности, реле сопротивления и других фазочувствительных реле-.

Известно устройство для сравнения фаз дву:с электрических величин, выполненное по способу сравнения времени совпадения их знаков с временем несовпадения, содержащее блок совпадения, интегратор, двусторонний ограничитель вьксодного напряжения инте.гратора и пороговЕ1й элемент, выполненнцй на операционном усилителе 13

Устройство, содержащее только один интегратор, не различает coBrtaдение положительных знаков сравниваемых величин от совпадения их отрицательнызс знаков. Вследствие этого оно имеет недостаточно высокую помехоустойчивость , так как может сработать ложно при наличии аперирдической составляющей хотя бы в одной из величин.

Наиболее близким к предлагаемому по технической сущности является устройство для сравнения фаз двух электрических величин, солержацее

блоки совпадения положительных и .отрицательных знаков сравниваешлх пеличин, два интегратора и два двусторонних ограничителя напряжения, подкл1зченных к выходам интеграторов, между выходами которых и пороговым элементом включается аналоговый сумматор t21 .

Недостат1сом устройства является

10 его сложность, обусловленная необходимостью формирования одинаковых знаков у напряжений, поступаюсщх на входа сумматора.

Цель изобретения - упрощение его

15 конструкции.

Поставленная цель достигается тем, что в устройстве для сравнения фаз двух электрических величин, содержгидем блоки совпадения положи20тельных и отрицательных знаков, два интегратора, входы которы:с подключены к выходам блоков совпадения, а выходы - к двусторонним ограничителям напряжения, и операционный

25 усилитель, между выходом первого интегратора и выводом источника питания и между выходом второго интегра тора и выходом операционного усилителя включены делит€1ли напряжения,

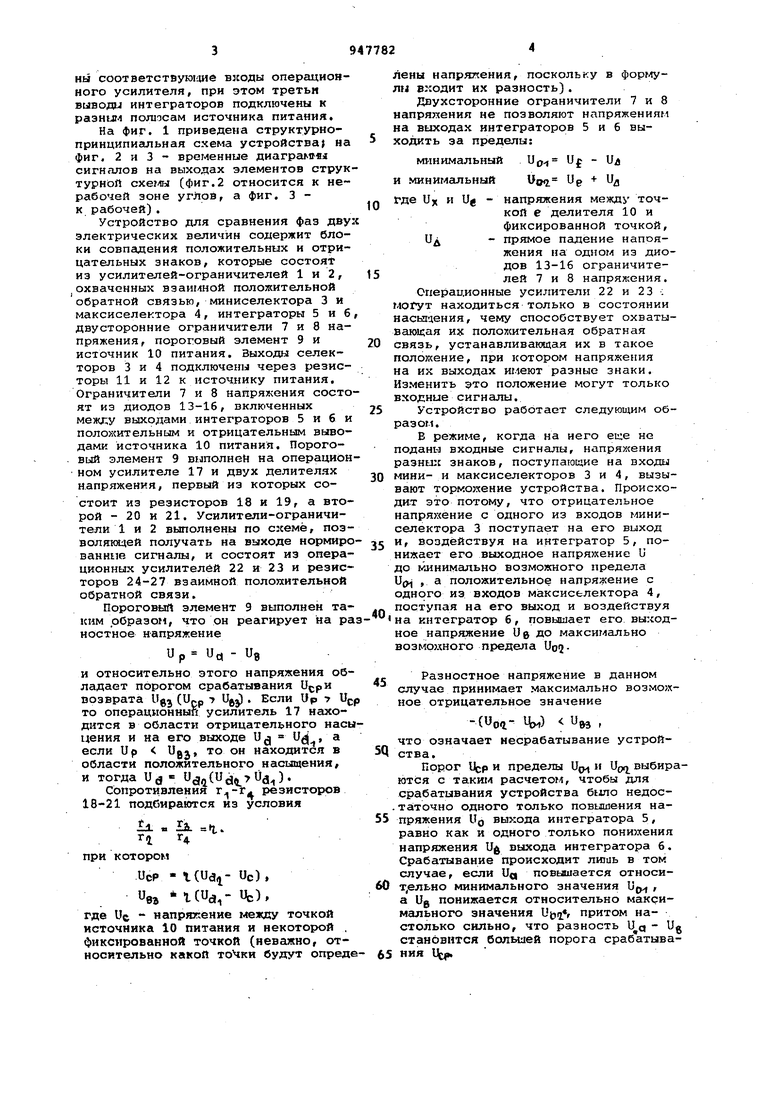

30 к средним выводам которых подключены соответствуюгдие входы операционного усилителя, при этом третьи выводи интеграторов подключены к раэшлл полюсам источиика питания. На фиг. 1 приведена структурноприиципигипьная схема устройства) на фиг. 2 и 3 - временные диаграмгял сигналов на выходах элементов струк турной cxei-iH (фиг.2 относится к нерабочей зоне углов, а фиг. 3 к рабочей). Устройство для сравнения фаз дву электрических величин содержит блоки совпсщения положительных и отрицательных знаков, которые состоят из усилителей-ограничителей 1 и 2, охваченных взаимной положительной обратной связью, миниселектора 3 и максиселектора 4, интеграторы 5 и 6 двусторонние ограничители 7 и 8 напряжения , пороговый элемент 9 и источник 10 питания. Выходы селекторов 3 и 4 подключены через резисторы 11 и 12 к источнику питания. Ограничители 7 и 8 напряжения состо ят из диодов 13-16, включенных меж/;у выходами интеграторов 5 и 6 и положительным и отрицательным выводами источника 10 питания. Пороговый элемент 9 выполнен на операцион ном усилителе 17 и двух делителях напряжения, первый из которых состоит из резисторов 18 и 19, а второй - 20 и 21. Усилители-ограничители 1 и 2 выполнены по схеме, позволяющей получать на выходе нормиро ваннив сигналы, и состоят из операционных усилителей 22 и 23 и резисторов 24-27 взаимной положительной обратной связи. Пороговый элемент 9 выполнен таким образом, что он реагирует на ра ностное напряжение Up Uc, - Ue и относительно этого напряжения обладает порогом срабатывания возврата Ugj(Upp 7 U . Если Up 7 U то операционный усилитель 17 находится в области отрицательного насы цения и на его выходе t если Up Ug., то он находится в области положительного насыщения, и тогда и а - d) Сопротивления резисторов 18-21 подбираются из условия 1л. . а. 1. г Г4 при котором UCP - Uc), ea l(Udr «с) где Uc напрягчение 1№жду точкой источника 10 питания и некоторой , фиксированной точкой (неважно, относительно какой точки будут опреде лены напряжения, поскольку в форглулч входит их разность). Двухсторонние ограничители 7 и 8 напряжения не позволяют напряжениям на выходах интеграторов 5 и б выходить за пределы: минимальный Uo-i Lf л и минимальный о Up - Uj где Ujj и Ug - напряжения между точкой е делителя 10 и фиксированной точкой, Цд - прямое падение напояжения на одном из диодов 13-16 ограничителей 7 и 8 напряжения. Операционные усилители 22 и 23 ; могут находиться только в состоянии насьпдения, чему способствует охватывающая их положительная обратная связь, устанавливающая их в такое положение, при котором напряжения на их выходах имеют разные знаки. Изменить это положение могут только входные сигналы. Устройство работает следующим образом. В режиме, когда на него еи:е не поданы входные сигналы, напряхсения разных знаков, поступающие на входы мини- и максиселекторов 3 и 4, вызывают тормозхение устройства. Происходит это потому, что отрицательное напряжение с одного из входов миниселектора 3 поступает на его выход и, воздействуя на интегратор 5, понижает его выходное напряжение U до минимально возможного предела U0 , а положительное напряжение с одного из входов максиселектора 4, поступая на его выход и воздействуя на интегратор 6, повышает его выходное напряжение 60 до максимально возмохшого предела UOQРазностное напряжение в данном случае принимает максимально возможное отрицательное значение -(Uoa- Цм) UM что означает несрабатывание устройства. Порог И пределы U(j и Upij, выбираются с таким расчетом, чтобы для срабатывания устройства было недоста1точно одного только повышения напряжения UQ выхода интегратора 5, равно как и одного только понижения напряжения } выхода интегратора б. Срабатывание происходит лишь в том случае, если UQ повыиается относит,ельно минимсшьного значения Up, , а Ug понижается относительно максимального значения Ujjij;, притом настолько сильно, что разность - Ug становится больыей порога срабатывания

При подаче на вход одной из сравниваемых величин с амплитудой напряжения, превышающей напряжение установки на резисторе 24, всякий раз, когда U превысит уставку, операционный усилитель 22 будет переключаться, изменяя знак своего выходного напряжения, а следовательно, и напряжения уставки второй величины, падающего на резисторе 26. В результате операционный усилитель 23 начнет переключаться почти одновременно с операционным усилителем 22, так что их выходные напряжения, несмотря на работу в режиме переключения, будут по-прежнему разнопоЛЯРНЫ14И. Напряжение на выходе интегратора 5 остается равшли Ц, а интегратор 6 - Ц,7 и состояние порогового элемента 9 не изменяется.

Когда на вход1л устройства поданы обе сравниваемие величины U и Ui, причем их амплитуды превышают соответствующие напряжения уставок на резисторах 24 и 26, Может сложиться ситуация, приводящая к срабатыванию устройства. Для этого необходимо, чтобы интервалы совпадения знаков сравниваемых величин имели достаточно большую продолжительность. Пусть

есть наименьшая длительность

тервсша совпадения t., при которой срабатывает устройство. Время t(4{.соответствует разности фаз величин и к ifj, абсолютную величину которой обозначим 1Чр1. При |Ч I I rt интервал совпадения t будет больше, чем . , следовательно, зоной работы устройства является область углов - Иг К Ч- , |Чг|.

В течение периода изменения сравниваемых величин встречаются два интервала совпадения их знаков (положительных и отрицательных). На той части каждого интервгша совпадения, где напряжения U и U) превышают соответствующие напряжения уставок на резисторах 24 и 26, напряжения на выходах операционных усилителей 22 и 23 приобретают одинаковую полярность. Заметим, что взаимная положительная обратная связь на резисторах 24-27 стремится изменить такое положение и, как только одно из напряжений и-,или Vt понизится настолько, что станет меньше напряжения уставки, соответствующий операционный усилитель 22 или 23 сразу же переключится, изменив к тому же полярность напряжения уставки оставшегося операционного усилителя и помогая er«iy тем ca.ым сохранить свое состояние.

На тЬй части интервала совпадения положительных знаков сравниваег/их величин, где напряжения U и и, достаточно велики, оба выходных напря-жения операционных усилителей 22

и 23 становятся положительными. Поступая на входы мини- и максиселектора 3 и 4,они приводят к , что выходные напряжения селекторов, как и., так и U., также становятся положительного знака. Для максисе-. лектора 4 это обычная полярность, стремящаяся повысить напряжение выхода чнтегратора 6 U g вплоть до значения Uj,, . Но для миниселектора 3 это новая полярность, возможная только в указанных виде условиях. Она приводит к постепенного повышению напряжения выхода интегратора 5 Ud от его минимального уровня максимального UQ Хотя напряжние U0 повышается лииь на части интервала совпадения положительных знако.в и II и, а в любое другое вр{ЛЯ понижается, оно тем не .-менее .может подняться достаточно высоко поскольку его повышение происходит меньшей постоянной времени, чем понижение.

На той части интервала совпащени отрицательных знаков U и U(j, где эти величины достаточно велики по абсолютному значению, оба выходных напряжения операционных усилителей 22 ч 23 становятся отрицательныгли. Как следствие, будут отрицательны и выходные напряжения миниселектора 3 и, для которого эта полярность обычна, и максиселектора 4 U., для которого она возможна только в указанны условиях, в это время напряжние U0 выхода интегратора б U понижается вплоть до значения Ug, а в любое другое время оно будет повышаться, но с большей постоянной времени.

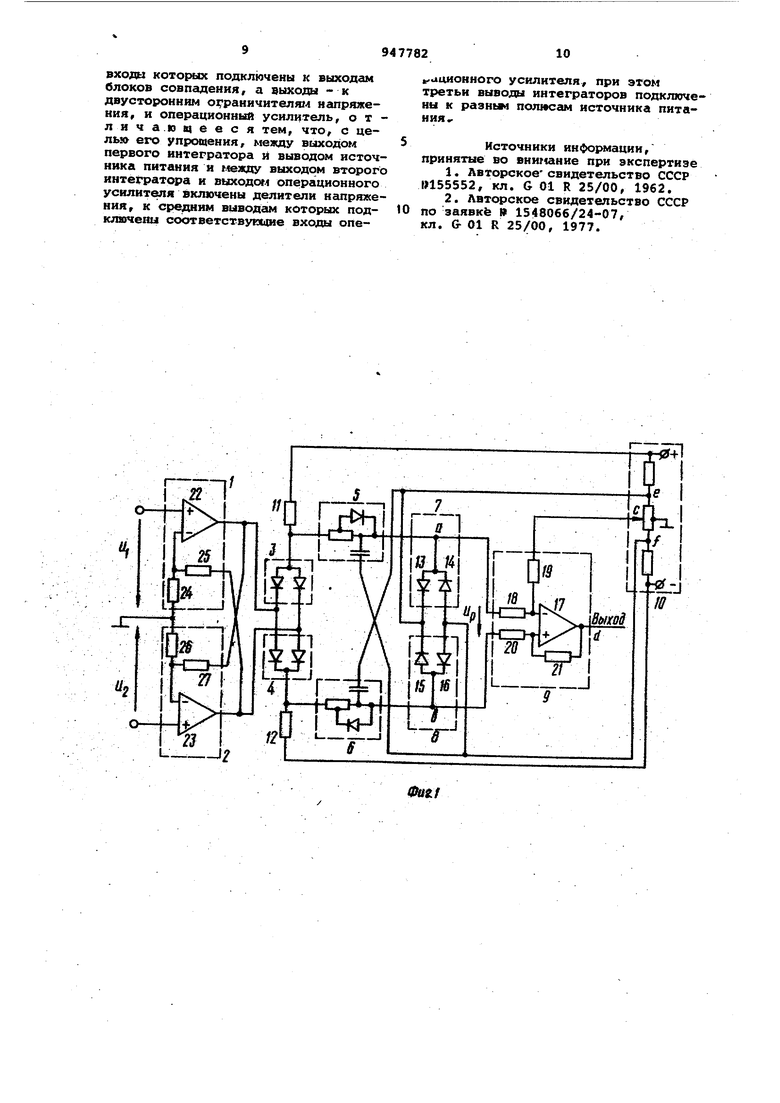

Диаграммы фиг. 2 и 3 построены для разных значений разности фаз элемента 9 между входныг.ш величинами и и Llj,

на фиг. 2р |Ч1 7|ЧгГсоответств енно

t -IrHLxt .

с. - ш ст.

на фиг. 26

ц| frl-cL,

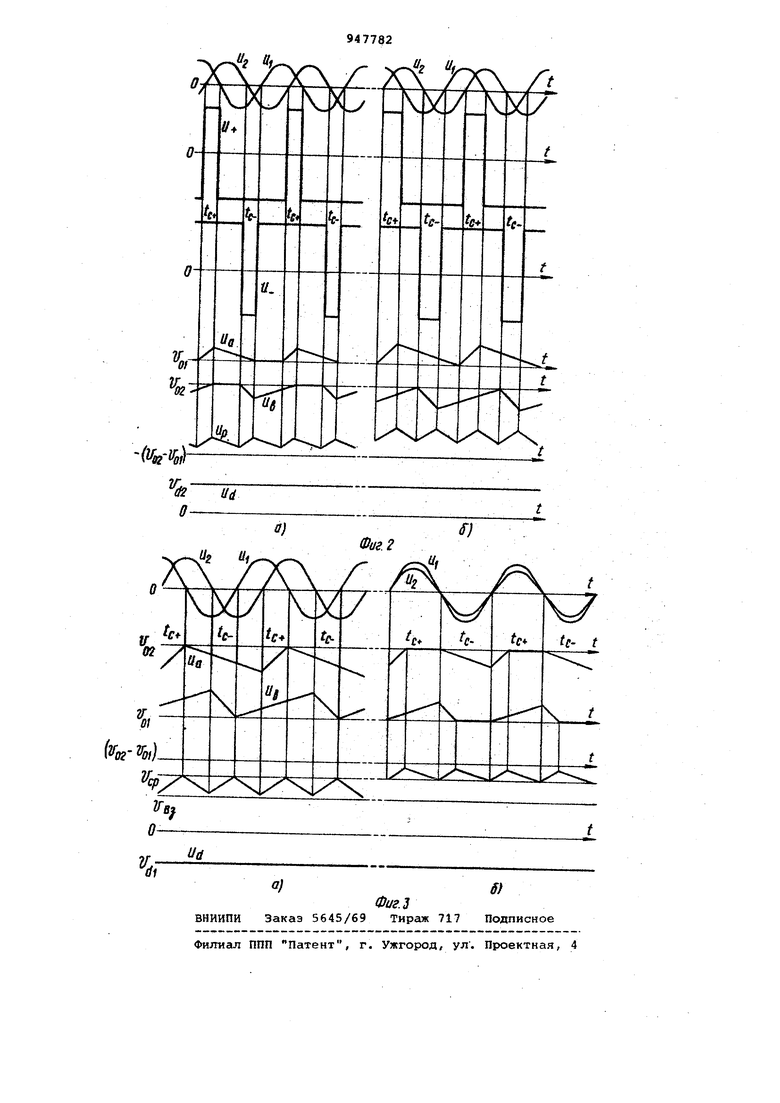

где oL и л t - малые величины, на фиг.За

,

на фиг. 3 S - f 0.

Для большей наглядности временных диаграг.с при их построении принято, что напряжения уставок на резисторах 24 и 26 несравненно меньше амплитуд величин и и IJ, вследствие чего уставки можно считать нулевыми. При этом условии выходное напряжение Миниселектора 3 1)4 положительно на всем интервале совпадения полояи5 тельных знаков величин U-t и Uij., обозначенном t. , и отрицательно в остапьное время, а выходное напряже ние максиселектора 4 U отрицательн на всем интервале совпадения отрицательных знаков величин U, обозначенном t , и положительно в остальное время. Как следствие, выходное напряжение и интегратора 5 на интервалах t может повышаться вплоть-до предела UQI, а в остально время оно может понижаться вплоть до предела Up. Аналогично, выходно напряжение Ug интегратора 6 на интервалах t может понижаться вплоть до предела Up, а в остальное время оно .может повышаться вплоть до предела UQIJ. Если разность фаз Ч находится в нерабочей зоне углов (фиг.2 ), то напря ; ение 1}, возросшее за время tt-f успевает .понизиться до предела Uj раньше, чем наступит следуюций интервал t, . Аналогично, напряжение и, понизившееся за время tc- успевает повыситься до предела раньше, чем наступит следующий ин тервал t(, , Образно говоря, кривая и у не в состоянии оторваться от ниж него предела , а Ug - от верхнего предела UOQ, В непосредственной близости от границы рабочей зоны (фиг.2е) повышение напряжения U0 на одном интервале tc+ равно его понижение за вре мя, проходящее до следующего интервала t(-+ а понижение напряжения Ug на одном интервале tp равно его по вышению за BpeHfi - проходящее до сле дующего интервала t. Незначительное уменьшение значения |Ч1 по сравнению с тем, для которого справедливо фиг.2 б , приводит к тому, что в течение периода повышение напряжения UQ, будет преоб ладать над его понижени.ем и, наоборот, понижение напряжения Uj будет преобладать нещ его повьЕшеннем. В результате от периода к периоду напряжение UQ будет все более возрастать, а напряжение U все более понижаться, и,-наконец, первое достигает верхнего предела Utii.i второе - нижнего UQ, после чего процесс устанавливается (фиг.З ). Даль нейшее уменьшение угла вплоть до нуля (фиг.З Б) приводит к тому, что напряжения U , и U j,, не отходя от достигнутых йределов, несколько уменьшают, свои пульсации. Разностное напряжение Up пульсирует с удвоенной частотой. Оно .повы шается на интервалах совпадения (как tf4, так и t.-) и понижается в остальное врегля. В нерабочей зоне углов (фиг.2 оно находится вблизи отрицательного значения -(и.ог еи а R рабочей зоне (фиг.З) - вблизи поло-:; и тельного значения (Uoi- Hoi ) . Когда максимальное значение напряжсНИН Up поднимается до порога U(p , элемент 9 сработает, а когда минимальное значение опустится до порога Ugj, возвратится. Пороги и Ugjустанавливаются таким образом, что при разности фаз между сравниваемыми величинами, равной IWrf , максимум напрял;ения Up равен , а минимум несколько больше Uea (фиг.3d). При такой настройке исключается вибрация устройства на краю рабочей зоны. С уменьшением Wi мaкcи /Iyмы напряжения Up будут заведомо больше Uj,p , а минимумы эаведоМО больше ч пульсации напряжения Up уменьшаются (фиг.З). , Закон изменения напрях;ения Up не зависит от того, к какой точке делителя напряхсения питания подключен третий вывод интегратора 5 или 6. Точки е и f выбраны в данном случае лишь с тем расчетоп, чтобы сразу после подачи напряжения питания, пока конденсаторы интеграторов 5 и б еще не заряжены, обеспечивалось условие Up -(Uc - Uf) вЬ устанавливающее пороговый элемент 9 в состояние несрабатывания независимо от полярности выходные: напряженна селекторов 3 и 4. В предлагаемом устройстве, сохранившем достоинства прототипа, удалось отказаться от использования сумматора и инвертора. Несмотря на функциональную сложность, устройство построено всего лшиь на трех операщионных усилителя :. Такое упрощение Вс1жно потому/ что оно повышает надехсность устройства и снижает его стоимость. С другой стороны, реализация устройства на палом числе операционных усилителей снижает потребляемый им постоянный ток, что особенно важ.но в случае его использования Б качестве автономного реле направления мощности, которое на подстанциях питается оперативны напряжением 220 В. Положительный эффект достигнут благодаря построению , при котором пороговый элемент приобретает свойства триггера с дифференциальны входом и подключается поэтому непосредственно к выходам интеграторов, а также за счет использования блоков совпадения с нормированньйли выходными сигналами. Форглула изобретения Устройство для сравнения фаз двух электрических величин, содержащее блоки совпадения положительных и отрицательных знаков, два интегратора.

входы которых подключены к выходам блоков совпадения, а выходы - к двусторонним ограничителя - напряжения, и операционный усилитель, о т лича.юцееся тем, что, с целы его упрощения, между выходом первого иитерратора и выводом источника питания и feждy выходом второго интегратора и выходогл операционного усилителя включены делители нгшряжения, к средним выводам которьос подклнгаеиы соответствующие входы опек ациоиного усилителя, при этом третьи выводы интеграторов подключены к разньм полпсгш источника питания

Источники информации, принятые во вниг1ание при экспертизе

1.Авторское свидетельство СССР №155552, кл. G 01 R 25/00, 1962.

2.Авторское свидетельство СССР по заявке If 1548066/24-07,

кл. G- 01 R 25/00, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения фазэлЕКТРичЕСКиХ ВЕличиН | 1979 |

|

SU813578A1 |

| Устройство для моделирования импульсного датчика частоты вращения | 1985 |

|

SU1251118A2 |

| Программная следящая система | 1981 |

|

SU1108394A1 |

| Устройство для управления четырехфазным двигателем переменного тока | 1980 |

|

SU886182A1 |

| Устройство для моделированияиМпульСНОгО дАТчиКА чАСТОТы ВРАщЕНия | 1979 |

|

SU849245A1 |

| Устройство управления приводом балансировочного стенда | 1982 |

|

SU1118962A2 |

| Устройство управления приводом балансировочного стенда | 1982 |

|

SU1019396A1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Широтно-импульсный преобразователь | 1986 |

|

SU1413715A1 |

| Реле времени | 1975 |

|

SU657476A1 |

Авторы

Даты

1982-07-30—Публикация

1980-11-17—Подача