(54) СТОХАСТИЧЕСКОЕ ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Стохастическое делительное устройство | 1979 |

|

SU796857A1 |

| Цифро-вероятностное устройство для деления чисел | 1978 |

|

SU771675A1 |

| Стохастический цифровой функциональный преобразователь | 1977 |

|

SU612249A1 |

| Вероятностное устройство для возведения в квадрат | 1979 |

|

SU857991A1 |

| Вероятностное устройство для умножения матриц | 1982 |

|

SU1056192A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Преобразователь код-вероятность | 1973 |

|

SU450153A1 |

| Вероятностное устройство для деления чисел | 1981 |

|

SU962939A1 |

| Стохастическое вычислительное устройство | 1981 |

|

SU982004A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

Изобретение относится к вычислительной технике и предназначается для выполнения операции деления чидсел. в стохастических вьтчислив

тельных машинах ().

Известны стохастические делительные устройства, содержащие преобразователи код-вероятность, счетчики, логические элементы И, ИЛИ, НЕ, сумматоры, элементыузадержки Ll3, 2 и З.

Недостатком данных устройств является низкая точность вычислений, что вызвано применением метода одноразрядного вероятностного кодирования чисел А и В.

Наиболее близким к предлагаемому является стохастическое делительное ус тройство, содержащее блок задержк, сумматор, преобразователь код-вероятность, блок умножения, блок инвертирования, входы которого соединены с разрядными шинами кода делителя, а выходы - с первой группой входов блока умножения, первая группа выходов которого подключена к второй группе входов сумматора, первая группа входов которого соединена с разрядными шинами кода делимого, а выходы - с выходами устройства t4.

Недостатком известного устройства является также низкая точность выполнения операции деления.

Цель изобретения - повышение точности деления.

Поставленная цель достигается тем, что в стохастическом делительном

10 устройстве, содержащем блок инвертирования, входы которого являются разрядными входами делителя устройства, блэк умножения, первая .группа входов которого соединена с выходами

15 блока инвертирования, сумматор, первая группа входов которого является разрядными входами делимого устройства, вторая группа входов соединена с выходами младших разрядов блока ум20ножения, а выходы являются выходами устройства, преобразователь код-вероятность и блок задержки, входы блока задержки соединены с выходами сумматора, а выходы - с второй

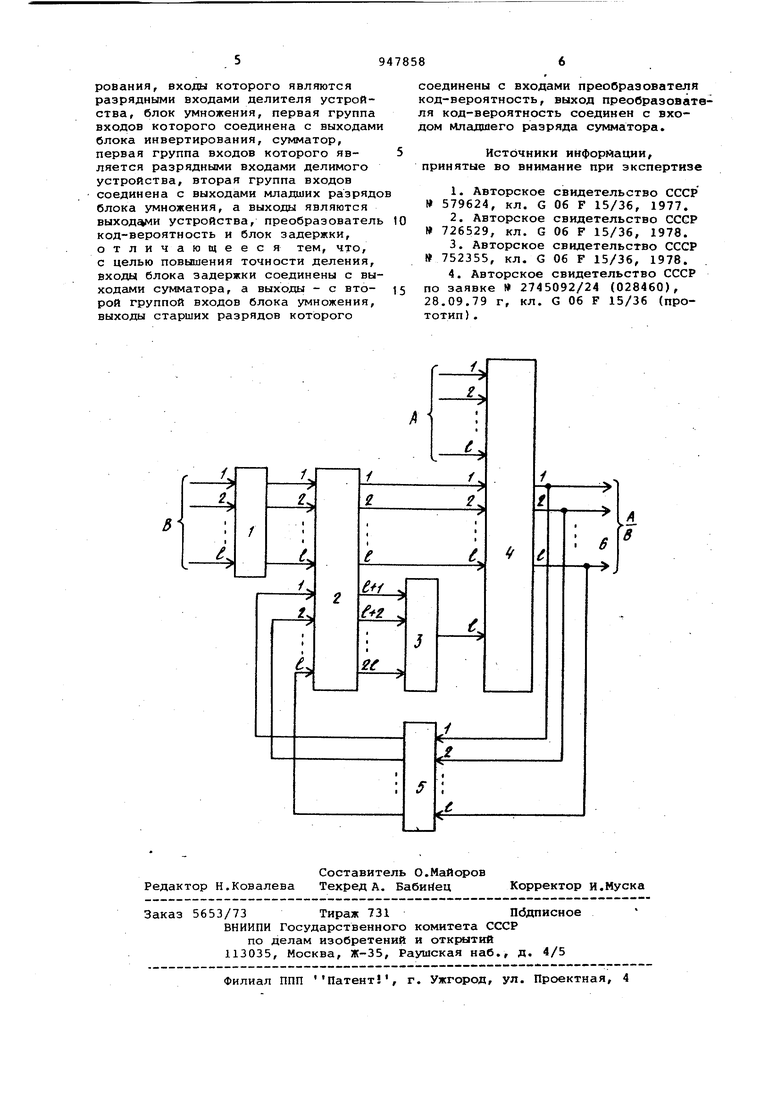

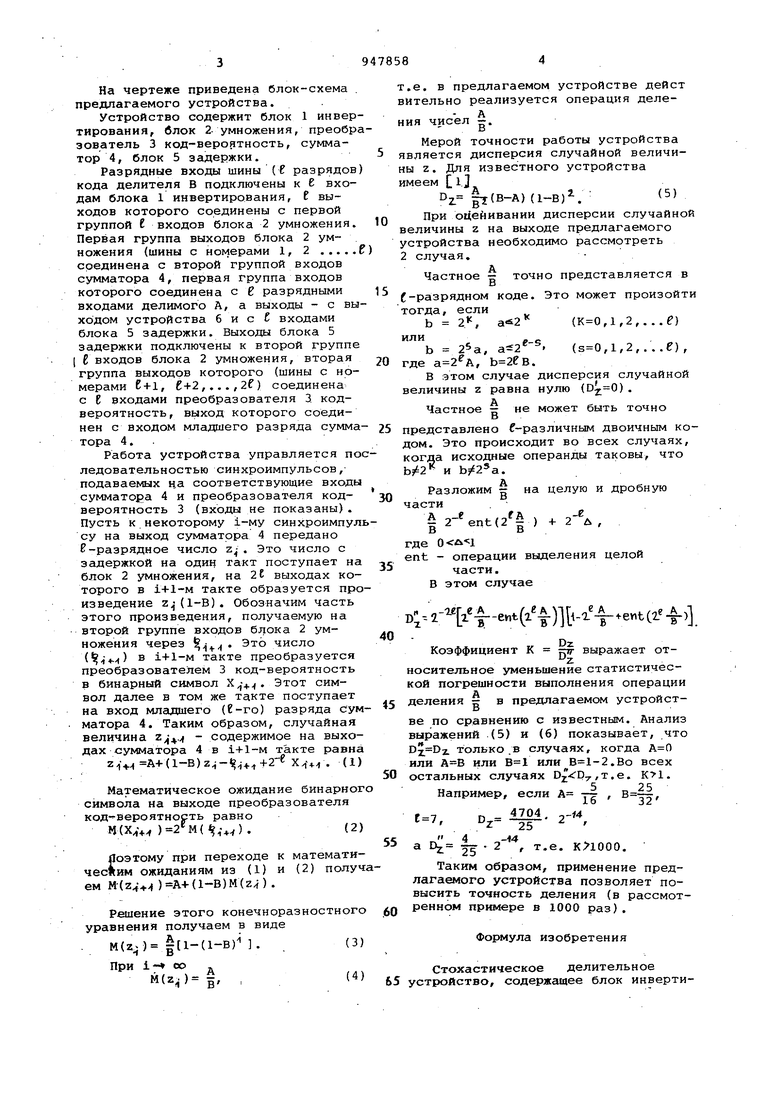

25 группой входов блока умножения, выходы старших разрядов которого соединены с входами преобразователя код-вероятность, выход преобразователя код-вероятность соединен с вхо30дом младшего разряда сумматора. На чертеже приведена блок-схема предлагаемого устройства. Устройство содержит блок 1 инвер тирования, блок 2- умножения, преобр зователь 3 код-вероятность, сумматор 4, блок 5 задержки. Разрядные входы шины (С разрядов кода делителя В подключены к В входам блока 1 инвертирования, Е выходов которого соединены с первой группой t входов блока 2 умножения. Первая группа выходов блока 2 умножения (шины с номерами 1, 2 соединена с второй группой входов сумматора 4, первая группа входов которого соединена с 6 разрядными входами делимого А, а выходы - с вы ходом устройства б и с С входами блока 5 задержки. Выходы блока 5 задержки подключены к второй группе I входов блока 2 умножения, вторая группа выходов которого (шины с номерами С+1, 6+2,...,2f) соединена с Е входами преобразователя 3. кодвероятность, выход которого соединен с входом младшего разряда сумма тора 4. . Работа устройства управляется по ледовательностью синхроимпульсов , подаваемых на соответствующие входы сумматора 4 и преобразователя кодвероятность 3 (входы не показаны). Пусть к.некоторому i-му синхроимпул су на выход сумматора 4 передано Р-разрядное число z. Это число с задержкой на один такт поступает на блок 2 умножения, на 2 выходах которого в i+1-м такте образуется пр изведение z(l-B). Обозначим часть этого произведения, получаемую на второй группе входов блока 2 умножения через . Это число () i+1-м такте преобразуется преобразователем 3 код-вероятность в бинарный символ .. Этот символ далее в том же такте поступает на вход младшего (6-го) разряда сум матора 4. Таким образом, случайная величина г. - содержимое на выходах сумматора 4 в i+1-м такте равна (-B) . (1 Математическое ожидание бинарно символа на выходе преобразователя код-Вероятность равно «( )(1,ч).(2 Поэтому при переходе к математи ческим ожиданиям из (1) и (2) полу ем M-(z )A+(l-B)M(z) . Решение этого конечноразностног уравнения получаем в виде M(zj) (1-В) . При i- сэо M(z)§, .е. в предлагаемом устройстве деист ительно реализуется операция делеАия чисел -. Мерой точности работы устройства является дисперсия случайной величиы Z. Для известного устройства меем 1 DZ Sl(B-A)(1-В). При оцейивании дисперсии случайной величины Z на выходе предлагаемого устройства необходимо рассмотреть 2 случая. Частное - точно представляется в в f-разрядном коде. Это может произойти тогда, если Ь 2, (,1,2,...е) или Ь , (,1,2 ,. . .) , где , . В этом случае дисперсия случайной величины Z равна нулю (). Частное - не может быть точно представлено f-различным двоичным кодом. Это происходит во всех случаях, когда исходные операнды таковы, что и . Разложим на целую и дробную части I (2| ) + , где ent - операции выделения целой части. В этом случае в;-2 Л- f-eHt(),.a.ev,tCi i-) Коэффициент К |г выражает относительное уменьшение статистической погрешности выполнения операции деления - в предлагаемом устройстве по сравнению с известным. Анализ выражений .(5) и (6) показывает, что . только.в случаях, когда или или или .Во всех остальных случаях Dy-srp.;., т. е. . 5 25 Например, если А 4 14 а Ог: 2 , т.е. . Таким образом, применение предлагаемого устройства позволяет повысить точность деления (в рассмотренном примере в 1000 раз). Формула изобретения Стохастическое делительное устройство, содержащее блок инвертирования, входы которого являются разрядными входами делителя устройства, блок умножения, первая группа входов которого соединена с выходами блока инвертирования, сумматор, первая группа входов которого является разрядными входами делимого устройства, вторая группа входов соединена с выходами младших разрядо блока умножения, а выходы являются выходами устройства, преобразователь код-вероятность и блок задержки, отличающееся тем, что, с целью повышения точности деления, йходы блока задержки соединены с выходами сумматора, а выходы - с второй группой входов блока умножения, выходы старших разрядов которого

соединены с входами преобразователя код-вероятность, выход преобразователя код-вероятность соединен с входом Младшего разряда сумматора.

Источники информации, принятые во внимание при экспертизе

5

А

в

Авторы

Даты

1982-07-30—Публикация

1980-10-29—Подача