(54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ОПТИМИЗАЦИОННЫХ ЗАДАЧ СТАНДАРТИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выбора оптимальных типоразмерных рядов | 1978 |

|

SU696495A1 |

| Устройство для решения задач типа балансирования сборочной линии | 1983 |

|

SU1167622A1 |

| Устройство для моделирования распределения материальных ресурсов | 1983 |

|

SU1125631A1 |

| Устройство для контроля блоков постоянной памяти | 1975 |

|

SU668008A1 |

| Устройство для планирования последовательности выполнения работ | 1985 |

|

SU1267404A1 |

| Устройство для вычисления оптимального распределения нагрузок на теплоэлектростанции | 1972 |

|

SU485491A1 |

| УСТРОЙСТВО ДЛЯ ФИЗИЧЕСКОГО МОДЕЛИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ СХЕМ | 1969 |

|

SU255665A1 |

| ОБУЧАЮЩАЯ МАШИНА | 1973 |

|

SU388295A1 |

| Устройство для автоматического адресования грузов | 1972 |

|

SU477914A1 |

| МАШИНА ЯЛЯ ОБУЧЕНИЯ И КОНТРОЛЯ ЗНАНИЙ | 1973 |

|

SU389543A1 |

Изобретение относится к вычислительной технике и может быть использовано для решения оптимизационныхмногомерных задач стандартизации.

Известно устройство для выбора оптимальных параметрических рядов, содержащее переключатель, счетчик, линии задержки, элементы ИЛИ, триггеры, элементы И, блоки индикации 1

Недостатком данного устройства является сложная структура устройства.

Наиболее близким к предлагаемому является устройство для выбора оптимальных типоразмеров рядов, содержащее блок задания исходных данных, блок решающих усилителей, блок инверторов, блок сравнения, коммутатор, блок управления, блок индикации 2.

Недостатком известного устройства является сложная функциональная структура устройства.

Цель изобретения - упрощение функциональной схемы стройства.

Поставленная цель достигается тем, что в устройстве для решения оптимизационных задач стандартизации, содержащем блок задания исходных данных, выход которого соединен с первым информационным входом решающего блока, управляющий вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с управляющим входом блока задания исходных данных, третий выход блока синхронизации соединен с управляющим входом блока сравнения, четвертый выход блока синхронизации подключен к управляющему входу блока

10 индикации, выход решающего блока соединен с информационньм входо блока сравнения, информационный выход которого подключен к второму информационному входу решающего бло15ка, управляющий выход блока сравнения соединен с первым входом блока синхронизации, второй вход которого, соединен с выходом блока задания исходных данных, третий вход блока

20 синхронизации подключен к выходу блока индикации.

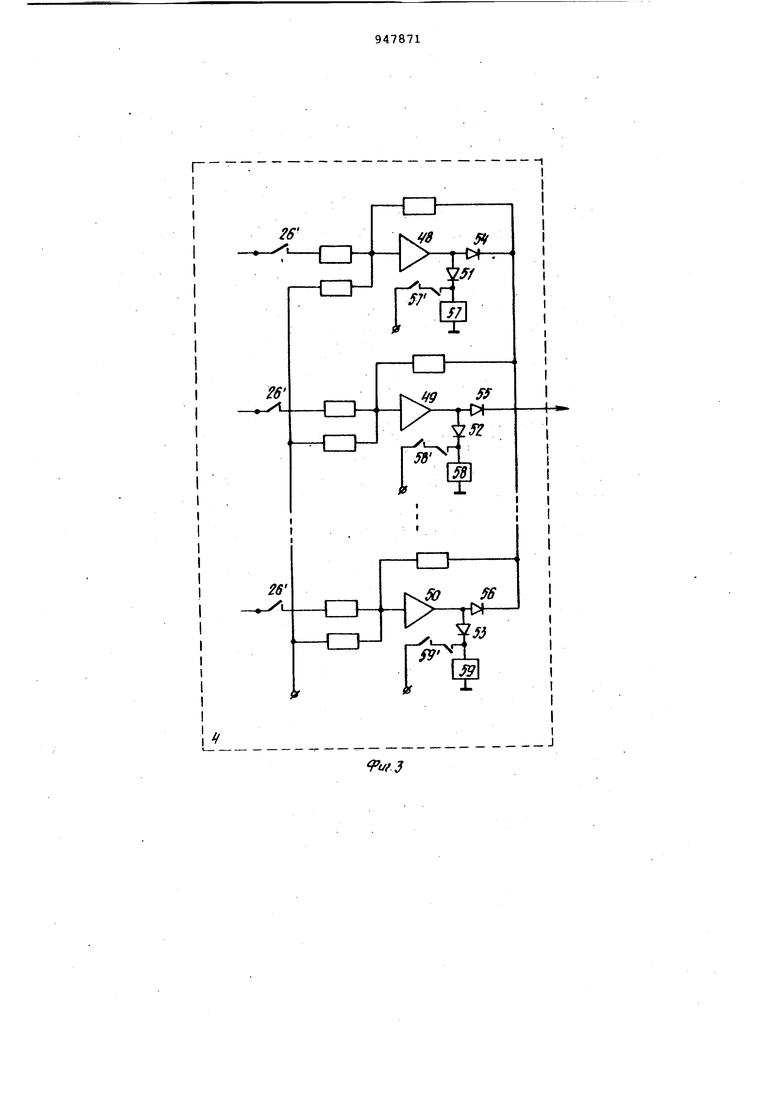

На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 25 блок-схема предлагаемого устройства с учетом внутренней структуры блоков задания исходных данных, блока синхронизации и решающего блока; на фиг.З - схема блока сравнения; на

30 фиг . 4 - блок индикации. Устройство для решения оптимизационных задач стандартизации содержит блок 1 задания исходных данных, блок 2 -синхронизации, решающий блок 3, блок 4 сравнения, блок 5 индикации . Блок 1 задания исходных данных преддтавляет собой матрицу размером ((т ж п) + т) резисторов, из которых m X п резисторов, пронумерованных (фиг.2) цифрами 6-11, служат для установки на них напряжений, пропорцио .нальных величинам .затрат () на изготовление и эксплуатацию типа i в количестве ,), необходимом для выполнения -ой функции, am резисторов, обозначенных (фиг.2) цифрами 12- 14 для установки напряжений, пропорциональных затратам () на разработку одного 1-го изделия, т.е. начальным затратам. Для контроля значений устанавливаемых напряжений используется измерительный прибор необходимого класса точности. Блок 2 синхронизации служит для управления процессом решения задачи и состоит из двух шаговых искателей .15 и 16, реле 17 с контактом 17 для включения шаговых искателей в кнопки Пуск, а также двух групп реле,- в одной из -которых имеются ре (18-26) по количеству-резисторов в блоке задания исходных данных,- с контактами 18- 26, а в другой (2744) - по два реле, на каждую лампу блока индикации с контактами 27- 4 Решающий блок включает в себя m опе рационных усилителей (фиг,2), пронумерованных цифрами 45 - 47 и предназначен для сул1мирования напряжений соответствующих эксплуатационным затратам (), с .напряжениями, соответствукадими начальным затратам , и с напряжением сигнала, вьаделенного блок:ом сравнения. Блок сравнения включает в себя m .операционных усилителей, обозначенных (фиг.З) цифрами 48 - 50, диоды 51-56.-К выходам усилителе-й 48-50 через диоды 51-53 подключены реле минимума 57 .59 с контактами 57- 59 и служит для выделения минимального/ соответ ствующего минимальному элементу, сигнала в столбце. Елок индикации репгения состоит из т, у. п индикаторных ламп (60-68) , подключенных к общей схеме, причем каждая лампа включается в соответст вии с выбранным в -; -ом столбце эле ментом. Устройство для региения -оптимизационных многомерных задач стандарти зации реализует следующий алгоритм. Последовательно во всех столбцах матрицы //с/;// затрат выбирается минимальный элемент , причем столбец выбирается в виде С--- если минимл.. ьHlifi элемент одного цл предЕэщущих столбцов находится в 1-оП строке; если в 1-ой строке -,,«. для предыдущих столбцов нет минимальных элементов. Устройство работает следующим образом. Приведение устройства в исходное состояние осуществляется отк.лючением его от источника питания и последующим включением в питающую сеть ., На резисторах 6-11 блока задания исходных данных (1) устанавливаются напряжения, соответствующие экспуатацион ным затратам с, (1 1,т, J 1,п), а на резисторах 12-14 напряжения, соответств у1С1цие начальным затратам (i l,m). В исходном состоянии переключатели шаговых искателей 15 и 16 блока 2 синхронизации находятся, в положении (п+1) и (т+1) соответственно. Нажимается . кнопка Hycjc блока 2 синхронизации. Срабатывает реле 17, самоблокируется своими контактами и включает в работу шаговые искатели 15 и 16. Бегунок шагового искателя 15 заI. За время замкмыкает контакт нутого состояния контакта любого другого искателя 15 бегунок шагового искателя 16 пробегает по всем своим (т+1) .контактам. Таким образом, последовательно срабатывает реле 18и24, 19и 25,...20 и 26, замыкаются их контахты, и напряжения с резисторов п-ервого столбца блока задания исходных данных (1) поступают на первые входы решающего 3 блока. Одновременно с этим на вторые входы решающего блока поступают напряжения, соответствующие начальным затратам, с резисторов 12-1.4. При замыкании т-го контакта шагового искателя 16 и срабатывании реле 26 замыкается-его группа контактов, стоящих во входных цепях блока 4 сравнения. Напряжения с вы-, ходов решающего блока поступают одновременно на соответствующие усилители блока сравнения. При последовательном срабатывании реле 18 - 20 замыкаются и соответствующие им контакты, стоящие в цепях блока игщикации, которые подключают к питанию реле 27 - 29. В результате срабатывания этих реле замыкаются их контакты 27 - 29j которые подготавливают к работе цепи питания ламп 60 - 62 блока индикации (5). В блоке сравнения происходит вьщеление минимального сигнала, который поступает на входы блока решающих усилителей. При выделении минимального элемента первого столбца срабатывает реле минимума (57 или 58, или ..., или 59) на выходе того операционног усилителя (48 или 49, или ...,или 5 в котором был записан минимальный сигнал. В результате этого замыкают ся нормально разомкнутые контакты (57 или 58, или ..., или 59) данного реле минимума, которые находятся, во входных цепях ламп 61-68 блока индикации. Соответствующая лампа индикации включается в сеть. Оказывается подключенным к сети и соответствующее.реле 36 или 37, или ..., или 38. В результате срабатывания реле его контакты замыкаются, и соответствующая лампа индикации оказываетс постоянно подключенной к сети .(происходит блоки1)овка контактов реле минимума). Каждое реле минимума имеет и по одной паре нормально замк.нутых контактов (57- 59), стоящих в цепях снятия сигналов, соответствующих начальным затратам, т.е. в цепях резисторов 12-14. При ВЕДцелении минимального элемента в столбце, т.е. при включении соответствующего реле минимума, эти контакты размыкаются, в результате чего один из резисторов 12 или 13, или ..,, или 14, а именно тот, который стоит в строке выделенного минимального эле мента, отключается и в дальнейшей работе схемы не участвует. При переходе бегунка шагового ис кателя 15 в положение 2 весь описанный цикл повторяется, только снятие сигналов происходит с резис торов второго столбца блока задания исходных данных, а в блоке решающих усилителей суммирование уже трех сигналов - двух прежних и минимального сигнала, поступившего с выхода блока сравнения. Процесс решения згшеряиается, когда бегунок шагового искателя 15 обежит все (п+1) контактов. В блоке индикации решения останутся включенными лампы, соответствующие элементам, вошедшим в оптимальное решение. Предлагаемое устройство благодаря наличию новых связей позволяет решать оптимизационные задачи стандартизации и отличается простой внутренней структурой. Формула изобретения Устройство для {эешения оптимизационных задач стандартизации, содержащее блок задания исходных данных, выход которого соединен с первьли информационным входом решающего блока, управляющий вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с управляющим входом блока задания исходных данных,третии выход блока синхронизации соединен с управляющим входом блока сравнения, четвертый выход блока синхронизации подключен к управляющему входу блока индикации, отличающееся тем, что, с целью упрощения устройства, выход решающего блока соединен с информационным входом блока сравнения, информационный выход которого подключен к второму информационному входу решающего блока, управляющий выход блока сравнения соединен с первым входом блока синхронизации, второй вход которого соединен с выходом блока задания исходных данных, третий вход блока синхронизации подключен к выходу блока индикации. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 790001, кл. G 06 G 7/122, 1979. 2.Авторское свидетельство СССР 696495, кл. G 06 G 7/48, 1979 (прототип).

J

Г

Г

1

Авторы

Даты

1982-07-30—Публикация

1980-09-12—Подача