(54) МНОГОКАНАЛЬНЫЙ РАСПРЕДЕЛИТЕЛЬ СИГНАЛОВ (ЕГО ВАРИАНТЫ)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство с динамическим выбором маршрутов передачи данных | 1987 |

|

SU1587529A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Устройство для коммутации информационных каналов | 1981 |

|

SU1003123A1 |

| ЭЛЕКТРОННЫЙ АДРЕСНЫЙ АВТОМАТ ДЛЯ ПРОГРАММНОГО | 1968 |

|

SU231228A1 |

| Фотоэлектрический преобразователь перемещений в код | 1982 |

|

SU1037311A1 |

| Устройство для определения объема выборки параметров контроля | 1986 |

|

SU1416979A1 |

| Информационно-измерительное устройство | 1985 |

|

SU1256074A1 |

| Устройство для диагностирования троированных дискретных схем автоматики | 1990 |

|

SU1772783A1 |

| Адаптивный многоканальный коммутатор | 1990 |

|

SU1800606A1 |

| Устройство для управления многоканальной измерительной системой | 1983 |

|

SU1149255A1 |

Изобретение относи.тся к ,вычислительной технике и автоматике и может быть использовано при построе- НИИ быстродействующих устройств управления цифровьах систем.

Известен многоканальный распределитель импульсов, содержащий коммутирующий триггер, схему совпадений, вспомогательный распределитель импульсов и ,Ц-выходных счетных триг-. геров 1.

Однако этот распределитель не обладает достаточным быстродействием из-за требования синхронизации запуска.

Известен также многоканальный распределитель импульсов, содержащий многоразрядный счетчик на триггерах, выполненный в виде трех отдельных счетчиков, промежуточный и основной дешифраторы 2,

Однако этот распределитель также не обладает достаточным быстродейстгвием.

Наиболее близким по технической сущности к данному изобретению является распределитель, содержащий счетчики коммутации строк и столбцов, промежуточные дешифраторы строк

и столбцов, матрицу элементов И и генератор тактовых импульсов L3 J.

Однако данный распределитель также не обладает необходимым быстродействием, так как не обеспечивает получения перекрывающейся временной диаграммы выходных сигналов.

Цель изобретения - повышение быстродействия многоканального распределителя сигналов.

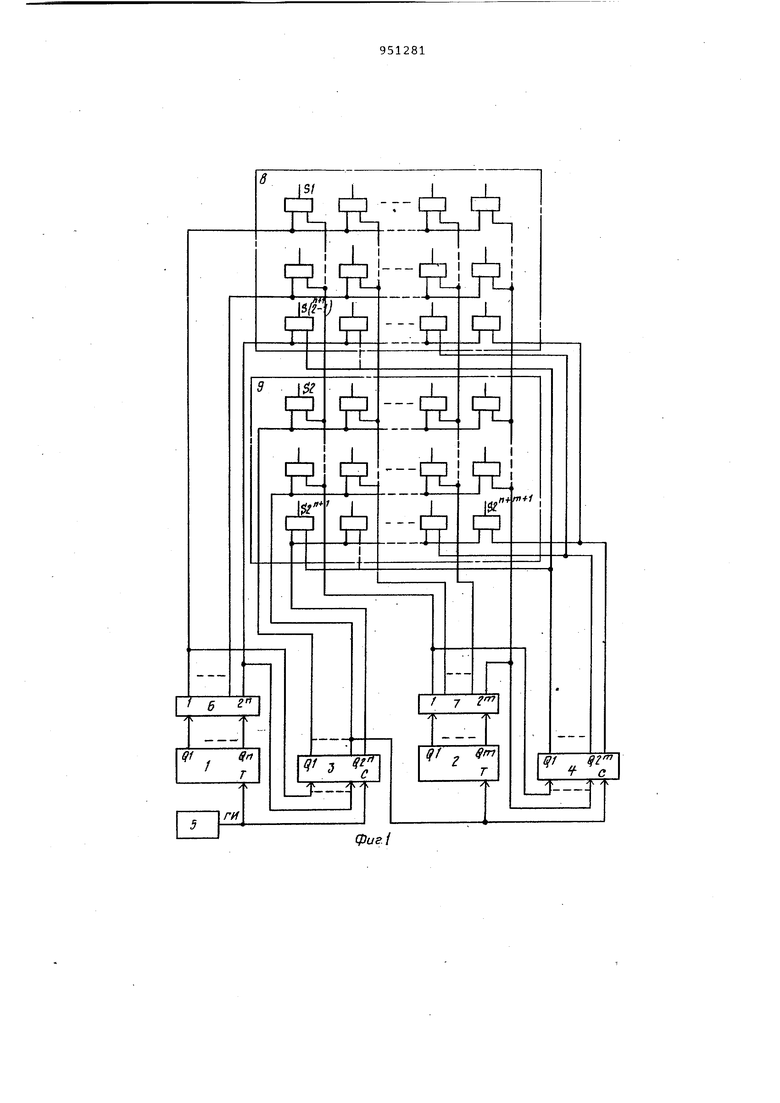

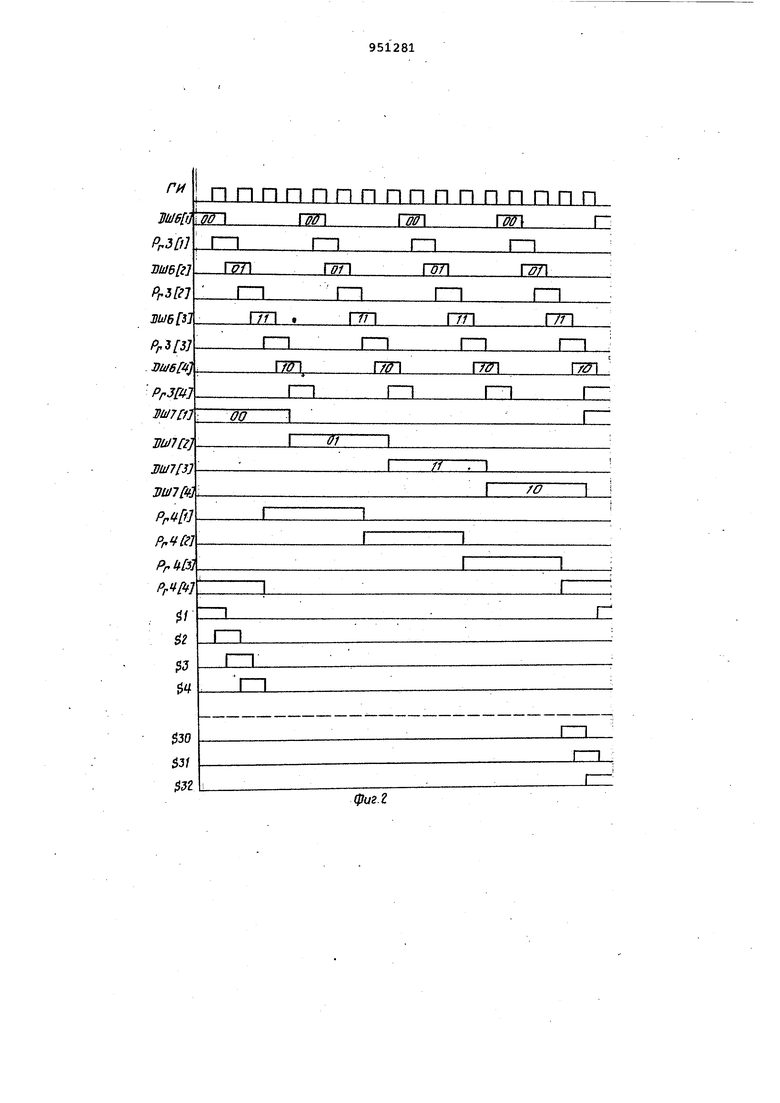

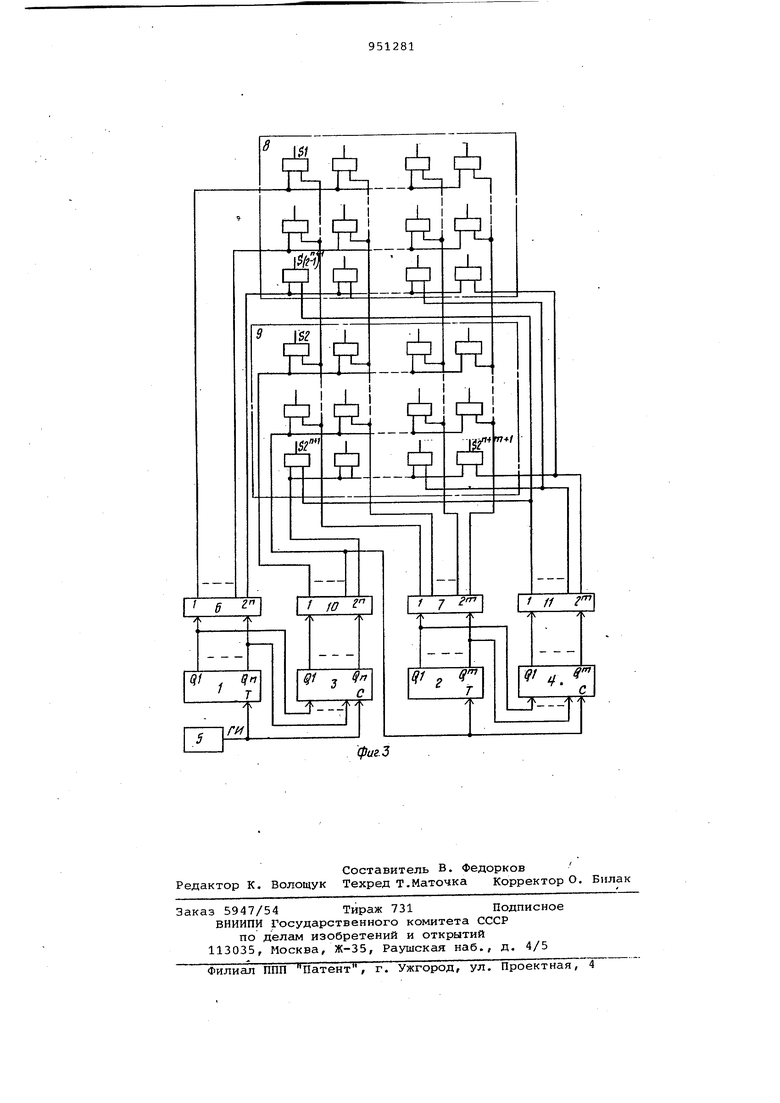

Поставленная 11ель достигается тем, что многоканальный распределитель сигналов, содержащий счетчики коммутации строк и столбцов, промежуточные дешифраторы строк и столбцов, матрицу элементов И и генератор тактовых импульсов, выход которого подключен к входу счетчика коммутации строк, выхрды разрядов которого соединены с входами промежуточного дешифратора строк, выходы которого соединены с первыми входами элементов И соответствующих строк матрицы, выходы элементов И матрицы являются выходами многоканального распределителя сигналов, выходы разрядов счетчика коммутации столбцов соединены с входами промежуточного дешифратора столбцов, выходы которого подключены к вторым входам элементов И соответствующих столбцов матрицы, за исключением элементов И последней строки матрицы, содержит также регистр коммутации строк регистр коррекции и дополнительную матрицу элементов И, причем входы разрядов регистра коммутации строк подключены к соответствующим выхода промежуточного дешифратора строк, а выходы разрядов регистра коммутации строк соединены с первыми 1 входами элементов И соответствуюгцих строк дополнительной матрицы элементов И, выходы которых являются дополнительными выходами многоканального распределителя сигналов, выходы промежуточного дешифратора столбцов соединены с-,, вторыми входами элементов И дополнительной матрицы за исключением элементов И последней строки дополнительной матрицы и с входами соответствующих разрядов регистра коррекции, выходы разрядов которого подключены к вторым входам соответствующих элементов И последних стро матрицы элементов И и дополнительной матрицы элементов И, тактовый вход регисгтра коммутации строк соединен с выходом генератора тактовых импульсов, вход счетчика коммутации столбцов и тактовый вход регист ра коррекции соединены с выходом предпоследнего разряда регистра ком мутации строк. Псэставленная цель достигается тем, Что многоканальный распределитель сигналов, содержащий счетчики коммутации.строк и столбцов, промежуточные дешифраторы строк и столбцов , матрицу элементов И и генера-. тор тактовых импульсов, выход которого подключен к входу счетчика ком мутации строк, выходы разрядов которого соединены с входами промежуточного дешифратора строк выходы которого соединены с первыми входаМи элементов И соответствующих строк матри1.ид1, выходы элементов И матрицьа являются выходами многоканального распределителя сигналов выходы разрядов счетчика коммутации столбцов соединены с входами промежуточного дешифратора столбцов выходы которого подключены к вторым входам элементов И соответствующих столбцов матрицы, за исключением элементов И последней ::троки матриц содержит также регистр коммутации строк, регистр коррекции, дополнительную матрицу элементов И и допол нительные дешифраторы строк и стол цов, причем входы разрядов регистр коммутации строк подключены к выхо дам разрядов счетчика коммутации строк, а выходы разрядов регистра коммутации строк соединены с входам дополнительного дешифратора строк, выходы которого соединеныс первыми входами элементов И соответствующих строк дополнительной матрицы элементов И, выходы которых являются дополнительными выходами многоканального распределителя сигналов, выходы промежуточного дешифратора столбцов соединены с вторыми входами элементов И дополнительной матрицы за исключением элементов И последней строки дополнительной матрицы, выходы разрядов счетчика коммутации столбцов соединены с входами соответствующих разрядов регистра коррекции, выходы разрядов которого подключены к входам дополнительного дешифратора столбцов, выходы которого, соединены с вторыми входами соответствующих элементов И последних строк матрицы элементов И и дополнительной матрн1щ элементов И, тактовый вход регистра коммутации строк соединен с выходом генератора тактовых импульсов, вход счетчика коммутации столбцов и .тактовый вход регистра коррекции соединены с предпоследним выходом дополнительного дешифратора строк. На фи-Го предста,влена функциональная схема одного варианта исполнения многоканального распределителя сигналов; на фиг. 2 - временные., диаграммы, на фиг.З - функциональная схема другого варианта исполнения многоканального распределител.ч сигналов. Распределитель (фиг.1 включает счетчики коммутации строк 1 и столбцов 2, регистр коммутации строк 3, регистр коррекции 4, генератор такто1 вых импульсов 5, промежуточные дешифраторы строк 6 и столбцов 7, матрицу элементов И 8 и дополнительную матрицу элементов И 9. Другой вариант распределителя )( фиг.З) содержит, кроме того, дополнительные дешифратор строк 10 и дешифратор столбцов 11. Распределитель работает следующим образом. По заднему фронту положительных тактовых импульсов типа меандр генератора 5 и положительных импульсов переноса с предпоследнего выхода регистра коммутации строк 3 соответственно меняют свое состояние выходы разрядов счетчиков коммутации строк 1 и столбцов 2, По переднему же фронту этих импульсов соответственно в регистр коммутации строк 3, имеющий разрядность 2, где И - разрядность счетчика 1-, и в регистр коррекции 4, имеющий разрядность 2, где ш -раз рядность счетчика 2, записывается ин.формация с выходов промежуточных дешиф1)аторов строк 6 и столбцов 7, .состояния которых к началу соответствующего импульса установились и меняются лишь после окончания импуль сов. Тогда информация в регистрах 3 и 4 повторяет -с эадержкой на длительность импульса соответствующей тактовой частоты информацию дешифрированных состояний соответственно счетчиков 1 и 2, и одновременно осуществляется жесткая синхронизация состояний соответствующих пар счетчик-регистр. Для любого состояния счетчика коммутации столбцов 2 и регистра коррекции 4 включенным окажется лишь один столбец основной 8 и дополнительной 9 матриц элементов И. Регистр коррекции 4 служит для устранения скола сигналов и импульсных помех на выходах последних строк соответственно основной 8, дополнительной 9 матриц элементов И в моме ты переключения столбцов. По мере поступления импульсов тактового гене ратора 5 на выходах промежуточного дешифратора строк 6 и регистра комму тации строк 3 вырабатывается циклически изменяющаяся последовательност импульсных сигналов. Эта последовательность, будучи логически умноженной на состояние выходов промежуточ|ного дешифратора столбцов 7 и счетчика коррекции 4, формирует на выходах основной 8 и дополнительной 9 матриц элементов И, являющихся соответственно нечетными и четными выходами (каналами) распределителя, серию циклически повторяющихся -перекрывающихся импульсных сигналов, длительность KOTOJ JX равна периоду следования тактовых импульсов генератора 5. Необходимости в дополнительной синхронизации счетчиков 1 и 2 и регистров 3 и 4 нет, так как диа грамма выходных сигналов может на-чаться с любого сигнала и далее синхронизируется автоматически сигналами генератора 5 и переноса. Временные диагратФ1ы (фиг.2 соответствуют распределителю на 32 канала, тогда разрядность счетчиков 1 и 2, синтези рованных для работы в циклическом коде, VI vrt 2, разрядность регистров 3 и 4 равна 4. На диаграмме показаны сигналы типа меандр задающего генератора тактовых импульсов, относительно которых синхронизирован все временные диаграммы распределите ля, состояние выходов промежуточного дешифратора строк б fДШб/1/...даб/4/ регистра коммутации строк 3 (РгЗ/1/. РгЗ/4/), промежуточного дешифратора столбцов 7 (ДШ7/1/...ДШ7/4/; и регистра коррекции 4 (Рг4/17...Рг4/4/ а также выходные перекрывающиеся сигналы распределителя S1...532 (один цикл).-, . В другом варианте распределителя Д фиг.3)дополнитель ные дешифраторы строк 10 и столбцов il подключены к выходам соответственно регистра коммутации строк 3 и регистра коррекции 4. В регистры коммутации строк 3 и коррекции 4 информация заносится соответственно с выходов счетчиков коммутации строк 1 и столбцов 2. При этом разрядности счетчика 1 и регистра 3, счетчика 2 и регистра 4 попарно совпадают. В остальном работа распределителей, представленных на фиг.1 и фиг.З, идентична. Таким образом, многоканальный распределитель сигналов, реализованный по представленной схеме повьлиает быстродействие за счет удвоения сигналов в цикле; является экономичным с точки зрения затрат оборудования { причем, при .разрядности счетчиков 1, и более экономичной являетс/j схема, представленная на фиг.З ; работает от сигналов типа меандр. Для реализации режима распределения импульсов необходимо простробировать элементы И матриц 8 и 9 импульсами генератора 5. Формула изобретения 1. Многоканальный распределитель сигналов, содержащий счетчики комму.тации строк и столбцов, промежуточные {дешифраторы строк и столбцов, мат|рицу элементов И и генератор тактовых импульсов, вых.од которого подключен к входу-счетчика коммутации строк выходы разрядов которого соединены с входами промежуточного дешифратора строк, выходы которого соединены с первыми входами элементов И соответствующих строк матрицы, выходы элементов И матрицы являются выходами многоканального распределителя сигналов, выходы разрядов счетчика коммута ции столбцов соединены с входами промежуточного дешифратора столбцов, выходы которого подключены к вторым входам элементов И соответствующих столбцов матрицы, за исключением элементов И последней строки матрицы, отличающий ся тем, что, с целью повышения быстродействия, он содержит регистр коммутации строк, регистр коррекции и дополнительную матрицу элементов И, причем входы разрядов регистр коммутагХ и строк подключены к соответств5ющим выходам промежуточного дешифратора строк, а выходы разрядов регистра коммутации строк соединешл с Т1ервы чи входаили элементов И соответствующих строк дополнительной матрицы элементов И, вгиоды которых являются дополнительными выходами многоканального распределителя сигналов, выходы промежутонного дешифратора столбцов соединены с вторьнии входами элементов И дополнительной матрицы, за исключением элементов И последней строки дополнительной матрицы, и с входами соответствующих разрядов регистра коррекции, выходы разрядов которого подключены к вторым входам соответст вующих элементов И последних строк . матрицы элементов И и дополнительной матрицы элементов И, тактовый вход регистра коммутации строк соединен с выходом генератора тактовых импуль сов, вход счетчика коммутации столбт цов и тактовый вход регистра коррекции соединены с выходом предпоследне го разряда регистра коммутации строк 2. Многоканальный распределитель сигналов, содержащий счетчики коммутации строк и столбцов, промежуточны дешифраторы строк и столбцов, матриц элементов И и генератор тактовых импульсов, выход которого подключен к входу счетчика коммутации строк, выходы разрядов которого соединены с входами промежуточного дешифратора строк, вь1ходы которого соединены с первыми входами элементов И соответствующих ст:рок матрицы, выходы элементов И матрицы являются выходами многоканального распределителя сигналов, выходы разрядов счетчика коммутации столбцов соединены с входами промежуточного дешифратора столбцов, выходы которого подключены к вторым входам элементов И соответствующих столбцов матрицы, за исключением элементов И последней строки матрицы, отличающийся тем, что, с целью повышения быстродействия, он содержит регистр коммутации строк, регистр коррекции, дополнительную матрицу элементов И и дополнительные дешифраторы строк и столбцов, причем входы разрядов регистра коммутации стррк подключены к выходам разрядов счетчика коммутации строк, а выходы разрядов регистра коммутации строк соединены с входами дополнительного дешифратора строк, выходы которого соединены с первыми входами элементов И соответствующих строк дополнительной матрицы элементов И, выходы которых являются дополнительными выходами многоканального распределителя сигналов, выходы промежуточного дешифратора столбцов соединены с вторыми входами элементов И дополнительной матрицы, за исключением элементов И последней строки дополнительной матрицы, выходил разрядов счетчика коммутации столбцов соединены с входами соответствующих разрядов регистра коррекции, выходы разрядов которого подключены к входам дополнительного дешифратора столбцов, выходы которого соединены с вторыми входами соответствующих элементов И последних строк матрицы элементов И и дополнительной матрицы элементов И, тактовый вход регистра коммутации строк соединен с выходом генератора тактовых импульсов, вход счетчика коммутации столбцов и тактовый вход регистра коррекции соединены с предпоследним выходом дополнительного дешифратора строк. Источники информадии, принятые во внимание при экспертизе 1.Авторское свидетельство СССР i № 402152, кл. Н 03 К 17/62, 1972. 2.Авторское свидетельство СССР № 455489; кл. Н 03 К 17/62, 1973. 3.Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств. М., .Советское радио, 1975, с.281, рис.6.15 (прототип1.

Авторы

Даты

1982-08-15—Публикация

1980-10-03—Подача