Известны электронные адресные автоматы для программного электропитания, содержащие адресные ключи, дешифраторы, генератор импульсов, регистры, коммутаторные усилители, схемы И и ИЛИ и устройство местного управления.

Предлагаемый автомат отличается тем, что содержит сравнивающее устройство, выход которого подключен ко входу регистра коллекторной группы, а входы - к выходам регистров коллекторной и эмиттерной групп и ко входам дешифр аторов коллекторной и эмиттерной групп, выходы которых через коммутаторные усилители подсоединены ко входам схем И адресных ключей и через разделительные диоды - к эмиттерам и коллекторам транзисторов соответствующих адресных ключей. Вторые входы схем И адресных ключей соединены через дешифраторы с выходами регистров номера нагрузки, а третьи входы схем И подсоединены к выходам распределителя, вход которого соединен с генератором импульсов. Один выход устройства местного управления подключен ко входу первого регистра номера нагрузки, выход переполнения которого соединен со входом второго регистра номера нагрузки, а выход переполнения второго регистра номера нагрузки подсоединен через схему ИЛИ и регистр коллекторной группы ко входу регистра эмиттерной группы. Второй выход

устройства местного управления подключен к сравнивающему устройству, а третий выход устройства местного управления подсоедине; через триггер к управляющим входал дешифраторов номера нагрузки.

Такое выполнение устройства позволяет сократить оборудование и улучшить эксплуатационные характеристики устройства.

iB основу построения автомата этого класса лежит программное построение (воспроизведение) трехфазных мостовых схем типа схемы Ларионова с применением электронного адресного Ключа и двухпарной (четырехмерной) дешифрации по три ключа, принадлежащие к разным строкам матрицы.

Адресным ключом называют электронный ключ с несколькими входными схемами совпадения с последующей сборкой с усилением и не имеющий фиксированного источника питания, работающий в двух чередующихся режимах: для тиристоров - в с анодной нагрузкой и в режиме с катодной нагрузкой, для транзисторов - в режиме с коллекторной нагрузкой и в режиме с эмиттерной нагрузкой.

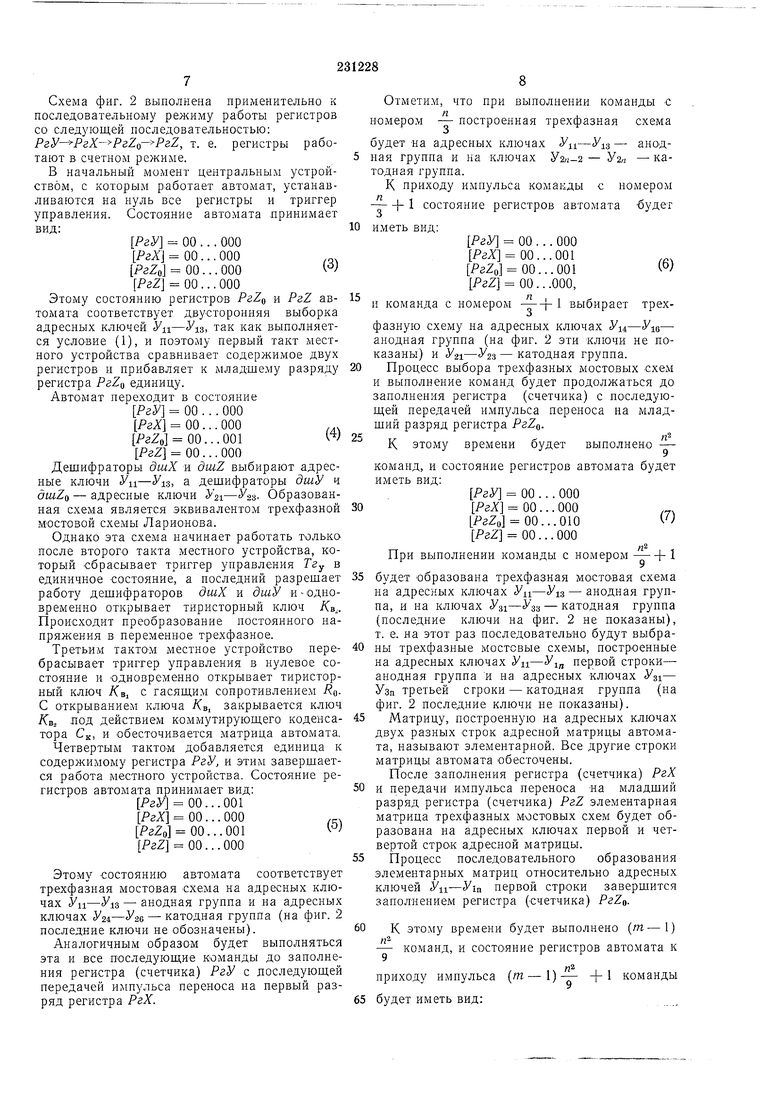

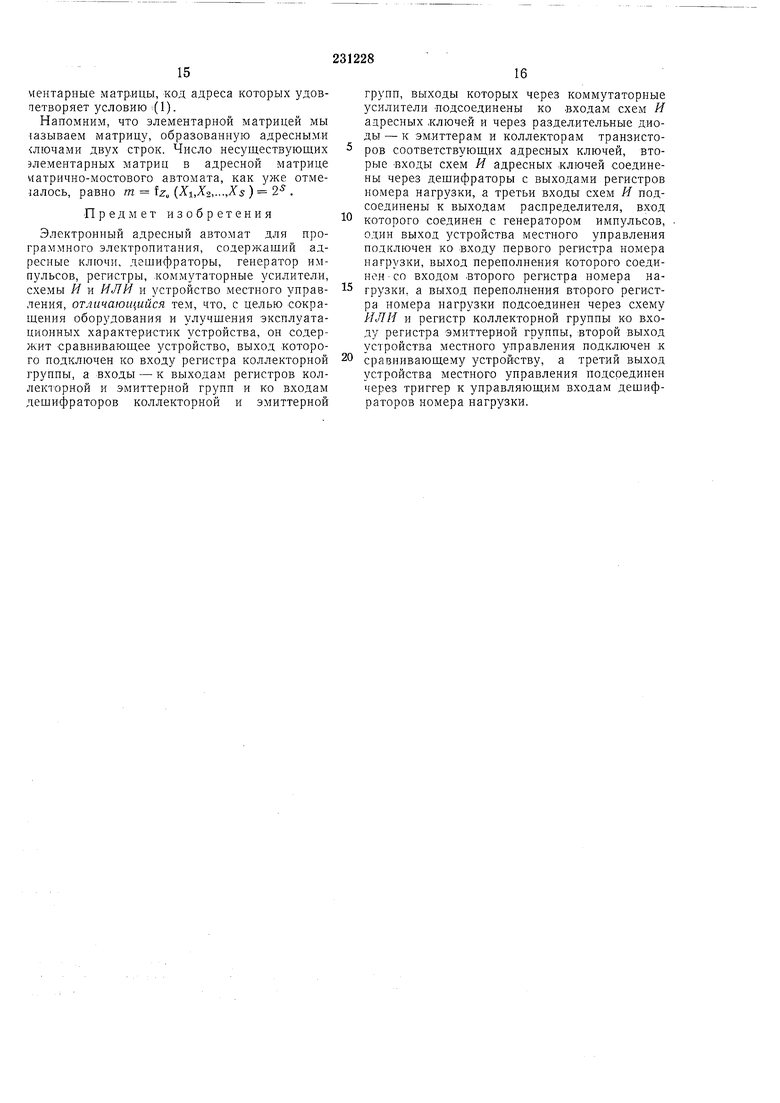

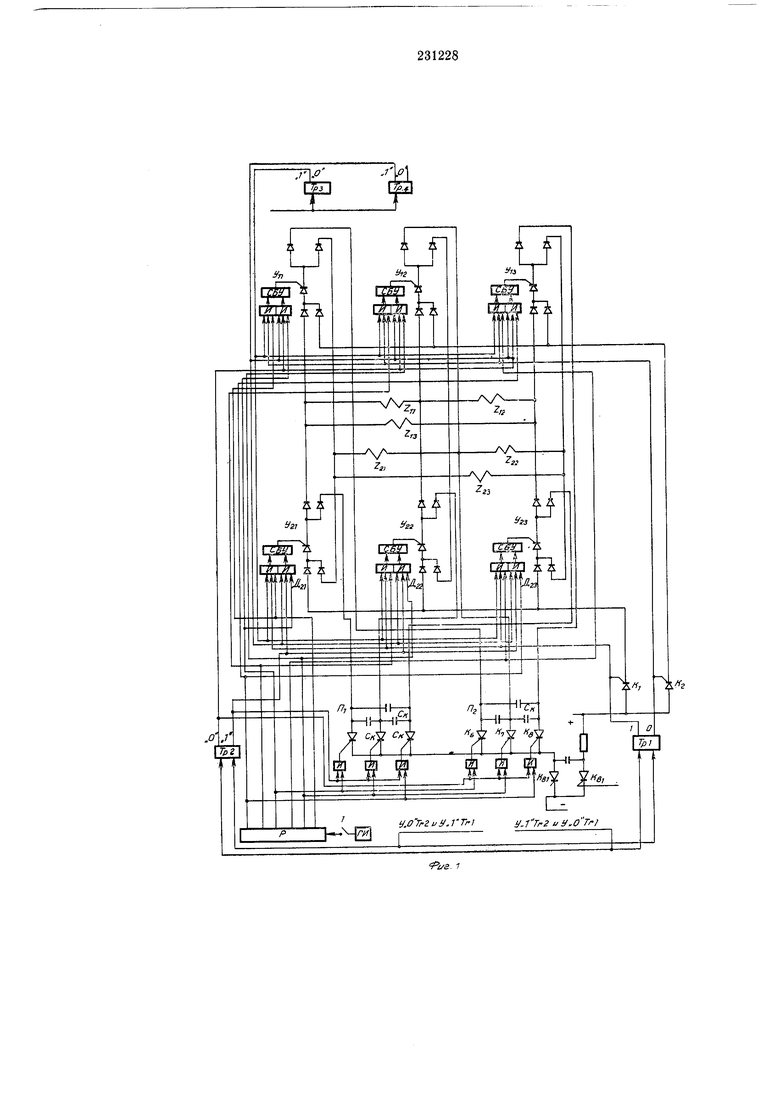

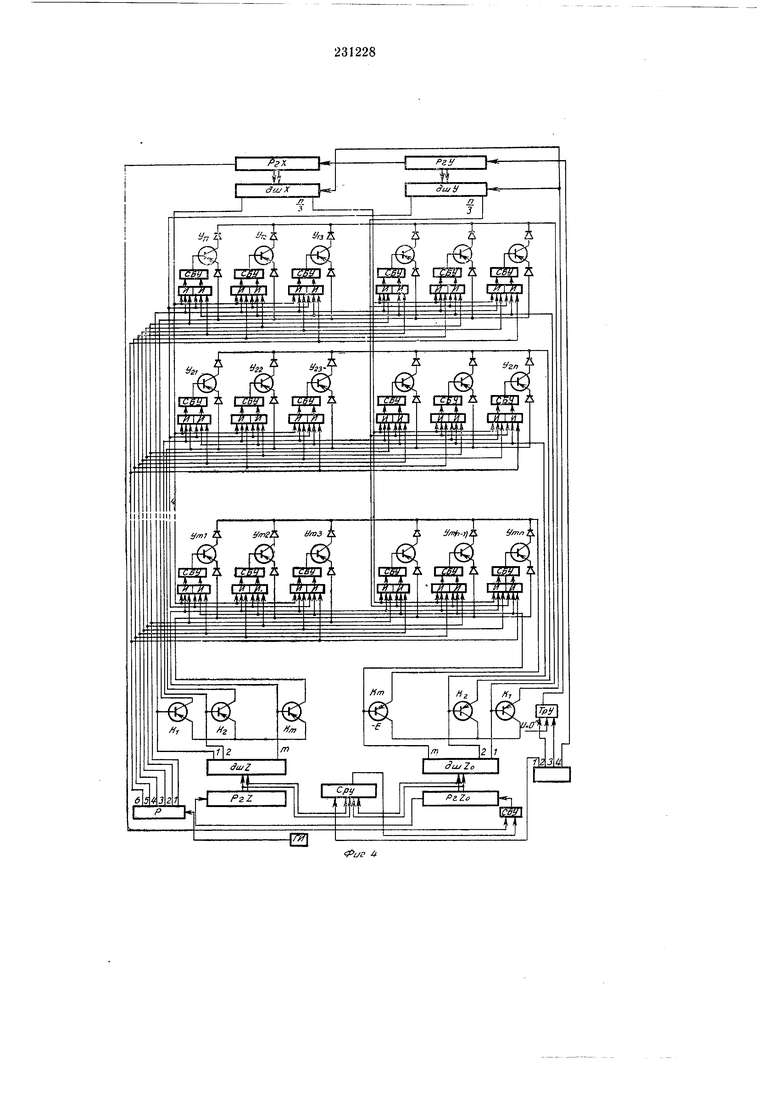

К катоду (коллектору) адресного ключа присоединяется набор диодов со стороны своих анодов, а к аноду (эмиттеру) - набор диодов со стороны своих катодов. чесгвом адресных шин матрицы трехфазного автомата. Часть этих диодов служит для программного электропитания электродо-в активного элемента адресного ключа, другая часть - для исключения взаимного шунтирования выходных нагрузочных шин автомата. На фиг. 1 представлена пояснительная схема программного построения трехфазных схем, каждая из которых является эквивалентом трехфазной мостовой схемы Ларионова; 10 на фиг. 2 - схема электронного адресного автомата матрично-мостового типа; на фиг. 3- схема матрицы трехфазного автомата; на фиг. 4 - схема управления и матрица автомата (транзисторный вариант); на фиг. 5 - схе- 15 ма, поясняющая принцип комбинированного построения мостовых схем; на фиг. 6 - схема соединения нагрузок для комбинированно-мостового автомата; на фиг. 7 - основная схема адресного автомата комбинированно-мостово- 20 го типа. Тиристоры называются коммутирующими ключами Ki и Kz анодной группы или эмиттерной группы для транзисторного варианта. Катодные секции П и П с коммутирующими 25 конденсаторами мостовой схемы Ларионова предназначены для осуществления трехфазной коммутации адресных ключей матрицы. Рассмотрим работу схемы фиг. 1. Пусть в определенный момент триггеры зо имеют следующие состояния: триггер Tpi - единичное, триггер Тр2 - нулевое, триггер Трз - единичное, триггер Тр -единичное. В таком состоянии аноды адресных ключей будут, подключены к положительному 35 полюсу источника питания через коммутирующий ключ Ki и соответствующие диоды Д21 - Дзз, а катоды каждого из адресных ключей через соответствующие диоды и тиристорные ключи катодной секции Я2 схемы 40 Ларионова - к отрицательному полюсу источника питания. (В действительности сказанное будет иметь место при наличии управляющих импульсов на выходных шинах распределителя, а пока что эти импульсы отсутствуют). 45 ОдновременнОе совпадение управляющих сигналов будет на обоих входах логических схем И адресных ключей , так как один из входов этих элементов управляется нулевым выходом триггера Тр, а другой - единичным 50 выходОМ триггера Тр. Аналогично, . одно-временное совпадение управляющих сигналов будет для логических схем И адресных ключей У21-Уаз- При включении тумблера Т генератора импульсов ГИ 55 тактовые импульсы Р поступят на входы адресных ключей со следующей последовательностью:1- на вход ключа У21 через схему И 60 2- на вход ключа У12 через схему Я 3- на вход ключа Узз через схему Я 5 Одновременно с открыванием адресных ключей 12, УП и 13 синхронно с каждым от тех же тактов распределителя открываются тиристоры катодной секции П схемы Ларионова, и тем самым первичные обмотки Z, Zi2 и трехфазного трансформатора оказываются под трехфазным напряжением (вторичные обмотки трансформаторов на чертеже не показаны). Процесс последовательного переключения первичных обмотОК трансформатора происходит под воздействием импульсов распределителя и коммутирующих конденсаторов катодной секции Я2 схемы Ларионова. Построенный трехфазный инвертор (преобразователь) на адресных ключах отличается от трехфазного автономного инвертора внесением в цепь нагрузки дополнительного сопротивления за счет коммутирующих ключей Кз-Кп секции //2-П, а также за счет последОВательных диодов адресных ключей и выключающего тиристорного ключа /Св,. При переключении триггеров Гр и Тр.2 к положительному полюсу источника питания будут подключены аноды адресных ключей через коммутирующий ключ К, а катоды адресных ключей У-21-У з будут подключены к отрицательному полюсу источника питания через катодную секцию П схемы Ларионова. Совпадение управляющих сигналов будет для входных логических схем И адресных ключей УН-У±з (аналогично для адресных ключей совпадение будет для логических схем Я. Последовательность поступления тактовых импульсов распределителя на входы адресных усилителей следующая: 1- на вход ключа УН через схему И 2- на вход ключа У22 через схему И 3- на вход ключа УХЗ через схему И 4- на вход ключа У21 через схему И 5- на вход ключа У12 через схему И 6- на вход ключа У2з через схему И Мы видим, что произошла перестройка, т. е. роли адресных ключей УН-Уаз и У21-Уаз поменялись местами, и на этот раз под трехфазным напряжением находится трансформатор с первичными обмотками , и Z. Процесс непрерывного переключения обмоток второго трансформатора к источнику трехфазного напряжения осуществляется непрерывной работой генератора импульсов ГИ с распределителем и катодной секции П схемы }1арио«ова. Рассмотренная на фиг. 1 схема в своем составе имеет две трехфазные мостовые схемы на адресных ключах, каждая из которых является эквивалентом, модификацией трехфазной мостовой схемы Ларионова. матрица, состоит из /п-строк и п-столбцов с общим числом N - m-n электронных (тиристорных) адресных ключей, при том так, что каждая тройка адресных ключей i-строки путем нрограммной коммутации источника питания и двухпарной (четырехмерной) дешифрации со стороны их входов образует с каждой тройкой адресных ключей всех других m - 1 строк трехфазных мостовых схем, 3 каждая из которых является эквивалентом трехфазной мостовой схемы Ларионова. Для всей адресной матрицы автомата число всех трехфазных мостовых схем определяется выражением г./14 1 N(N-1) (т - ) - тп (тп - п) - - . Схема матрицы трехфазного автомата (см. фиг. 3), выполненная на транзисторных адресных ключах, состоит из двух строк и шести столбцов с обш,им числом (m-l) 2(2-l)-| 8 эквивалентных трехфазных схем. Управляющие схемы фиг. 3 не показаны. Коммутаторами коллекторной группы источника питания являются транзисторные ключи 12-Ki5. Эмиттерная группа коммутаторов в этой схеме представлена ключами Ки и Ki. Первая цифра в обмотках Z соответствующих трехфазных трансформаторов указывает номер трансформатора, вторая -номер обмотки. Любая тройка адресных ключей данной строки образует с каждой тройкой другой строки трехфазную мостовую схему. Например, тройка адресных ключей zi-У-2з образует трехфазную схему с тройкой адресных ключей с выходным трехфазным трансформатором 51-53. Та же тройка образует аналогичную схему с тройкой ключей с трехфазным трансформатором 61-63. Число строк -т и столбцов -п матрицы электронного адресного автомата определяется необходимым количеством выходных шин. Оборудование для управления матрицей автомата будет наименьшим при ее квадратной геометрии (от 3п). Управление матрицей автомата (см. фиг. 2) осуществляется двухпарной (четырехмерной) дешифрацией, и при этом каждый из двух дешифраторов duiZo и duiZ имеет двойное назначение. Каждая выходная шина дешифратора duiZ с номером t управляет входом г-го тиристорного Ключа коммутатора анодной группы /Ci- Km И ОДНИМ ИЗ ВХОДОВ логичбской схемы и всех адресных ключей той же г-строки. Аналогично, каждая выходная шина дешифратора dtuZo с номером i управляет входными цепями одной катодной секции Я схемы Ларионова (катодная группа коммутатора) и одним из входов логической схемы И всех адресных ключей той же строки. Два других дешифратора дшХ и дшУ являются перпендикулярами соответственно дешифраторов duiZ и dmZ(t. Каждая выходная шина дешифратора дшХ одновременно управляет одним из входов логической схемы И адресных ключей трех столбцов и совместно с соответствующим выходом дешифратора duiZ определяет номер тройки, т. е. трех адресных ключей из той строки матрицы автомата, Которая при данном коде адреса выходного трансформатора образует анодную группу в эквивалентной трехфазной схеме. Аналогично, каждая выходная шина дешифратора дшУ совместно с соответствующим выходом дешифратора dtuZo определяет номер трех адресных ключей из другой строки матрицы, которые лри данном коде образуют катодную группу в эквивалентной трехфазной схеме. Для этой цели каждая выходная шина дешифратора дшУ также одновременно управляет одним их входов логической схемы И адресных ключей трех столбцов матрицы. Выходные трехфазные трансформаторы (адресные нагрузки) и относящиеся к ним диоды на схеме фиг. 2 не показаны. Код адреса нагрузочного трансформатора (позиции) принимается в регистры дешифраторов РгХ, РгУ, PeZo, PaZ. Разрядность регистров PeZ и PsZfl одна и та же (то же самое для регистров РгХ и РгУ). Число выходных шин для дешифраторов дшХ и дшУ равно п для матрицы с п-столбцов. Сравнивающее устройство Сру производит формирование алгоритма работы автомата, т. е. обеспечивает выбор адресных ключей, принадлежащих только к разным строкам матрицы автомата. При работе -автомата местное устройство производит сравнение содержимого двух регистров PeZ и PгZ(, и если поразрядная сумма по mod2 равна нулю, то происходит добавление единицы к младшему разряду младшего регистра. Это условие записывается в виде: PsZo Xi, Xz ..., Х .-.,.v Ргг Х„ X, ..., Х, ©(1) о о ... о где 5o - разрядность регистров PsZj и PгZ, как отмечалось, одна и та же. Выходные шины распределителя (расщепителя фаз) к входам адресных ключей матрицы подведены с учетОМ обеспечения образования трехфазного напряжения. Местное устройство МУ предназначено для управления работой автомата и состоит из релаксационных ждущих схем, триггера управления Тгу и схемы выключения (прерывателя). Все дешифраторы являются типа «диодная матрица с выходными усилителями необходимой мощности. Каждый дешифратор такого типа реализует функцию алгебры логики в виде:

Схема фиг. 2 выполнена применительно к последовательнОМу режиму работы регистров со следующей последовательностью: РгУ- Рг - Рг7о- PsZ, т. е. регистры работают в счетном режиме.

В начальный момент центральным устройством, с которым работает автомат, устанавливаются на нуль все регистры и триггер управления. Состояние автомата принимает вид:

РгУ 00 ... 000

РгХ 00... 000,„.

PsZo 00... 000W

PeZ 00 ... 000

Этому состоянию регистров PaZo и PeZ автомата соответствует двусторонняя выборка адресных ключей , так как выполняется условие (1), и поэтому первый такт местного устройства сравнивает содержимое двух регистров и прибавляет к младшему разряду регистра PsZo единицу. Автомат переходит в состояние

РгУ 00 ... 000

РгХ 00... 000,.,

P2Zo 00...001W

PsZ 00... 000

Дешифраторы дшХ и diuZ выбирают адресные ключи УН-УГЗ а дешифраторы дшУ ч doiZo - адресные ключи . Образованная схема является эквивалентом трехфазной Мостовой схемы Ларионова.

Однако эта схема начинает работать только после второго такта местного устройства, который сбрасывает триггер управления Tsy в единичное состояние, а последний разрешает работу дешифраторов дшХ и дшУ и-одновременно открывает тиристорный ключ Кв,. Происходит преобразование постоянного папряжения в переменное трехфазное.

Третьим тактОМ местное устройство перебрасывает триггер управления в нулевое состояние и одновременно открывает тиристорный ключ Хв, с гасящим сопротивлением оС открыванием ключа Яв, закрывается ключ KB, ПОД действием коммутирующего коденсатора CK, и обесточивается матрица автомата. Четвертым тактом добавляется единица к содержимому регистра РгУ, и этим завершается работа местного устройства. Состояние регистров автомата принимает вид:

РгУ 00... 001

РгХ 00... 000...

P2Zo 00...001

PaZ 00... 000

Этому состоянию автомата соответствует трехфазная мостовая схема на адресных ключах УН-У13 - анодная группа и на адресных ключах У24-Узб - катодная группа (на фиг. 2 последние ключи не обозначены).

Аналогичным образом будет выполняться эта и все последующие команды до заполнения регистра (счетчика) РгУ с доследующей передачей ил пульса переноса на нервый разряд регистра РгХ.

Отметим, что при выполнении команды с номером - построенная трехфазная схема

будет на адресных ключах - анодная группа и на ключах - У2п - катодная группа.

К приходу импульса команды с номером

I 1

-- 1 состояние регистров автомата оудет

иметь вид:

РгУ 00 ... 000 РгХ 00... 001

(6) P3Zo 00...001 PsZ 00 .. .000,

и команда с номером 1 выбирает трехфазную схему на адресных ключах анодная группа (на фиг. 2 эти ключи не показаны) и - катодная группа. Процесс выбора трехфазных мостовых схем и выполнение команд будет продолжаться до заполнения регистра (счетчика) с носледующей передачей импульса переноса на младший разряд регистра PsZo.

К этому времени будет выполнено -

команд, и состояние регистров автомата будет иметь вид:

РгУ 00 ... 000

РгХ 00... 000,„,

PгZo 00...010()

PeZ 00 ... 000

п

При выполнении команды с номером -1

будет образована трехфазная мостовая схема па адресных ключах УН-У - анодная группа, и на ключах Уз1-Узз - катодная группа (последние ключи на фиг. 2 не показаны), т. е. на этот раз последовательно будут выбраны трехфазные мостовые схемы, построенные на адресных ключах УН-У первой строки- анодная группа и на адресных ключах Уз1- Узп третьей сгроки - катодная группа (на фиг. 2 последние ключи не показаиы).

Матрицу, построенную на адресных ключах двух разных строк адресной матрицы автомата, называют элементарной. Все другие строки матрицы автомата обесточены. После заполнения регистра (счетчика) РгХ

и передачи импульса переноса на младший разряд регистра (счетчика) PгZ элементарная матрица трехфазных мостовых схем будет образована на адресных ключах первой и четвертой строк адресной матрицы.

Процесс последовательного образования элементарных матриц относительно адресных ключей УН-Угп первой строки завершится заполнением регистра (счетчика) PeZo.

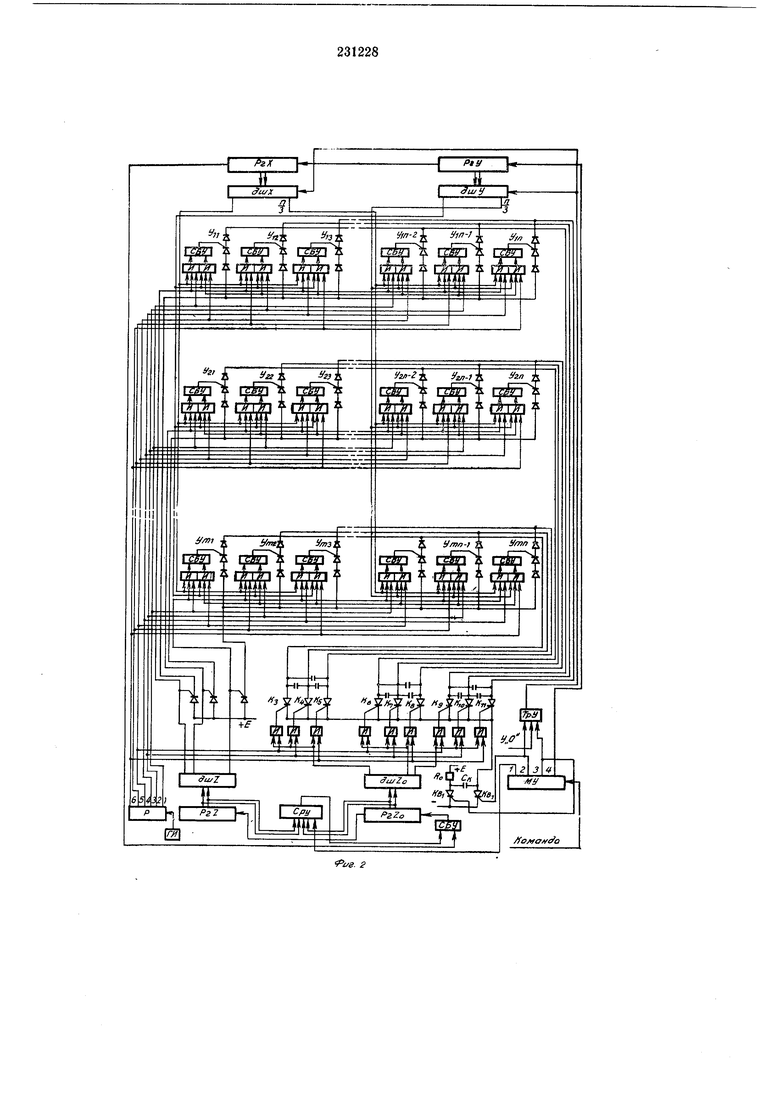

К этому времени будет выполнено (tn-1) РгУ 00 ... 000 РгХ 00... 000 PeZo 00... 000 PsZ 00.. .000, и поэтому дешифраторы дшХ -к duiZ выбирают адресные ключи - анодная группа, а дешифраторы дшУ и (5ш2о- адресные ключи - катодная группа мостовой схемы Ларионова. Таким образом роли адресных ключей УН- УГЛ и по сравнению с состоянием (4) автомата поменялись местами, т. е. произошло «реверсирование и в дальнейшем аналогичным образом будет образована т-1 элементарных матриц относительно адресных ключей второй строки адресной матрицы. Однако при выполнении команды с номе, ,, «2 «2 m «2 , , ром (т-1)1Ь 1 г состояние регистров автомата уже будет иметь вид: РгУ 00 ... 000 РгХ 00... 000,„. PaZo OO...OOI( P2Z 00...001, что приводит к Выполнению условия (1), И поэтому местное устройство (МУ) своим первым тактОМ добавляет единицу к содержимому регистра PzZ и исключает одновременность двусторонней выборки адресных ключей второй строки матрицы автомата, т. е. делается искусственный переход. С заполнением регистра /sZ и передачей импульса переноса на младший разряд регистра PaZ завершается последовательность вы/1 И2полнения еще (т - 1)- команд. После повторного заполнения регистра sZ,, и передачи импульса переноса на первый разряд регистра PeZ состояние регистров автомата будет иметь вид: РгУ 00 ... 000 РгЛ 00 ... 000.,,,. PaZn 00 ... 000() PeZ 00... 010, и дешифраторы дшХ и дш2 выбирают адресные ключи У.Ч1-У:)з - анодная группа и ключи У,,-У1Я - катодная группа и т. д. При выполнении команды с номером + 2(m-l)- + состояние регистров будет иметь вид: РгУ 00 ... 000 РгХ 00 ... 000 P2Zo 00...010 iP2Z 00...010, и снова будет сделан искусственный переход. Во всех случаях при выполнении команд, номера которых описываются формулой - +1, где а 1, 2, 3. т, происходит Это обстоятельство приводит к тому, что писанный автомат отрабатывает функцию вида: 0)) lfz(Xi, Х ,.. ., Xsi)fz,(Xi, Х , ..., s,(Xi,Xs, ..,,Xs,}fy(Xi,Xz, ...,Xs,) - - fz,(Xi,X,... ,Xs,)fx{Xi,X2,.. .,Xs,)fy (X,,X,,...,Xs.}, де Г-код адреса элементарной матрицы, I - код адреса трехфазной мостовой схемы, принадлежащей к данной элементарной матрице, III - код адреса несуществующих трехфазных мостовых схем адресной матрицы автомата. Запись в виде И не верна и требует формального преобразования. Учитывая условие (2), имеем 2 2 (2 - 1), и так как 5i 52 5о, а 5з Si 5,TO 2S«22S(2So-l). С другой стороны, /X (1 .2 ,} и fy (JfTjAa,... Дз,) обеспечивает- выхода и совместно образуют - выходных трехфазных мостовых шин,учитывая также, 4Tofz(if-,Xsi) и fzo (1 ,..., Xs,) обеспечивают выходных шин, окончательно имеем ф (/п-1) (-) Рдля случая т Вп ,1 Л(Л -Зл) Схема (см. фиг. 4) управления и матрица автомата (транзисторный вариант) состоит из тех же основных устройств с той лишь разницей, что в этой схеме нет схем искусственной коммутации с конденсаторами. Приборы являются управляемыми, и поэтому отпадает необходимость в таких схемах. Коммутаторами источника питания коллекторной группы являются транзисторные усилители (ключи) /Ci - К, управляемые дешифратором dtuZfj. Аналогично, комм}таторами источника питания эмиттериой группы являются транзисторные ключи /Ci - /См, управляемые дешифратором dtuZ. Процесс последовательного выполнения команд и переходов при выполнении условия (1) выполняется так же, как это делалось для тиристорного варианта. Пусть состояния регистров следующие: РгУ 00... 001 Рг 00 ... 000,.„. P2Zo 00...001( 00 .. .000, дешифратор du-i.Z открывает транзисторный ключ и подключает к положительному полюсу источника питания эмиттеры адресных ключей Уи-У1п и совместно с дешифратором дшХ выбирает тройку адресных ключей Уц-У, т. е. совпадение управляющих сигналов будет иметь место для логических схем И ключей УН-Уц матрицы.

11

полюсу источника питания будут подключены коллекторы адресных ключей второй строки матрицы, и также совместно с дешифратором дшУ .выбирает адресные ключи У24- У2в (не показаны).

В данном случае совпадение будет иметь место для логических схем И элементов.

Под трехфазным напряжением будет трансформатор с первичными обмотками 61-63 на фиг. 3.

При изменении адреса нагрузки, например, для состояния автомата:

РгУ 00 ... 000 РгХ 00 ... 000,. 04

PaZn 00... 000

fP2Z 00...001

под трехфазным напряжением окажется трансформатор с первичными обмотками 11-13 и т. д.

Изменение входного сопротивления адресных ключей при переходе с одного режима на другой компенсируется варьированием параметров управляющих сигналов для одной из логических входных схем Я.

Удельный расход диодов для автомата с трехфазным выходом равен шести без учета оборудования для управления.

Выбор типа усилителей для цепей управления, длительность паузы между тактами местного устройства, организации последовательности или параллельности работы регистров и все другие конкретные вопросы разрешаются разработчиком в соответствии со своим собственным требованием, и при этом во всех случаях необходимо организовать местное устройство так, чтобы первым тактом формировалась алгоритма работы по формуле (И).

Частным вариантом рассмотренного автомата является комбинированно-мостовой матричный автомат, который в некоторых случаях окажется более экономичным по сравнению с матрично-мостОВым автоматом.

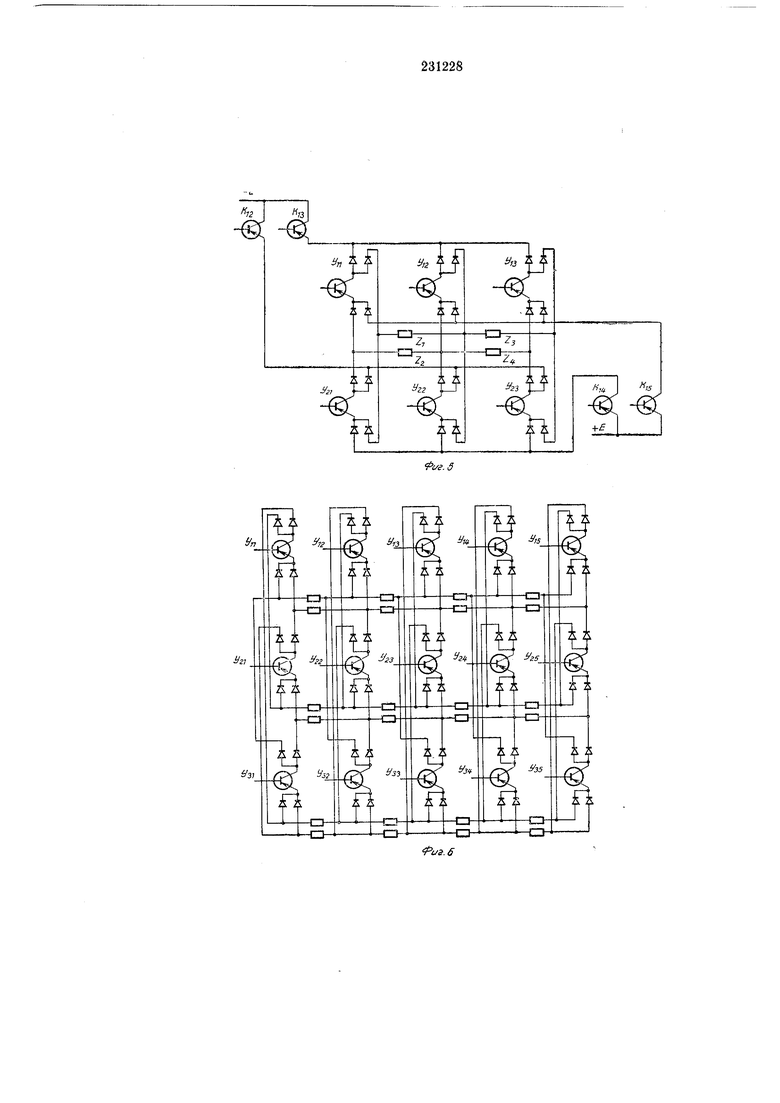

Схема (см. фиг. 5) поясняет принцип комбинированного построения мостовых схем. Пусть в рассматриваемый момент открыты коммутирующие ключи Ки и К, и следовательно, к отрицательному полЮСу источника подключены коллекторы адресных ключей . а к положительному полюсу - эмиттеры адресных ключей УЧ -Угз- В результате открывания адресных ключей Уо и УХЗ под током будет нагрузка Zg, направление тока слева направо. Вторым полупериодом открываются адресные ключи У12 и Уц, и ток нагрузки Za изменяет свое направление, т. е. создается мостовая схема с однофазным выходом. Для образования второй мостовой схемы открываем адресные ключи У и УХЗ, пропуская ток через нагрузку Z4, вторым полупериодом - ключи Уаз и У12, и ГОК изменяет свое направление. Адресные ключи У и Уаз являются общими для двухмостовых схем, т. е. комбинированными. В схеме (см. фиг. 6) удельный расход диодов, лримерно, равен двум, что достигается неполным использова12

нием логической возможности электронных адресных ключей.

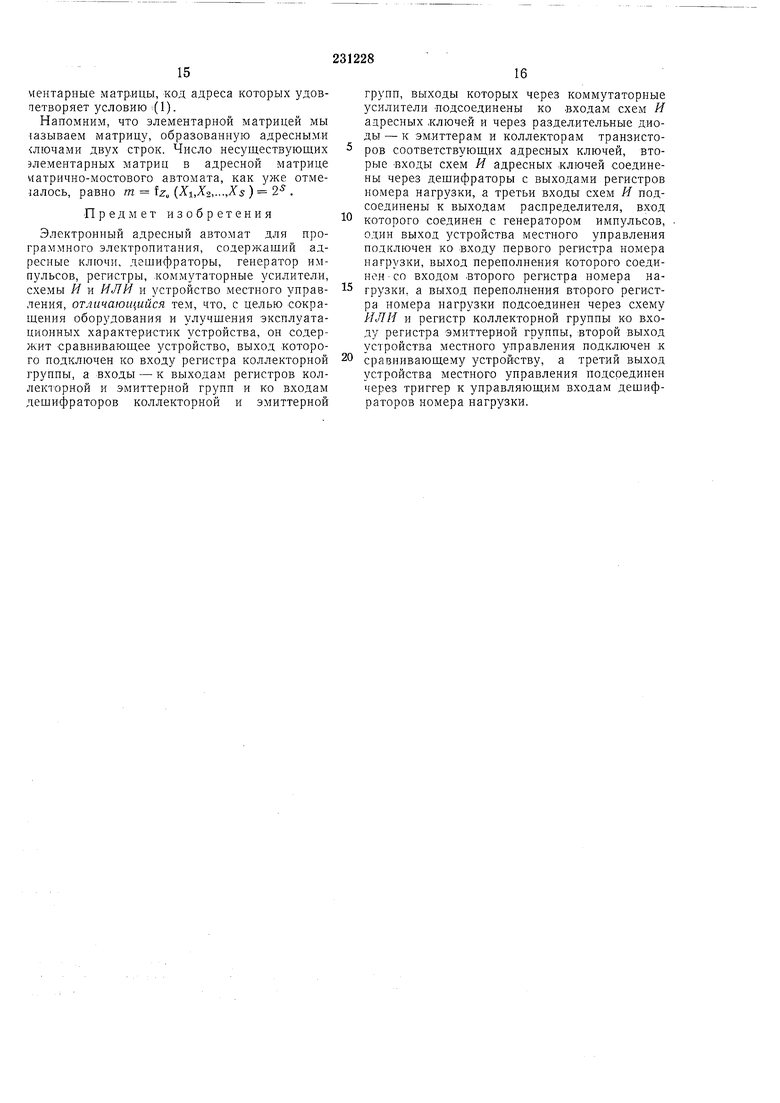

Адресная матрица автомата с т-строк и ft+l столбцов с общим Я mf/t-j-1) числом электронных адресных ключей обеспечивает Р т(т - 1) rt; :iOT№ выходных шин. Для схемы на фиг. 6 Р т(т)п 6-4 24 и количество диодов определяется выражением Д 2Р + 2т(т-1)т(от-1)/г +

Н-2т(т-1) отСт--1) (т -2) без учета оборудования управления, которое для этого варианта автомата значительно больше по сравнению с автоматом матрично-мостового Типа, однако прикидочный анализ показывает,

что этот вариант автомата во многих случаях экономичнее матрично-мостового варианта.

Основная схема адресного автомата комбинированно-мостового типа (см. фиг. 7) состоит из адресной матрицы и схемы трехмерного

управления с .повторением. Адресная -матрица состоит из т-строк и n+l столбцов с общим числом N т() электронных адресных ключей, при том так, что «аждый адресный ключ Уij с адресным ключом У1( + 1)

последующего номера той же строки составляет пару адресных ключей, каждая из которых образует одно-фазную мостовую схему со всеми парами адресных ключей тех же номеров всех других т - 1-строк адресной матрицы автомата.

Управление матрицей автомата осуществляется трехмерным способом с повторным образованием комбинационной части матрицы. Основная часть адресной матрицы состоит из

столбцов с первого до предпоследнего номера, а комбинационная часть - со второго до последнего, т. е. здесь рассматривается как две матрицы с одинаковым числом п-столбцов и т-строк, вставленных друг в друга. В состав

схемы управления входят регистры кода адреса элементарных матриц с дешифратором, коммутирующие ключи источника питания, сравнивающее устройство, местное устройство с триггером управления - все эти устройства

являются постоянными для адресных матриц. Для определения номера нагрузки и ее подключения к источнику питания служит один регистр РгУ с двумя выходными дешифраторами дшУ и дшУ. Один из дешифраторов

дшУ-i служит для определения номера нагрузки основной части матрицы, а другой дешифратор дшУ-2, - для определения номера нагрузки комбинационной части матрицы. Очередность работы дешифраторов дшУ

и дшУ определяется триггером Тг комбинации, так что, если работает дешифратор дшУ, то на выходных шинах дешифратора дшУ отсутствуют управляющие напряжений. Адресные ключи в схеме матрицы имеют по четыре

входных логических схем Я с иоследующей сборкой с усилением Сбу. Каждая выходная шина дещифратора дшУ управляет одновременно по одним входам схем совпадения И двух столбцов основной части матрицы. Ана13

дшУ2 управляет одновременно по одним входам схем Я комбинационной части матрицы. Адресные ключи первого и последнего столбцов имеют по два входных логических элемента.

Работа авто-мата организована в последовательном режиме со следующей последовательностью P3y- PeZo- PeZ. В качестве генератора управляющих импульсов используется третий и четвертый такты местного устройства.

Рассмотрим работу комбинированно-мостового автомата.

Как и во всех других случаях, первоначально устанавливаются на нуль все регистры и триггер управления, одновременно на нуль устанавливается триггер комбинации, подготавливая работу центральной системы с основной частью матрицы.

Для матрицы автомата не имеется элементарной .матрицы с первым (нулевым) номером, и поэтому первый такт местного устройства добавляет единицу к содержимому регистра -PsZo и состояние автомата принимает вид:

РгУ 00 ... 000 Рг2о 00...001(14)

PaZ 00... 000

В соответствии с этим дещифратор diuZ подключает к положительному полюсу источника эмиттеры ключей первой строки, а дещифратор diuZf, - к отрицательному полюсу источника питания коллекторы ключей второй строки матрицы. Дещифратор дшУ управляет одновременно входами логических схем И и поэтому с дешифратором dmZ выбирают ключи УП и У12 по входу схем И, а с дешифратором duiZft - ключи Уа и УЗ по входу схем Я.

Второй такт местного устройства устанавливает в единичное состояние триггеры управления и разрешает ра-боту дещифратора дшУ-, который нулевой код регистра РгУ преобразует в управляющее напряжение на своем первом (нулевом) выходе для окончательного выбора указанных четырех ключей.

Третий такт местного устройства открывает адресные ключи Уц и , и ток потечет через нагрузку Zi (см. фиг. 5 или фиг. 6). Четвертый такт местного устройства открывает адресные ключи У12 и У21, и в результате направление тока через нагрузку Z изменяется на противоположное. Пятый такт перебрасывает триггер управления в нулевое состояние и добавляет единицу к содержимому регистра РгУ.

Наличие триггера управления во всех вариантах адресных автоматов продиктовано обеспечением безаварийного режима работы, который может иметь место при выполнении условий (1), хотя для многих практических задач, .как, например ферритовые запоминающие устройства, аварийного режима не будет происходить, так как для этих устройств в цеиь источника тока вводится токостабилизи14

рующее сопротивление с достаточной величиной.

Роль триггера управления - задержать преобразование кода в лправляющее напрял ение дешифраторами дшУ- и 5шУо до тех пор, пока местным устройством не будет проверена выполнимость условия (1).

Процесс последовательного выбора адресных нагрузок для этого варианта автомата происходит аналогичным образом.

Пусть имеем следующее состояние автомата:

РгУ 111...Ill Яг2„1 011 ...111(15)

P2Z 111 ...111

Дешифратор diuZ выбирает коммутирующий ключ Km 1 через который к положительному полюсу источника питания подключает эмиттепы адресных ключей Ут1 - Ут(л4-1). Дешифратор diuZn выбирает коммутирующий ключ с номером /Cm и подключает к отрицательному полюсу источника питания коллекторы адресных ключей-строки Уjn -

-VДешифратор 5шУ,с дешифратором dmZ выбирает ключи Ут(л+1) и У,щп , а с дешифратором dluZo - ключи Ут . И Ут

- (п-1)- п

22

Первый полупериод тока нагрузки создается через соответствующую нагрузку открыванием ключей Ут(п-) и Ут , 3. второй полупериод через ту же нагрузку - открыванием ключей Ут,п. и Ут , И Т. Д.

-1

2

После заполнения регистров (счетчиков), т. е. когда состояние автомата примет вид: РгУ 111 ... 111 PeZnl 111...111(16)

PeZ 111... Ill,

очередная команда своим первым тактом устанавливает на нуль регистры PaZn и PeZ, а импульс переноса перебрасывает триггер Тгк в единичное состояние.

Для тиристорного варианта автомата при изменении кода адреса выходной шины возникает необходимость полного обесточивания адресной матрицы автомата и для этого служит тиристорный ключ KB, , который образует с тиристорным ключем /Св инверторную (прерывательную) схему.

Последовательное с ключом /Св, -сопротивление R является гасящим. Управление базовыми электродами тиристорных прерывательных схем осуществляется дешифратором duiZn и соответствующим выходом генератора импульсов ГЯ через логические И. vteHiapHbie матрицы, код адреса которых удовпетворяет условию i(l). Напомним, что элементарной матрицей мы 1азываем матрицу, образованную адресными лючами двух строк. Число несуществующих элементарных матриц в адресной матрице viaTpH4HO-MOCTOBoro автомата, как уже отмеlanocb, равно m fz (X-i,X2,...,Xs ) - 2 . Предмет изобретения Электронный адресный автомат для программного электропитания, содержащий адресные ключи, дешифраторы, генератор импульсов, регистры, коммутаторные усилители, схемы И и ИЛИ и устройство местного управления, отличающийся тем, что, с целью сокращения оборудования и улучщения эксплуатационных характеристик устройства, он содержит сравнивающее устройство, выход которого подключен ко входу регистра коллекторной группы, а входы - к выходам регистров коллекторной и эмиттерной групп и ко входам дешифраторов коллекторной и эмиттерной групп, выходы которых через коммутаторные усилители -подсоединены ко входам схем И адресных .ключей и через разделительные диоды - к эм.иттерам и коллекторам транзисторов соответствующих адресных ключей, вторые ВХОДЫ схем И адресных ключей соединены через дешифраторы с выходами регистров номера нагрузки, а третьи входы схем И цодсоедннены к выходам распределителя, вход которого соединен с генератором импульсов, один выход устройства местного управления подключен ко входу первого регистра номера нагрузки, выход переполнения которого соединен со входом .второго регистра номера нагрузки, а выход переполнения второго регистра номера нагрузки подсоединен через схему ИЛИ и регистр коллекторной группы ко входу регистра эмиттерной группы, второй выход устройства местного управления подключен к сравнивающему устройству, а третий выход устройства местного управления цодсрединен через триггер к управляющим входам дещифраторов номера нагрузки.

-{ I ш

IT

PI У

I шу

1

:

,

У a

J; IJ.J

Уг/7-;А -«2Я

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| ЕНБЛИО-ГЕКАС. А. Петросян | 1971 |

|

SU291200A1 |

| УСТРОЙСТВО КРИПТОГРАФИЧЕСКОЙ ЗАЩИТЫ ИНФОРМАЦИИ | 2011 |

|

RU2475838C1 |

| Формирователь тестов | 1987 |

|

SU1552185A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU335718A1 |

| Формирователь тестов | 1989 |

|

SU1661769A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1983 |

|

SU1108507A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU604033A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

Уп

Даты

1968-01-01—Публикация