.(54) ЧАСТОТНО-ИМПУЛЬСНЫЙ КОМПАРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел | 1978 |

|

SU767753A1 |

| N-канальное устройство суммирования | 1981 |

|

SU982000A1 |

| Анализатор частотно-фазовых соотношений двух импульсных последовательностей | 1980 |

|

SU894849A1 |

| Устройство для сравнения чисел | 1979 |

|

SU920701A1 |

| Устройство для срвнения следующих друг за другом чисел | 1975 |

|

SU575645A2 |

| Цифро-аналоговое вычислительное устройство | 1973 |

|

SU475634A1 |

| Устройство для сравнения чисел | 1977 |

|

SU667966A1 |

| Устройство для сравнения чисел | 1978 |

|

SU763891A1 |

| Частотно-импульсный компаратор | 1987 |

|

SU1390775A1 |

| Устройство для сравнения чисел | 1981 |

|

SU960768A1 |

1

Изобретение относится к импульсной технике, автоматике и вычислительной технике и может использоваться при построении автоматизированных систем контроля и регулирования, а также в приборостроении.

Известно устройство для определения знака разности двух импульсных последовательностей, содержащее блок исключения совпадающих импупьсов, R,5 -триг- ,д геры, элементы И и инверторы 1 .

Недостатками этого устройства являются его сложность, обусловленная необходимостью применения блока исключения ,5 совпадающих импульсов, и малые функциональные возможности, так как оно не определяет меньшей входной частоты и не находит модуля разности частот.

Наиболее близким по технической сущ-20 ности к предлагаемому явгхябтся .устройство для определения знака разности двух частот, содержащее два триггерных блока вычитания частот, первые входы которых подключены ко входам устройства, а вторые к выходу элемента совпадения 21Недостатками известного устройства являются его малые функциональные возт ,можности, так как оно не мЪжет использоваться для выделения меньшей из входных частот и модуля разности частот.

Целью изобретения является расширение функциональных возможностей путем обеспечения возможности выделения меньшей входной частоты и разности входных частот.

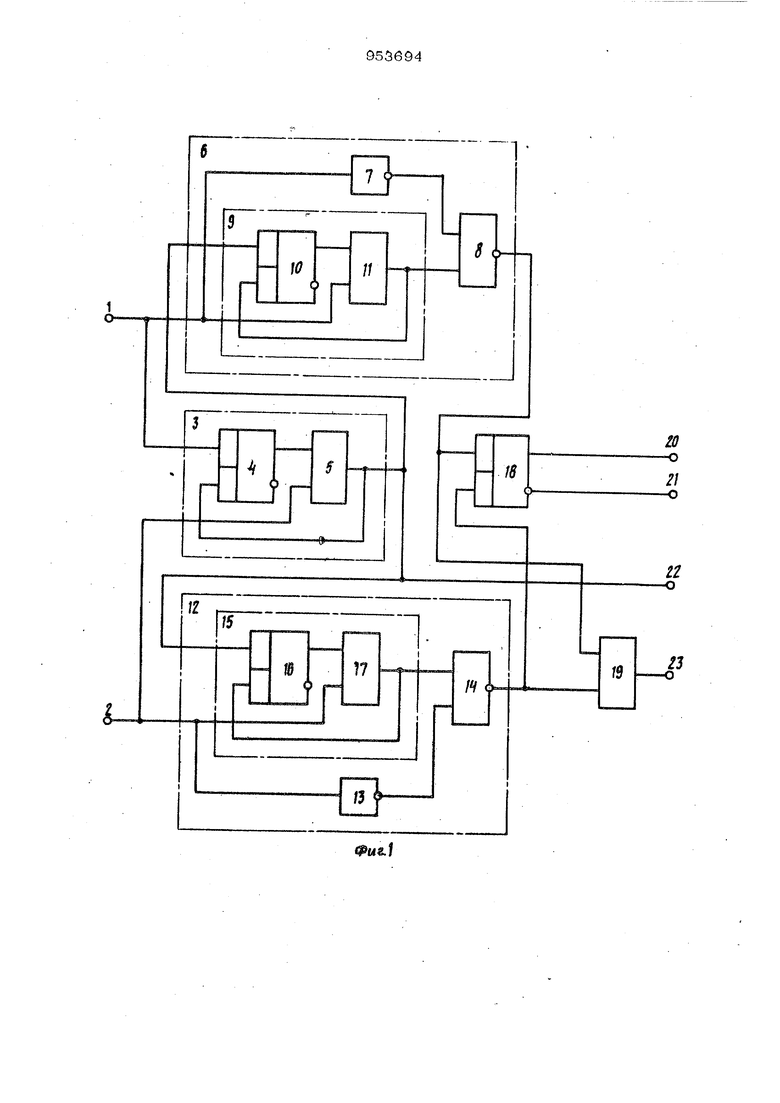

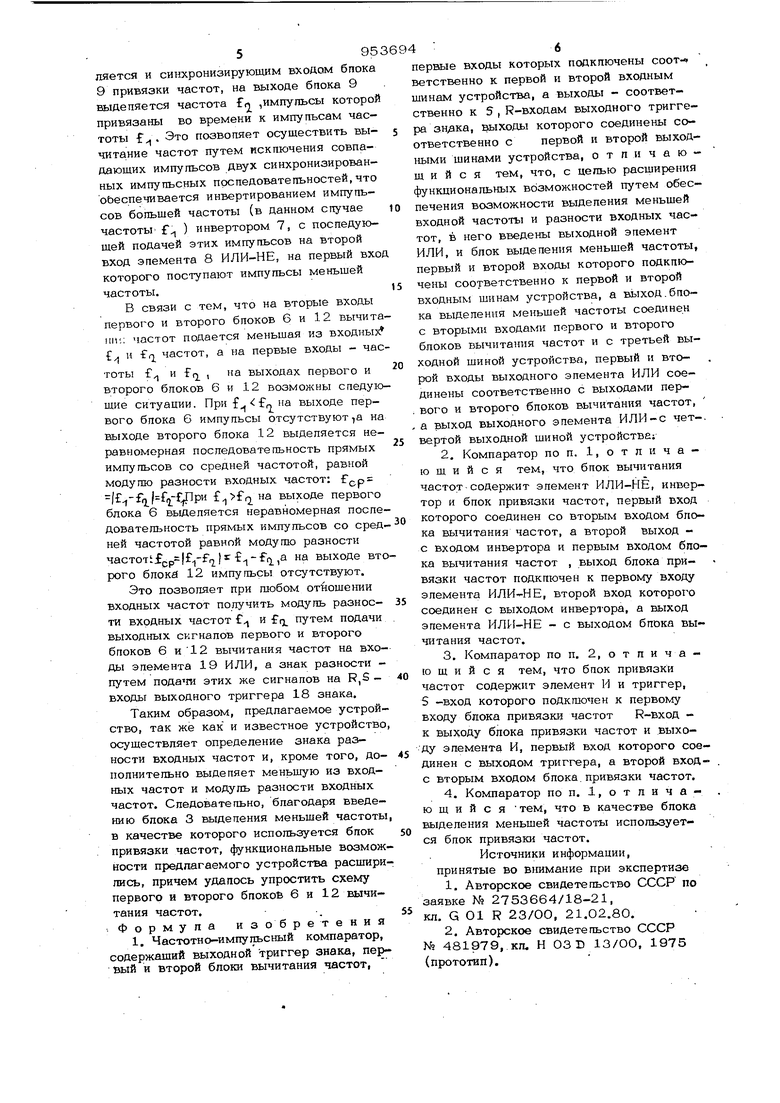

Поставленная цель достигается тем, что в частотно-импульсном компараторе, .содержащем выходной триггер знака, вый и второй блоки вь1читания частот, первые входы которых подключены соответственно к первой и второй входным шинам устройства, а выходы - соответственно к S , R-входам выходно1 о триггера знака, выходы которого соединены соответственно с первой и второй выходными шинами устройства, ввеД(-ны выходной эпемент ИЛИ и бпок выдепения меньшей частоты, первый и второй входь которого подкпючены соответственно к первой и Второй входным шинам устройства, а выход блока выдепения меньшей частоты соединен со вторыми входами первого и второго блоков вычитания частот и с треть.ей выходной шиной устройства, первый и второй входы выходного элемента ИЛИ соединены с соответственно с выходами первого и второго бпоков вычитания частот, а выход выходного элемента ИЛИ - с четвертой выходной шиной устройства, причем бпок вычитания частот содержит элемент ИЛИ-НЕ , инвертор и бпок привязки частот, первый вход которого соединен с вторым входом блока вычитания частот, а второй выход - со входом инвертора и первым входом блока вь1 читания частот, выход блока привязки час тот подключен к первому входу элемента ИЛИ-НЕ, второй вход которого соединен с выходом инвертора, а выход элемента ИЛИ-НЕ соединен с выходом блока вычитания частот.Блок привязки частот содержит эпемент И и триггер, 5 -вход которого подключен к первому входу блока привязки частот. R-вход - к выходу блока привязки частот и выходу элемента И, первый вход которого соединен с вьйсодом триггера, а второй вход - с вторым вхо дом блока привязки частот. В качестве блока выделения меньшей частоты используется бпок привязки частот. На фиг. 1 изображена структурная схе ма предлагаемого устройства; на фиг. временные диаграммы, характеризуюшие работу устройства. I Компаратор содержит первую и вторую входную шины 1 и 2, бпок 3 выдепения меньшей частоты, состоявдий из триггера 4 и элемента 5 И, первый блок 6 вычитания частот, состоящий из инвертора 7, элемента 8 ИЛИ-НЕ, блока 9 привязки частрт , состоящего из триггера 10, элемента 11 И, второй бпок 12 вычитания частот, состоящий из инвертора 13, элемента 14 ИЛИ-НЕ, бпок 15 привязки частот, состоящий из триггера 16, элемента 17 И, выходной триггер 18 знака, выходной элемент 19 ИЛИ, первую, вторую, третью и четвертую выход ные шины 20, 21, 22 и 23 устройства. Тастотно-импупьсный компаратор рабо тает следующим обрюзом. На первую и вторую входные шины 1 и 2 поступают сравниваемые частоты, представленные в виде последовательностей коротких импульсов (фиг. 2 а, б). Блок 3 выделения меньшей частоты осушествляет выделение меньшей из .входных частот, подаваемых на первую и вторую входные шины 1,2.s Блок работает следующим образом (фиг. 2). Импульсами частоты, поступающей на первую входную шину 1 компаратора (фиг. 2 а), триггер 4 устанавливается, например, в единичное состояние (фиг.2а), разрешающее прохождение последующего за этим моментом импупьса второй входной шины 2 устройства (фиг. 2 б) через элемент 5 И на выход блока 3 выделения меньшей частоты на R-вход триггера 4 (фиг. 2 г) с появлением которого триггер 4 устанавливается в нулевое состояние (фиг. 2 .в), подготавпиваясь к приему последующего импупьса с первой входной шины 1 устройства. Еспи (левая часть временных диаграмм, показанных на фиг. 2), то на выходе блока 3 выдепения меньшей частоты выделяется частота . , причем импульсы этой частоты будут привязаны во времени к импульсам частоты п.В этом случае указанное устройство работает в качестве блока привязки частот. Если fr (правая часть временных диаграмм, приведенных на фиг. 2), то, так как сброс триггера 4 осуществляется в соответствии с импульсами частоты, поступающей на вторую входную щину 2 устройства (фиг.2 б), на выходе блока 3 выдепения меньшей частоты выделяется частота ,Таким образом, при f fq на третью выходную шину 22 устройства поступают импульсы частоты fr ,а при ifc частоты f ,т. е. в обоих случаях устройство выделяет меньшую из входных частоты ., или (,. 11 Возможность предварительного определения меньшей частоты позволяет осущестЬить упрощение первого и второго блоков 9 и 12 вычитания частот, работу которых рассмотрим на первом блоке 6 компаратора при f связи с тем, что известная уже меньщая частота frj подается на вход вычитаемого первого блока 6 вычитания частот, который является информационным входом блока 9 : привязки частот, а большая частота f подается на вход уменьшаемого первого блока 6 вычитат;я частот, который яь595ляется и синхронизирующим входам блока 9 привязки частот, на выходе бпока 9 выделяется частота fn ,импульсы которой привязаны во времени к импупьсам частоты f . Это позволяет осуществить вычитание частот путем исключения совпадающих импульсов двух синхронизированных импульсных последовательностей, что оЬеспечивается инвертированием импульсов большей частоты (в данном случае частоты f; ) инвертором 7, с последующей подачей этих импульсов на второй вход элемента 8 ИЛИ-НЕ, на первый вхо которого поступают импупьсы меньшей частоты. В связи с тем, что на вторые входы первого и второго блоков 6 и 12 вычита пи;; частот подается меньшая из входны . н г частот, а на первые входы - час тоты f и f 0 , на выходах первого и второго блоков 6 и 12 возможны следую щие ситуации. При f fn а выходе первого блока 6 импульсы отсутствуют а на выходе второго блока 12 выделяется неравномерная последовательность прямых импульсов со средней частотой, равной модулю разности входных частот: 0 -l -fq l-{ff pii выходе первого блока 6 выделяется неравномерная после довательность прямых импульсов со сред ней частотой равной модулю разности 4acTOTtfpp |f -f,j, на выходе вто рого блока 12 импульсы отсутствуют. Это позволяет при любом отношении входных частот по.лучить модуль разности входных частот и f Q путем подачи выходных сигналов первого и второго блоков 6 и12 вычитания частот на входы элемента 19 ИЛИ, а знак разности путем подаш этих же сигналов на R,S входы выходного триггера 18 знака. Таким образом, предлагаемое устройство, так же как и известное устройство осуществляет определение знака разности входных частот и, кроме того, дополнительно выделяет меньшую из входных частот и модуль разности входных частот. Следовательно, благодаря введению блока 3 выделения меньшей частоты в качестве которого используется блок привязки частот, функциональные возможности предлагаемого устройства расширились, причем удалось упростить схему первого и второго блокоь 6 и 12 вычитания частот. Формула изобретения 1. Частотно-импульсный компаратор, содержащий выходной триггер знака, первый и второй блоки вычитания частот, 4 6 первые входы которых подключены COOT-F ветственно к первой и второй входным шинам устройства, а выходы - соответственно к 5 , R-входам выходного триггеpa зндка, выходы которого соединены соответственно с первой и второй выходнь1ми шинами устройства, отличающийся тем, что, с цепью расширения функциональных возможностей путем обес печения возможности выделения меньшей входной частоты и разности входных частот, Б него введены выходной элемент ИЛИ, и блок выделения меньшей частоты, первый и второй входы которого подключены соответственно к первой и второй входным шинам устройства, а выход.блока выделения меньшей частоты соединен с вторыми входами первого и второго блоков вычитания частот и с третьей выходной шиной устройства, первый и второй входы выходного элемента ИЛИ соединены соответственно с выходами первого и второго блоков вычитания частот, а выход выходного элемента И ЛИ-с чет-. вертой выходной шиной устройства; 2. Компаратор по п, 1, о т п и ч а ю щ и и с я тем, что блок вычитания частот-содержит элемент ИЛИ-НЁ, инвертор и блок привязки частот, первый вход которого соединен со вторым входом бпока вычитания частот, а второй выход с входом инвертора и первым входом блока вычитания частот , выход блока привязки частот подключен к первому входу элемента ИЛИ-НЕ, второй вход которого соединен с выходом инвертора, а выход элемента ИЛИ-НЕ - с выходом блока вычитания частот. 3. Компаратор по п. 2,отличаю щ и и с я тем, что блок привязки частот содержит элемент И и триггер, S -вход которого подключен к первому входу блока привязки частот R-вход - к выходу блока привязки частот и выхо У элемента И, первый вход которого выходом триггера, а второй входс вторым входом блока, привязки частот. 4. Компаратор по п. 1, отличающий с я тем, что в качестве блока Деления меньшей частоты испопьзует ° привязки частот, Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по аявке № 2753664/18-21, л. G О1 R 23/00, 21.02,80. 2.Авторское свидетельство СССР 481979, кп. Н 03 D 13/ОО, 1975 прототип).

м

h

/л

Фиг. 2 1ггп

Авторы

Даты

1982-08-23—Публикация

1981-03-23—Подача