(5) АНАЛИЗАТОР ЧАСТОТНО-ФАЗОВЫХ СООТНОШЕНИЙ ДВУХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-импульсный компаратор | 1981 |

|

SU953694A1 |

| -Канальное устройство дляСуММиРОВАНия чАСТОТ | 1979 |

|

SU817709A1 |

| Устройство задержки импульсногоСигНАлА | 1979 |

|

SU813739A1 |

| Устройство для определения знакаРАзНОСТи дВуХ иМпульСНыХ пОСлЕдОВАТЕльНОСТЕй | 1979 |

|

SU842611A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1037313A1 |

| Устройство выделения тактовых импульсов | 1986 |

|

SU1425864A2 |

| Сумматор @ частотно-импульсных сигналов | 1982 |

|

SU1156068A1 |

| Цифровой управляемый генератор | 1989 |

|

SU1748247A1 |

| Система связи с относительной фазовой и фазоимпульсной модуляцией | 1987 |

|

SU1559421A1 |

| Частотно-импульсный компаратор | 1987 |

|

SU1390775A1 |

Изобретение относится к импульсной технике и может использоваться в радиолокационных устройствах, а также при построении устройств автомати ки. Известно устройство для сравнения частот двух импульсных последователь ностей, содержащее триггер-накопител элементы И, инверторы, элементы ИЛИ, триггер временной задержки, устройство для вычитания частоты и исполь зуемое для контроля частоты тактовых импульсов путем определения момента совпадения импульсов входных частот tl 3. Недостаток этого устройства - его малые функциональные возможности, что объясняется отсутствием возможности выделения большей и меньшей из входных частот, частот с большей и меньшей фазой и определения знака разности входных импульсных последовательностей. Известно также устройство для определения знака разности двух импульсных последовательностей, содержащее три триггера, четыре элемента И и два элемента ИЛИ. Известное устройство может использоваться для нахождения знака разности частот при неравных входных частотных f fj или знака разности фаз двух импульсных последовательностей при f f l2. Недостатки этого устройства его малые функциональные возможности, что обусловлено отсутствием средств для сигнализации о равенстве частот и фаз входных импульсных последовательностей и возможности выделения большей и меньшей из входных:частот. Цель изобретения - расширение функциональных возможностей устройства путем обеспечения возможности

определения: знака разности и равенства частот двух импульсных сигналов, знака разности и равенства фаз импульсных последовательностей с частотами и выделения большей и меньшей из входных частот.

hocтaвлeннaя цель достигается тем, что в анализаторе частотно-фазовых соотношений двух импульсных последовательностей, содержащем блок вычитания частот, выход которого соединен с первым выходом анализатора, блок сключения совпадающих импульсов, первый и второй входы которого соединены со входами соответственно первого и второго элементов задержки, со, ходами первого элемента ИЛИ и со вхоами анализатора, а выходы подключены ко входам блока определения знака разности двух импульсных последовательностей, прямой выход которого соединен со вторым выходом анализатора и первыми входами первого и четвертого элементов И, а инверсный с первыми входами второго и третьего элементов И, причем выходы первого и второго элементов И подключены ко . входам второго элемента ИЛИ, а выходы третьего и четвертого элементов И - ко входам третьего элемента ИЛИ, введен блок определения равенства фаз входных последовательностей импульсов, выход первого элемента задержки соединен со вторыми входами первого и третьего элементов И, выход второго элемента задержки - со вторыми входами второго и четвертого элементов И, а выходы второго и третьего элементов ИЛИ - с третьим и четвертым выходами анализатора, выход второго элемента ИЛИ подключен ко входу уменьшаемого, а выход третьего элемента ИЛИ - ко входу вычитаемого блока вычитания частот, выход первого элемента ИЛИ соединен с первым входом, а выходы блока исключени совпадающих импульсов - со и третьим входами блока определения равенства фаз входных последовательностей импульсов, выход которого соединен с пятцм выходом анализатораi

Кроме того, блок вычитания частот выполнен в виде блока привязки импульсов вычитаемого к импульсам уменьшаемого, вход уменьшаемого соединен со входом третьего элемента

задержки, а выход упомянутого блока привязки подключен ко входу инвертора, выход которого и выход третьего элемента задержки связаны со входами пятого элемента И, подключенного к выходу блока вычитания частот,а блок определения равенства фаз входных последовательностей выполнен в виде выходного триггера, первый вход которого соединен с первым входом этого блока, а второй вход - с выходом четвертого элемента ИЛИ, входы которого являются вторым и третьим входами указанного блока.

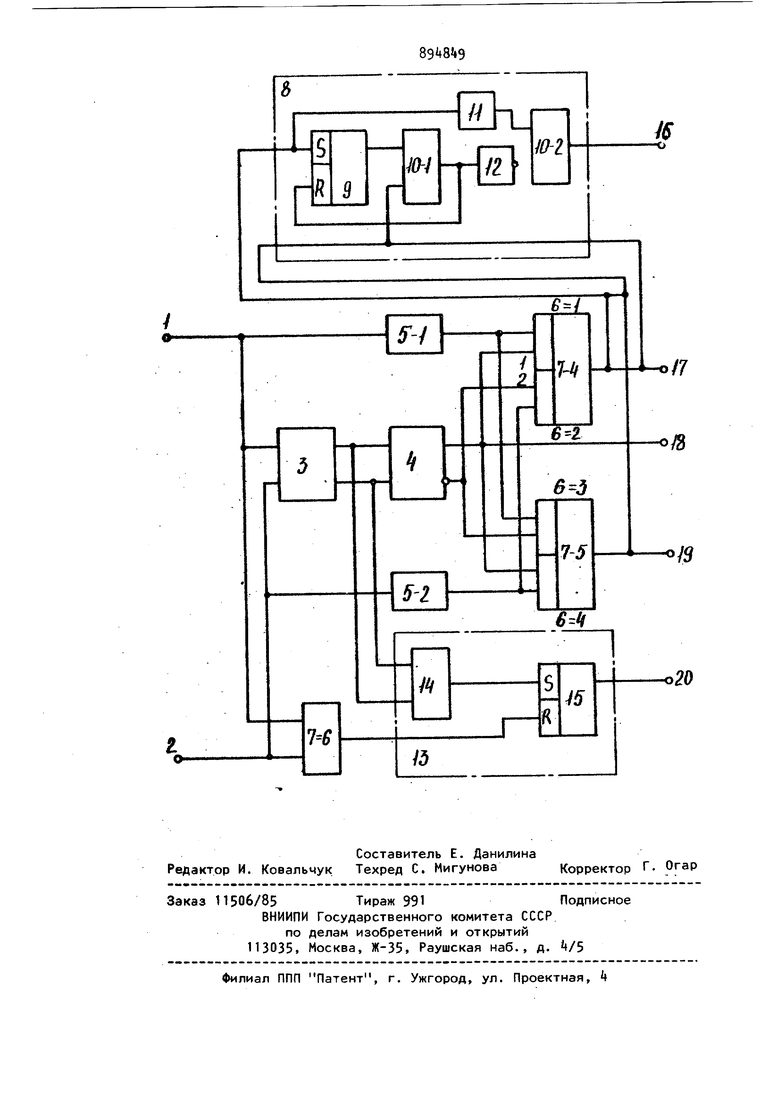

На чертеже приведена структурная схема анализатора частотно-фазовых соотношений двух импульсных последовательностей.

Аанализатор содержит входы 1 и 2 блок 3 исключения совпадающих импульсов, блок k определения знака разности двух импульсных последовательностей, элементы , .задержки, элементы И , , , 6, элементы ИЛИ , , , блок 8 вычитания частот, в состав которого входят RS-триггер 9, элементы И 10-1, 10-2, элемент 11 задержки и инвертор 12, причем RS-триггер 9 и элемент И образуют блок привязки импульсов вычитаемой частоты к импульсам уменьшаемой, блок 13 определения равенства фаз входных последовательностей, содержащий элемент ИЛИ Ik, RS-триггер 15, выходы 16-20.

Устройство работает следующим образом.

Блок 3 исключения совпадающих импульсов осуществляет исключение совпадающих импульсов последовательностей импульсов, поступающих на входы 1 и 2 анализатора. Блок определения знака разности двух последовательностей импульсов определяет знак ,разности частот входных сигнаf, fa

,где f.

1

лов, если

и

частоты сигналов, поступающих на входы 1 и 2, и определяет знак разности Оаз входных сигналов, если устанавливая при или Чо где Ч, и Ч5 - фаза импульсо входньГх 1 и 2 последовательностей, логическую единицу на прямом выходе (выход -18 анализатора) блока k определения знака разности импульсных последовательностей и логический нуль на его инверсном выходе. Если 0 или Ч -f, , состояние сигналов на прямом и инверсном выходах блока 4 меняется на противоположное При f. состояние выходных прямого и инверсного сигналов блока k обеспечивает прохождение на выход 17 устройства частоты f., , а на выход 19 частоты fq через соответственно элементы. и задержки длительность задержки которых выбирается равной длительности задержки в цепи определения знака разности двух импульсных последовательностей открытие единичным потенциалом с прямого выхода блока определения зн ка разности двух импульсных последо .вательностей элементов , , со ответственно элементов ИЛИ 7 и . В это время на инверсном выход блока устанавливается нулевой потенциал,запрещающий прохождение импульсов с выходов элементов задержки элементы И и . При f fn состояние сигналов на выходе блока меняется на проти воположное рассмотренному, ив этом случае большая частота поступа на выход 17 устройства с выхода эле мента задержки через открытый элемент И и элемент ИЛИ 7, а меньшая частота на выход 19 устройства с выхода элемента задержки через открытый элемент И и элемент ИЛИ . Таким образом, на выходах 18 и 19 анализатора выделяется большая и меньшая частота, как при f 7 fj.) так и при f, f,. Уст роист во работ ет аналогично при f , f Q.; т.е. при равных входных частотах на выходе 17 выделяется сигнал с бол шей фазой, а на выходе 19 - сигнал меньшей фазой. Сигнализация о равенстве входных частот осуществляется с помощью бло ка 8 вычитания частот, выходы которого соединены с выходами 17, 19 соответственно большей и .меньшей частот.Благодаря тому, что выходы большей и меньшей из входных частот известны, вычитание этих частот в блоке 8 можно произвести путем привязки импульсов меньшей частоты к импульсам большей частоты, что осуществляется схемой привязки, содержащей, например RS-триггер 9 и элемент И с последующей подачей на первый вход элемента И 96 выходного сигнала схемы привязки через инвертор 12 и на второй вход элемента И прямого сигнала боль шей частоты, задержанного элементом 11 задержки на время Т задержки сигнала меньшей частоты от момента его поступления на вход блока вычитания до момента его прихода на первый вход элемента И . В данном случае tt. 2У, где i время задержки интегральных элементов, на которых собирается устройство. Благодаря такой привязке и соответствующей задержке сигнала большей частоты на входах элемента И выделяется: на первом - прямой си1- нал большей частоты, а на втором инверсный меньшей частоты, привязанный во времени к соответствующим импульсам вь1сокой .частоты. Следовательно, на выходе элемента И и на выходе 1б анализатора выделяется последовательность импульсов, средняя частота которых равна разности частот сигналов, поступающих на входы 1 и 2 при f f,. При При т f г,. fn ИМПУЛЬСЫ на выходе 16 с1налип импульсы на выходе затора отсутствуют, так как разность входных частот равна нулю, что сигнализирует о равенстве входных частот. Для сигнализации о моменте равенства фаз .последовательностей импульсов с равными входными частотами f ff, подаваемыми на входы 1 и 2 анализатора, используется блок 13 определения равенства фаз входных последовательностей. Зто осуще.ствляется путем подачи на входы RS-триггера 15, выход которого служит выходом 20 анализатора, сигнала равного сумме частот входных сигналов с выхода элемента ИЛИ , на первый вход сигналов с выходов блока исключения совпадающих импульсов через элемент ИЛИ It на второй вход. Суммарный сигнал с выхода элемента ИЛИ осуществляет, например, сброс RS-триггера .15 в нулевое состояние, Если выходные частоты равны и их импульсы совпадают, т.е. Vn , то на выходах блока 3 исключения совпадающих импульсов импульсы отсутствуют, следовательно, они отсутствуют и на выходе элемента ИЛИ k. В этом случае RS-триггер 13 находитя все время в нулевом состоянии. ри неравенстве фаз входных частот, акже как и при неравенстве входных I мастит, RS-триггер 15 переключается Следоват-ельно, установка RS-триггер 15 в нулевое состояние сигнализирует о равенстве фаз двух равных вход ных частот. Таким образом, предлагаемое устройство осуществляет определение зн ка разности двух частот при f f и определение знака разности фаз вх ных последовательностей при f f. Кроме того, оно позволяет выделять большую и меньшую из входных частот находить разность входных частот и определять момент их равенства, определять момент равенства фаз входных импульсных последовательностей при равных входных частотах. Формула изобретения 1. Аанализатор частотно-фазовых соотношений двух импульсных последо вательностей, содержащий блок вычитания частот, выход которого соединен с первым выходом анализатора, блок исключения совпадающих импульсов, первый и второй входы которого соединены со входами соответственно первого и второго элементов задержки, со входами первого элемента ИЛИ и со входами анализатора, а выходы подключены ко входам блока определе ния-знака разности двух импульснь1х последовательностей, прямой выход к г торого соединен со вторым выходом анализатора и с первыми входами пер вого и четвертого элементов И, а инверсный - с первыми входами второ го и третьего элементов И, причем выходы первого и второго элементов подключены ко входам второго элемен та ИЛИ, а выходы третьего и четвертого элементов И - ко входам третье элемента ИЛИ, отличающийс я тем, что, с целью расширения функциональных возможностей, в него введен блок определения равенства фа входных последовательностей импульсов, выход первого элемента задержки соединен со вторыми входами первого и третьего элементов И, выход второго элемента задержки - со вторыми входами второго и четвертого элементов И, а выходы второго и третьего элементов ИЛИ - с третьим и четвертым выходами анализатора, выход второго элемента ИЛИ подключен ко входу уменьшаемого, а выход третьего элемента ИЛИ - ко входу вычитаемого блока вычитания частот, выход первого элемента ИЛИ соединен с первым входом, а выходы блока исключения совпадающих импульсов - с вторым и третьим входами блока определения равенства фаз входных последовательностей импульсов, выход которого соединен с пятым выходом анализатора. .2. Анализатор по п.1, о т л и чающийся тем, что блок вычитания выполнен в виде блока привязки импульсов вычитаемого к импульсам уменьшаемого, вход уменьшаемого соединен со входом третьего элемента задержки, а выход упомянутого блока привязки подключен ко входу инвертора, выход которого и выход третьего элемента задержки связаны со входами пятого элемента И, выходом подключенного к выходу блока вычитания частот. 3. Анализатор по п.1, отличающийся тем, Что блок определения равенства фаз входных последовательностей выполнен в виде выходного триггера, первый вход которого соединен с первым входом этого блока, а второй вход - с выходом четвертого элемента ИЛИ, входы которого являются вторым и третьим входами указанного блока. Источники информации, принятые во внимание при экспертизе 1.Патент ФРГ № 2039557, кл. Н 01 35/20, 1979. 2.Авторское свидетельство СССР по заявке № 275366V18-21, кл. G 01 R 23/00, 1979.

Авторы

Даты

1981-12-30—Публикация

1980-05-08—Подача