(S) УСРЕДНИТЕЛЬ-АНАЛИЗАТОР СПЕКТРА ФУРЬЕ

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор спектра | 1987 |

|

SU1552117A1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| Цифровой анализатор спектра в ортогональном базисе | 1983 |

|

SU1124326A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Анализатор спектра Фурье | 1987 |

|

SU1387010A1 |

| Анализатор спектра случайныхпРОцЕССОВ | 1979 |

|

SU838600A1 |

| Цифровой генератор спектра фурье | 1973 |

|

SU446063A1 |

| Анализатор спектра Фурье | 1978 |

|

SU877554A1 |

| Устройство для приема последовательности импульсно-временных кодов | 1987 |

|

SU1483478A1 |

| Адаптивный коррелометр | 1979 |

|

SU809196A1 |

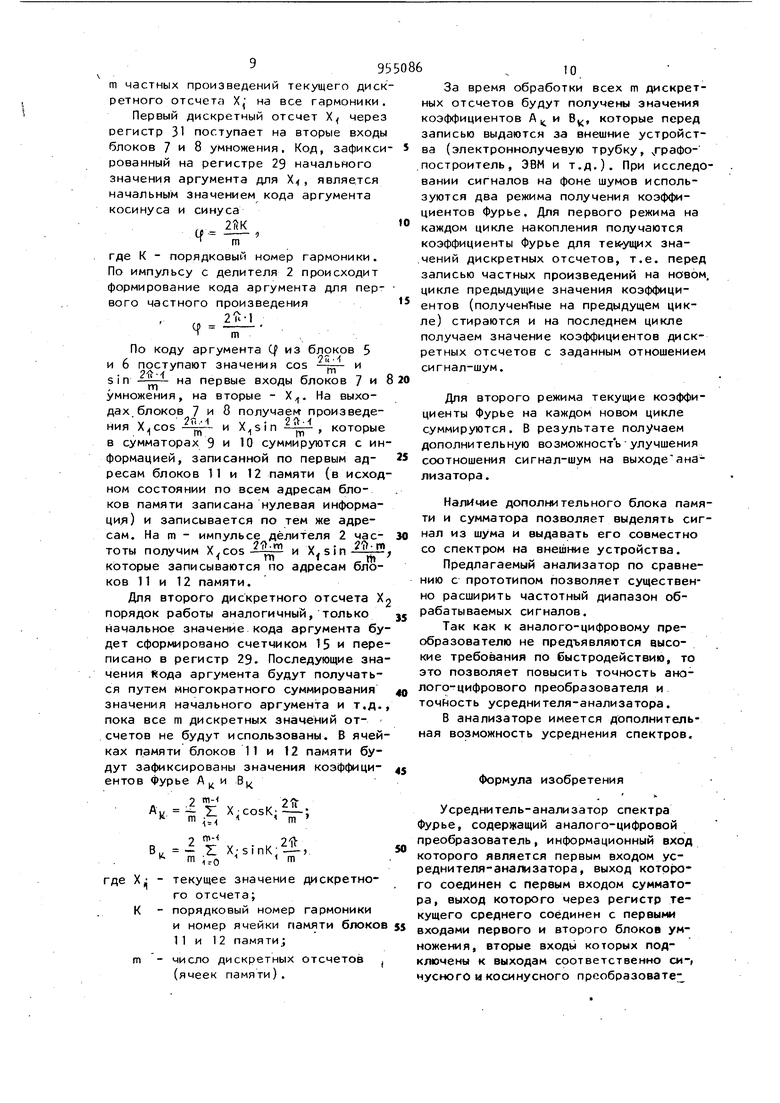

Изобретение относится к цифровой электроизмерительной технике и предназначено для выделения сигналов из шума и определения коэффициентов Фурье высокочастотных процессов аппаратурой ограниченного быстродействия и может быть использовано в спектрометрии, системах автоматического управления, технического контроля и т.д.to

Известен аналого-цифровой спектральный анализатор Фурье, содержащий генератор импульсов, аналого-цифровой преобразователь, перестраиваемый фильтр, интеграторы, вычислительный is блок, запоминающее устрдйство.

Работа этого анализатора основана на предварительной дискретизации и квантовании входного сигнала и записи его в двоичном коде в запоминаю- 20 щее устройство. После записи входного сигнала в виде дискретных отсчетов производится многократное считывание

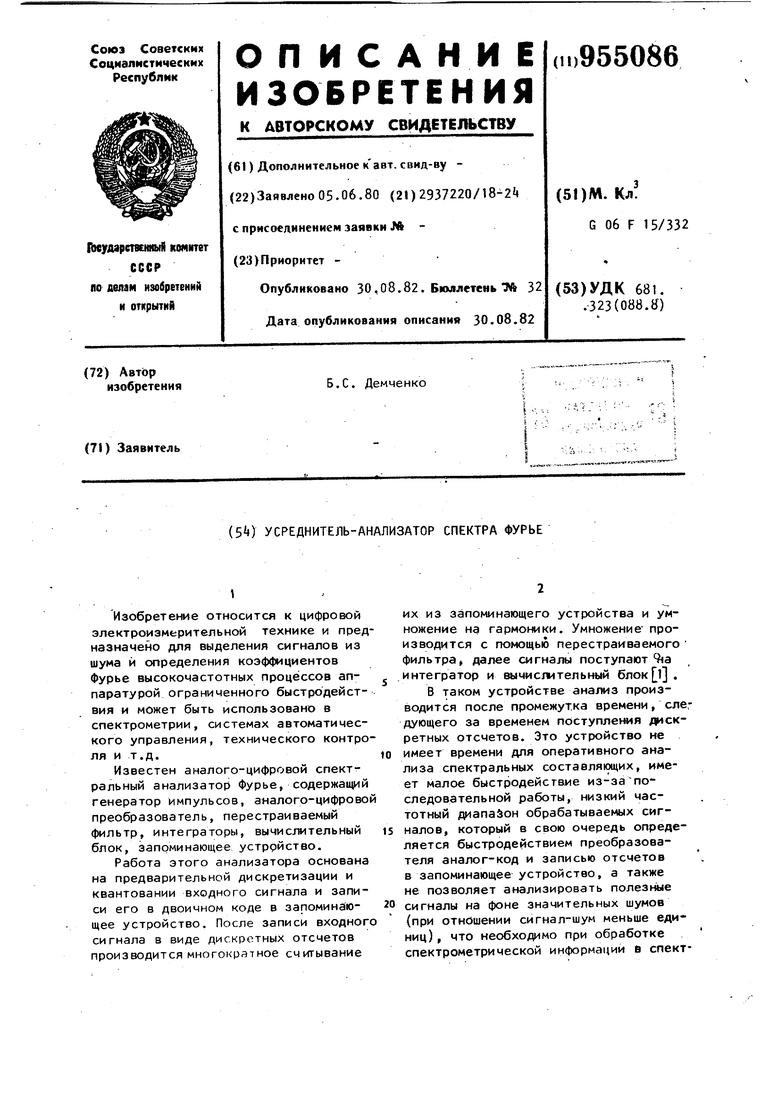

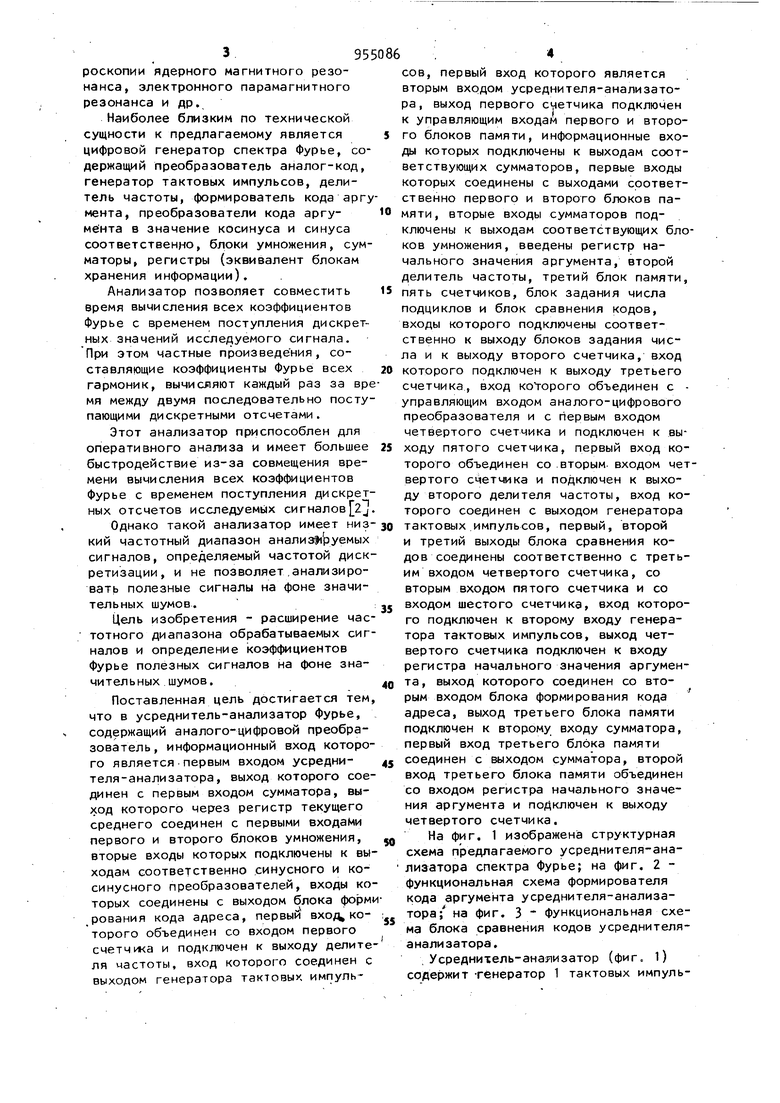

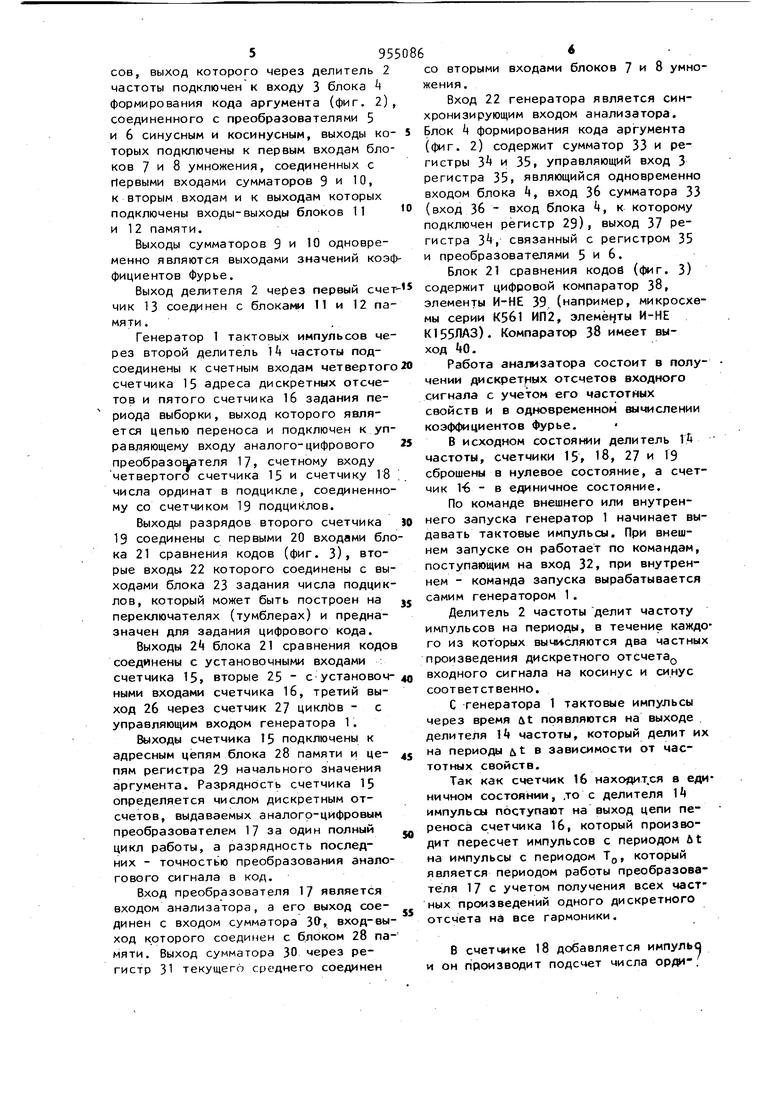

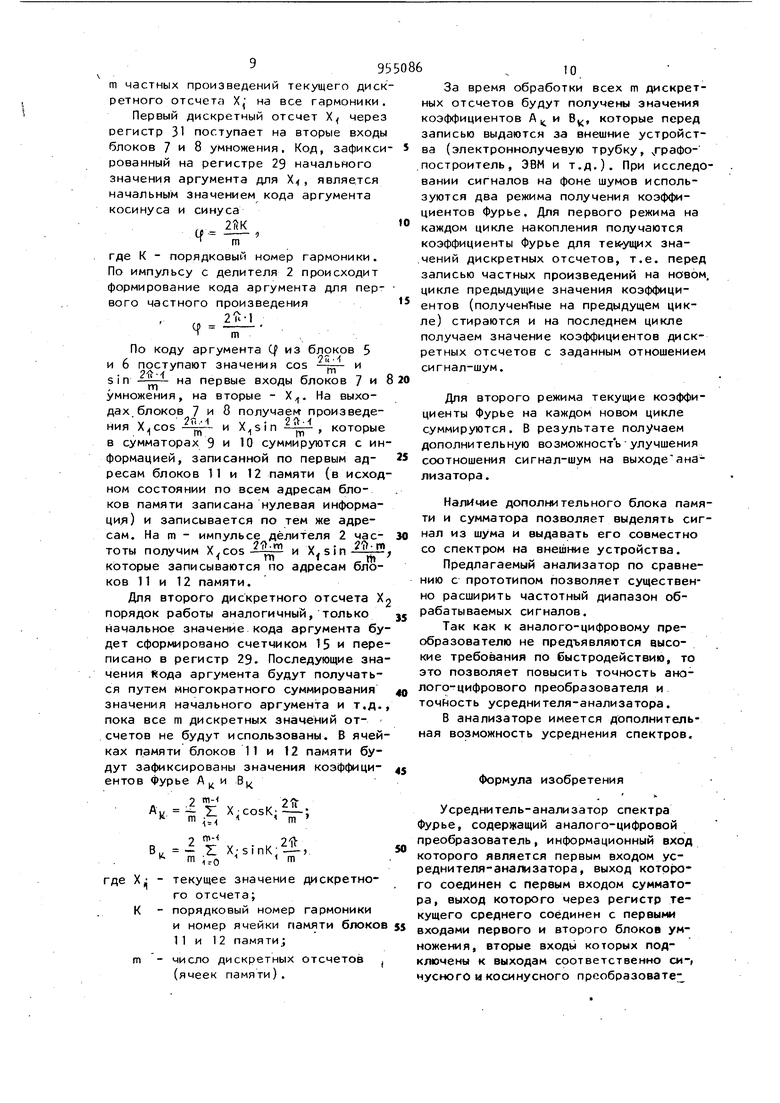

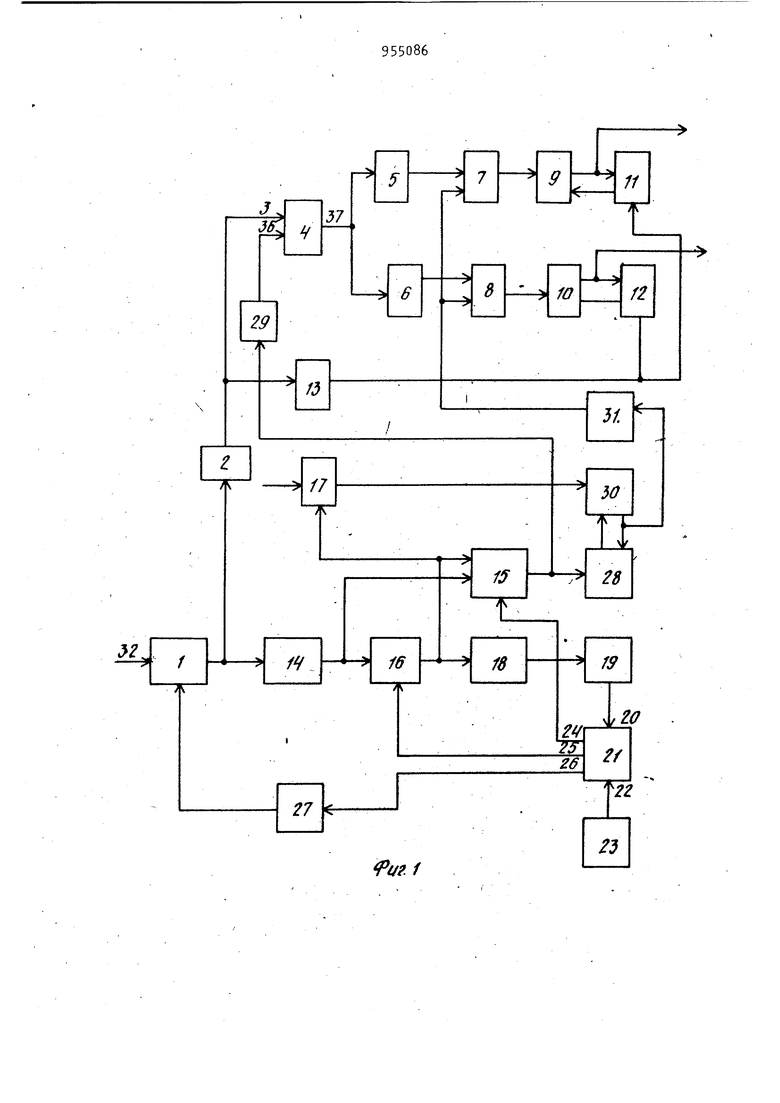

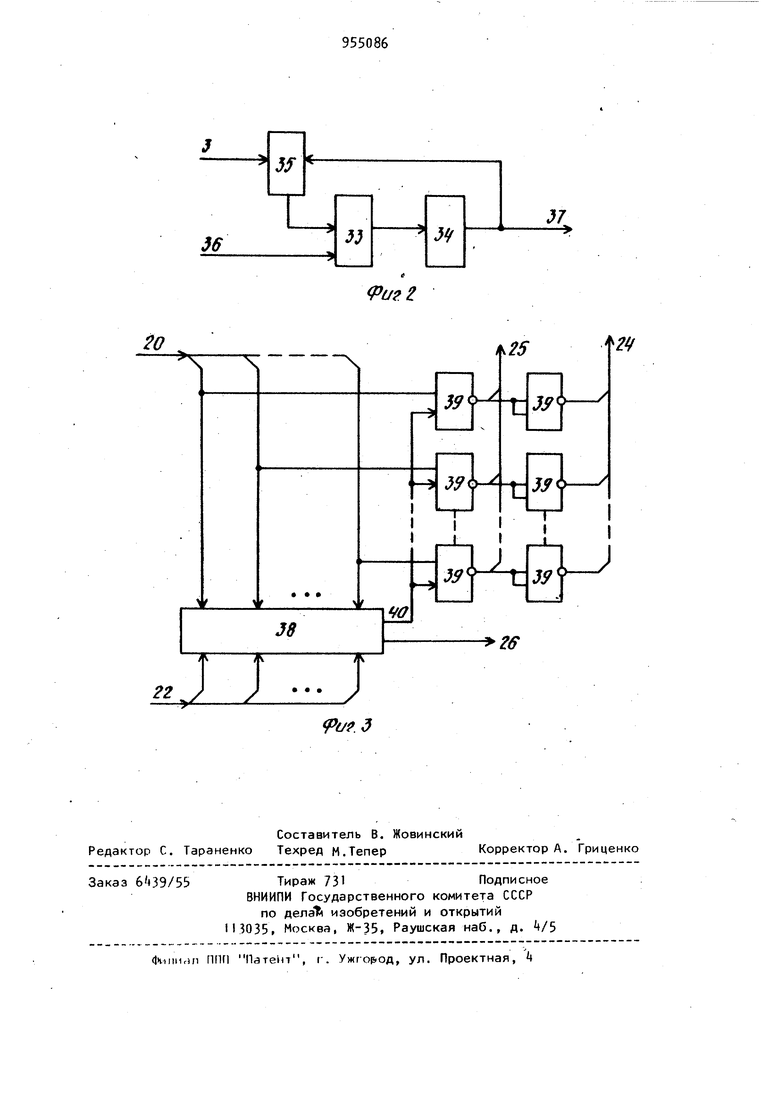

их из запоминающего устройства и умножение на гармоники. Умножение производится с помощью перестраиваемого фильтра, далее сигналы поступают 9ia интегратор и вычислительный . В таком устройстве анализ производится после промежутка времени, еле,дующего за временем поступления дискретных отсчетов. Это устройство не имеет времени для оперативного анализа спектральных составляющих, имеет малое быстродействие из-запоследователь ной работы, низкий частотный диапазон обрабатываемых сигналов, который в свою очередь определяется быстродействием преобразователя аналог-код и записью отсчетов в запоминающее устройство, а также не позволяет анализировать полезные сигналы на фоне значительных шумов (при отношении сигнал-шум меньше единиц) , что необходимо при обработке спектрометрической информации в спект3.95 роскопии ядерного магнитного резонанса, электронного парамагнитного резонанса и др. Наиболее близким по технической сущности к предлагаемому является цифровой генератор спектра Фурье, содержащий преобразователь аналог-код, генератор тактовых импульсов, делитель частоты, формирователь кода аргу мента, преобразователи кода аргумента в значение косинуса и синуса соответственно, блоки умножения, сумматоры, регистры (эквивалент блокам хранения информации). Анализатор позволяет совместить время вычисления всех коэффициентов Фурье с временем поступления дискретных значений исследуемого сигнала, При этом частные произведения, составляющие коэффициенты Фурье всех гармоник, вычисляют каждый раз за вре мя между двумя последовательно посту пающими дискретными отсчетами. Этот анализатор приспособлен для оперативного анализа и имеет большее быстродействие из-за совмещения времени вычисления всех коэффициентов Фурье с временем поступления дискрет ных отсчетов исследуемых сигналов 2j Однако такой анализатор имеет низкий частотный диапазон анализ 1руемых сигналов, определяемый частотой дискретизации, и не позволяет.анализировать полезные сигналы на фоне значительных шумов. Цель изобретения - расширение частотного диапазона обрабатываемых сигналов и определение коэффициентов Фурье полезных сигналов на фоне значительных шумов. Поставленная цель достигается тем, что в усреднитель-анализатор Фурье, содержащий аналого-цифровой преобразователь , информационный вход которого является первым входом усреднителя-анализатора, выход которого соединен с первым входом сумматора, выход которого через регистр текущего среднего соединен с первыми входами первого и второго блоков умножения, вторые входы которых подключены к выходам соответственно синусного и косинусного преобразователей, входы которых соединены с выходом блока форми рования кода адреса, первый вхо/ которого объединен со входом первого счетчика и подключен к выходу делите ля частоты, вход которого соединен с выходом генератора тактовых импульсов, первый вход которого является вторым входом усреднителя-анализатора, выход первого счетчика подключен к управляющим входам первого и второго блоков памяти, информационные входы которых подключены к выходам соответствующих сумматоров, первые входы которых соединены с выходами соответственно первого и второго блоков памяти, вторые входы сумматоров подключены к выходам соответствующих блоков умножения, введены регистр начального значения аргумента, второй делитель частоты, третий блок памяти, пять счетчиков, блок задания числа подциклов и блок сравнения кодов, входы которого подключены соответственно к выходу блоков задания числа и к выходу второго счетчика, вход которого подключен к выходу третьего счетчика, вход которого объединен с управляющим входом аналого-цифрового преобразователя и с первым входом четвертого счетчика и подключен к выходу пятого счетчика, первый вход которого объединен со .вторым, входом четвертого счетчика и подключен к выходу второго делителя частоты, вход которого соединен с выходом генератора тактовых импульсов, первый, второй и третий выходы блока сравнения кодов соединены соответственно с третьим входом четвертого счетчика, со вторым входом пятого счетчика и со входом шестого счетчика, вход которого подключен к второму входу генератора тактовых импульсов, выход четвертого счетчика подключен к входу регистра начального значения аргумента, выход которого соединен со вторым входом блока формирования кода адреса, выход третьего блока памяти подключен к второму входу сумматора, первый вход третьего блока памяти соединен с выходом сумматора, второй вход третьего блока памяти объединен со входом регистра начального значения аргумента и подключен к выходу четвертого счетчика. На фиг. 1 изображена структурная схема предлагаемого усреднителя-анализатора спектра Фурье; на фиг. 2 функциональная схема формирователя кода аргумента усреднителя-анализатора; на фиг. 3 функциональная схема блока сравнения кодов усреднителяанализатора. , Усредни-кель-анаяизатор (фиг. 1) содержит -генератор 1 тактовых импульсов, выход которого через делитель частоты подключен к входу 3 блока k формирования кода аргумента (фиг. 2 соединенного с преобразователями 5 и 6 синусным и косинусным, выходы к торых подключены к первым входам бло ков 7 и 8 умножения, соединенных с Первыми входами сумматоров 9 и 10, к вторым входам и к выходам которых подключены входы-выходы блоков 11 и 12 памяти. Выходы сумматоров 9 и 10 одновременно являются выходами значений коэ фициентов Фурье. Выход делителя 2 через первый сче чик 13 соединен с блoкa в 11 и 12 па мяти. Генератор 1 тактовых импульсов че рез второй делитель k частоты подсоединены к счетным входам четвертог счетчика 15 адреса дискретных отсчетов и пятого счетчика 16 задания периода выборки, выход которого является цепью переноса и подключен к уп равляющему входу аналого-цифрового преобразователя 17, счетному входу четвертого счетчика 15 и счетчику 18 числа ординат в подцикле, соединенно му со счетчиком 19 подциклов. Выходы разрядов второго счетчика 19 соединены с первыми 20 входами бл ка 21 сравнения кодов (фиг. 3), вторые входы 22 которого соединены с вы ходами блока 23 задания числа подцик лов, который может быть построен на переключателях (тумблерах) и предназначен для задания цифрового кода. Выходы блока 21 сравнения кодо соединены с установочными входами сметчика 15, вторые 25 - с установоч ными входами счетчика 16, третий выход 2б через счетчик 27 циклЬв - с управляющим входом генератора Г. Выходы счетчика 15 подключены к адресным цепям блока 28 памяти и цепям регистра 29 начального значения аргумента. Разрядность счетчика 15 определяется числом дискретным отсчетов, выдаваемых аналого-цифровым преобразователем 17 за один полный цикл работы, а разрядность последних - точностью преобразования анало гового сигнала в код. Вход преобразователя 17 является входом анализатора, а его выход соединен с входом сумматора З, вход-вы ход которого соединен с 28 па мяти. Выход сумматора 30 через регистр 31 текущего среднего соединен со вторыми входами блоков 7 и 8 умножения. Вход 22 генератора является синхронизирующим входом анализатора. Блок k формирования кода аргумента (фиг. 2) содержит сумматор 33 и регистры 3 и 35, управляющий вход 3 регистра 35, являющийся одновременно входом блока , вход Зб сумматора 33 (вход 36 - вход блока k, к которому подключен регистр 29), выход 37 регистра З, связанный с регистром 35 и преобразователями 5 и 6. Блок 21 сравнения КОДОЁ (фиг. 3) содержит цифровой компаратор 38, элементы И-НЕ 39, (например, микросхемы серии К561 ИП2, элементы И-НЕ К155ЛАЗ). Компаратор 38 имеет выход 0. Работа анализатора состоит в получении дискретных отсчетов входного сигнала с учетом его частотных свойств и в од|« временном вычислении коэффициентов Фурье. В исходном состоянии делитель ТА частоты, счетчики 15, 18, 27 и 19 сброшены в нулевое состояние, а счетчик 1-6 - в единичное состояние. По команде внешнего или внутреннего запуска генератор 1 начинает выдавать тактовые импульсы. При внешнем запуске он работает по командам, поступающим на вход 32, при внутреннем - команда запуска вырабатывается самим генератором 1. Делитель 2 частоты делит частоту импульсов на периоды, в течение каждого из которых вычисляются два частных произведения дискретного отсчета входного сигнала на косинус и синус соответственно, С генератора 1 тактовые импульсы через время ut появляются на выходе делителя частоты, который делит их на периоды its зависимости от частотных свойств. Так как счетчик 16 находит.ся а единичном состоянии, .то с делителя 1 импульсы поступают на выход цепи переноса счетчика 16, который производит пересчет импульсов с периодом ut на импульсы с периодом Т, который является периодом работы преобразователя 17 с учетом получения всех частных произведений одного дискретного отсчета на все гармоники. В счетчике 18 добавляется импульс он производит подсчет числа . нат (дискретных отсчетов в подцикле Объем этого счет1 1ка равен t m m - где q To/ut; общее количество дискретных m - отсчетов, которыми представляется входной аналоговый сигнал. По заднему фронту импульса At заносится импульс из счетчика 16 в счетчик 15, а во время импульса д1 выдается код адреса определяемого дискретного отсчета на адресный вход блока 28 памяти, и в преобразователь 17 производится выборка входного сиг нала. Из блока 28 по первому адресу счи тывается содержимое (в исходном состоянии во всех ячейках памяти была записана нулевая информация) и подается на второй вход сумматора 30, а на первый его вход поступает значение дискретного отсчета с выхода пресзбразователя 17. Результат суммирования записывается в регистр 31 и в ту же ячейку блока 28. Через время TQ на выходе счетчика 16 появл ется команда выборки, которая запускает вторично преобразователь 1/, разрешает выдачу кода адреса fo счет чика, 15 на адресные цепи блока 28 и добавляет импульс в счетчик 18. В счетчике 15 за время TQ насчитывается q импульсов. По этим кодам из блока 28 памяти считывается информация , суммируется с сигналами вторых дискретных отсчетов из преобразователя 17 и записывается в регистр 31 и по тому же адресу в блок 28. Последующие дискретные отсчеты будут считываться и записываться в блок 28 по адресам 2q,3q. «niq. Пос ле получения т дискретных отсчетов в счетчик 19 подциклов заносится еди ница, делитель частоты, счетчики 46, 18 и 15 сбрасываются в нуль. При кодах на входах 20 меньших, чем на входах 22 цифрового компаратора 38 (фиг. 3), на выходе появляется раз решающий потенциал и соответственно на выходах 2k и 25 появляется прямой и обратный к-од счетчика 19, который заносится п счегмики 16 и 15. Оствнавливлетгя работа генератора 1. На этом ра(5от,ч на первом подцикле закан чивлетс . 9 Далее поступает второй синхроимпульс на вход 32 генератора. 1,соответствующий вторичной синхронной развертке входног;9 сигнала. Запускается генератор 1 и начинается второй подцикл получения дискретных отсчетов. Первая команда выборки на выходе счетчика 16 появится через иt по отношени(р к первой команде выборки в первом подцикле, так как в конце первого подцикла в счетчик 16 занесен обрёт-. ный код единицы, а в счетчике 15 занесен код единицы в прямом коде. В результате информация из блока 28 считывается по второму адресу и после сложения с дискретным отсчетом записывается по тому же адресу. Для последующих дискретных отсчетов второго подцикла информация будет считываться из блока 28 памяти по адресам q+1, 2q+1 , 3q+1,. . .mfc|+ 1 , суммироваться с дискретными отсчетами и записываться по тем же адресам. Для последнего подцикла команда выборки со счетчика 16 сдвигается на (q-l)ut по отношению к первой команде выборки в первом подцикле, а информация с блока 28 считывается по адресам (q+m,2q+m, 3q+ni,... .mq+m ). После определения последнего дискретного отсчета на q - 1 подцикле в блоке 21 сравнения кодов происходит сравнение кода, зафиксированного на счетчике 19 и установленного на блоке 23 задания числа подциклов. В результате делитель 1 частоты, счетчики 16, 18, 19 и 15 сбрасываются в нуль, в счетчик 27 добавляется единица, а в счетчики 16 и 15 по установочным входам заносится код нуля из счетчика 19 в обратном и прямом кодах соответственно. На этом полный цикл получения в дискретных отсчетов заканчивается. При наличии повторяющихся полезных сигналов в шуме производится выделение сигналов из шума. Для этого на счетчике 27, исходя из требуемого соотношения сигнал-шум, устанавливается необходимое число циклов накопления и производится запуск анализатора, после достижения необходимого числа циклов накопления в ячейках памяти записаны дискретные отсчеты с заданными соотношением сигнал-шум. Работа по циклам аналогична работе для одного цикла получения дискретных отсчетов входного сигнала. Одновременно с получением дискретпых отсчетов за время Т вычисляется 99 m частных произведений текущего диск ратного отсчета X, на все гармоники Первый дискретный отсмет Х через регистр 31 поступает на вторые входы блоков 7 и 8 умножения. Код, зафикси рованный на регистре 29 начального значения аргумента для Х, является начальным значением кода аргумента косинуса и синуса W - о m где К - порядковый номер гармоники. По импульсу с делителя 2 происходит формирование кода аргумента для первого частного произведения 2 , m По коду аргумента Ср из блоков 5 и 6 поступают значения cos и sin L. на первые входы блоков 7 и умножения, на вторые - Х. На выходах блоков 7 и 8 получаем произведе-j , которые в сумматорах 9 и 10 суммируются с ин формацией, записанной по первым адресам блоков 11 и 12 памяти (в исход ном состоянии по всем адресам блоков памяти записана нулевая информация) и записывается по тем же адресам. На m - импульсе делителя 2 импульсе делителя П-т тоты получим X,cos - J. и f -rtT которые записываются по адресам блоков 11 и 12 памяти. Для второго дискретного отсчета Х порядок работы аналогичный, только начальное значение.кода аргумента бу дет сформировано счетчиком 15 и пере писано в регистр 29. Последующие зна чения аргумента будут получаться путем многократного суммирования значения начального аргумента и т.д. пока все m дискретных значений отсчетов не будут использованы. В ячей ках памяти блоков 11 и 12 памяти будут зафиксированы значения коэффициентов Фурье А и о т- А), Ц X COSK; m Ь . ,, 21 В. Z X, sinK; -) m текущее значение дискретного отсчета; порядковый номер гармоники и номер ячейки памяти блоков 11 и 12 памяти; число дискретных отсчетов (ячеек памяти). часЗа время обработки всех m дискретных отсчетов будут получены значения коэффициентов А | и By,, которые перед записью выдаются за внешние устройства (электроннолучевую трубку, графопостроитель, ЭВМ и т.д.). При исследовании сигналов на фоне шумов используются два режима получения коэффициентов Фурье. Для первого режима на каждом цикле накопления получаются коэффициенты Фурье для текущих зна.чений дискретных отсчетов, т.е. перед записью частных произведений на новом, цикле предыдущие значения коэффициентов (полученные на предыдущем цикле) стираются и на последнем цикле получаем значение коэффициентов дискретных отсчетов с заданным отношением сигнал-шум. Для второго режима текущие коэффициенты Фурье на каждом новом цикле суммируются. В результате получаем дополнительную возможность улучшения соотношения сигнал-шум на выходеанализатора . Наличие дополнительного блока памяти и сумматора позволяет выделять сигнал из шума и выдавать его совместно со спектром на внешние устройства. Предлагаемый анализатор по сравнению с прототипом позволяет существенно расширить частотный диапазон обрабатываемых сигналов. Так как к аналого-цифровому преобразователю не предъявляются высокие требования по быстродействию, то это позволяет повысить точность анолого-цифрового преобразователя и точность усреднителя-анализатора. В анализаторе имеется дополнительная возможность усреднения спектров. Формула изобретения Усреднитель-анализатор спектра Фурье, содержащий аналого-цифровой преобразователь, информационный вход которого является первым входом уседнителя-анализатора, выход KOTQJX)го соединен с первым входом сумматоа, выход которого через регистр текущего среднего соединен с первыми вводами первого и второго блоков уможения, вторые входь) которых подлючены к выходам соответственно си-, усного и косинусного прсобразовате;

леи, входы которых соединены с выходом блока формирования кода адреса, первый вход которого объединен с входом первого счетчика и подключен к выходу делителя частоты, вход которогр соединен с выходом генератора тактовых импульсов, первый вход которого является вторым входом усреднителя-анализатора, выход первого счетчика подключен к управляющим входам первого и второго блоков памяти, информационные, входы которых подключены к выходам соответствующих сумматоров, первые входы которых соединены с выходами соответственно первого и второго блоков памяти, вторые входы сумматоров подключены к выходам соответствующих блоков умножения отличающийся тем, что, с целью расширения диапазона частот входных сигналов, в усреднитель-анализатор введены регистр начального значения аргумента, второй делитель частоты, третий блок памяти, пять счетчиков, блок задания числа подциклов и блок сравнения кодов, входы которого подключены соответственно к выходу блока задания числа подциклов и к выходу второго счетчика, вход которого подключен к выходу третьего счетчика, вход которого о§ъединен с управляющим входом аналого-цифрового преобразователя и с первым

входом четвертого счетчика и подключен к выходу пятого счетчика, первый вход которого объединен с вторым входом четвертого счетчика и подключен к выходу второго делителя частоты, вход которого соединен с выходом генератора тактовых импульсов, первый, второй и третий выходы блока сравнения кодов соединены соответственно с третьим входом четвертого счетчика, с вторым входом пятого счетчика и с входом шестого счетчика, выход которого подключен к второму входу генератора тактовых импульсов, выход четвертого счетчика подключен к входу регистра начального значения аргумента, выход которого соединен с вторым входом блока формирования кода адреса, выход третьего блока памяти подключен к второму входу сумматора, первый вход третьего блока памяти соединен с выходом сумматора, второй вход третьего блока памяти объединен с входом регистра начального значения аргумента и подключен к выходу четвертого счетчика.

Источники информации, принятые во внимание при экспертизе

20

N

Ригг

2

ik25

jy

г

fV

J8

j I... j

22

Uf

L5

jf

t:

I I I

447

Авторы

Даты

1982-08-30—Публикация

1980-06-05—Подача