каждого сумматора подключен к его второму информационному входу, выход схемы сравнения является эна(Ковым выходом блока адресации и подключен к управляющим входам второго и третьего сумматоров, выход вычитателя подключен к входу дешифратора, выход которого является адресным выходом блока адресации .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования Фурье | 1984 |

|

SU1195358A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Многофункциональный анализатор случайных процессов | 1986 |

|

SU1399766A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2006 |

|

RU2309430C1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Способ тактовой синхронизации и регенерации телеграфных сигналов и устройство для его осуществления | 1991 |

|

SU1830188A3 |

| Способ анализа спектра сигналов и устройство для его осуществления | 1988 |

|

SU1573432A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| Устройство для измерения серии временных интервалов | 1986 |

|

SU1465870A1 |

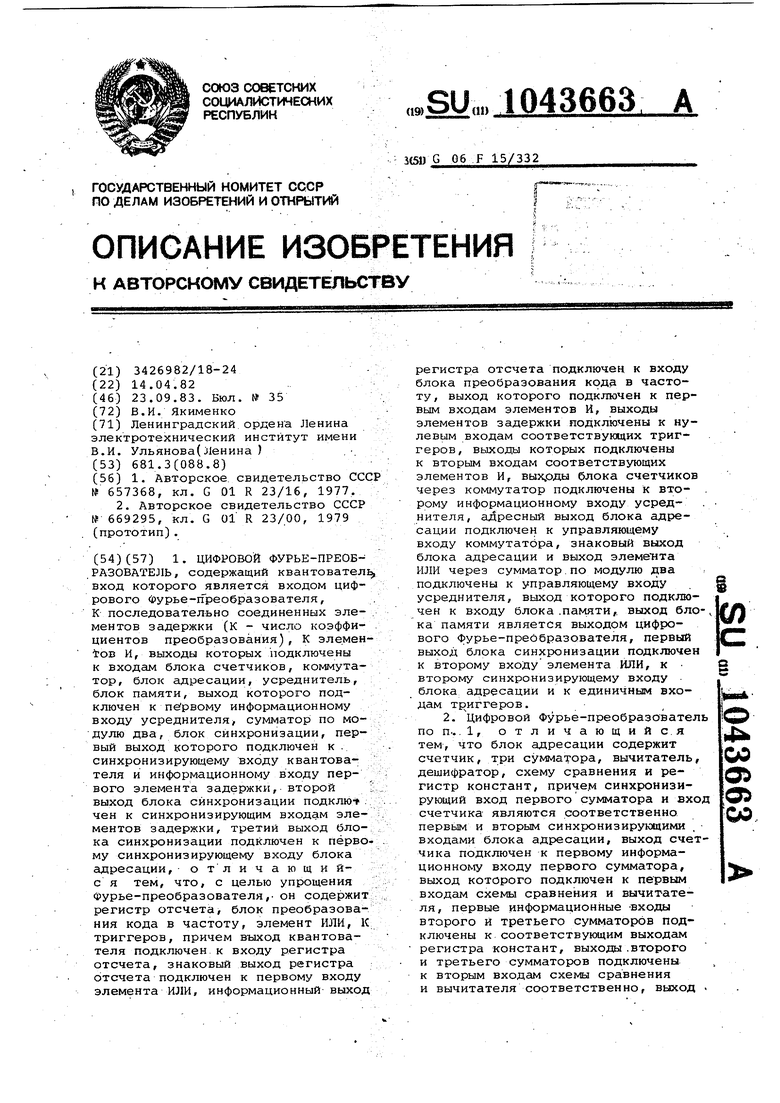

1. ЦИФРОВОЙ ФУРЬЕ-ПРЕОБРАЗОВАТЕЛЬ, содержащий квантовател вход которого является входом цифрового Фурье-гГреобразователя, К последовательно соединенных элементов задержки (К - число коэффи- . циентов преобразования), К элементов И, выходы которых подключены к входам блока счетчиков, коммутатор, блок адресации, усреднитель, блок памяти, выход которого подключен к первому информационному входу усреднителя, сумматор по модулю два, блок синхронизации, первый выход которого подключен к . синхронизирующему входу квантователя и информационному входу первого элемента задеэржки, второй выход блока синхронизации подклю- чен к синхронизирующим входам элементов задержки, третий выход блока синхронизации подключен к пёрво- . му синхронизирующему входу блока адресации, отличающийс я тем, что, с целью упрощения Фурье-преобразователя,- он содержит регистр отсчета, блок преобразования кода в частоту, элемент ИЛИ, К триггеров, причем выход квантователя подключен к входу регистра отсчета, знаковый выход регистра отсчета подключен к первому входу элемента ИЛИ, информационный выход регистра отсчета подключен к входу блока преобразования кодэ в частоту, выход которого подключен к первым входам элементов И, выходы элементов задержки подключены к нулевым входам соответствующих триггеров, выходы которых подключены к вторым входам соответствующих элементов И, выхрды блока счетчиков через коммутатор подключены к второму информационному входу усред- . Нителя, аЛресный выход блока адресации подключен к управляющему входу коммутатора, знаковый выход блока адресации и выход элемента ИЛИ через сумматор.по модулю два подключены к управляющему входу усреднителя, выход которого подклюсл чен к входу блока .памяти,, выход бло-, ка памяти является выходом цифрос вого Фурье-преобразователя, первый выход блока синхронизации подключен а к второму входу элемента ИЛИ, к второму синхронизирующему входу блока адресации и к единичнь м входам тр иггеров. 2. Цифровой Фурье-преобразователь поп.. .1, отличающийс.я 4; ОО тем, что блок адресации содержит счетчик, три сумматора, вычитатель, дешифратор, схему сравнения и реда да оо гистр констант, приче.м синхронизирующий вход первого сумматора и вход счетчика являются соответственно первым и вторым синхронизирующими , входами блока адресации, выход счетчика подключен к первому информационному входу первого сумматора, выход которого подключен к первым входсьм схемы сравнения и вычитателя, первые информационные -входа) второго и третьего сумматоров подключены к соответствукицим выходам регистра констант, выходы .второго и третьего сумматоров подключены к вторым входам схемы сравнения и вычитателя соответственно, выход

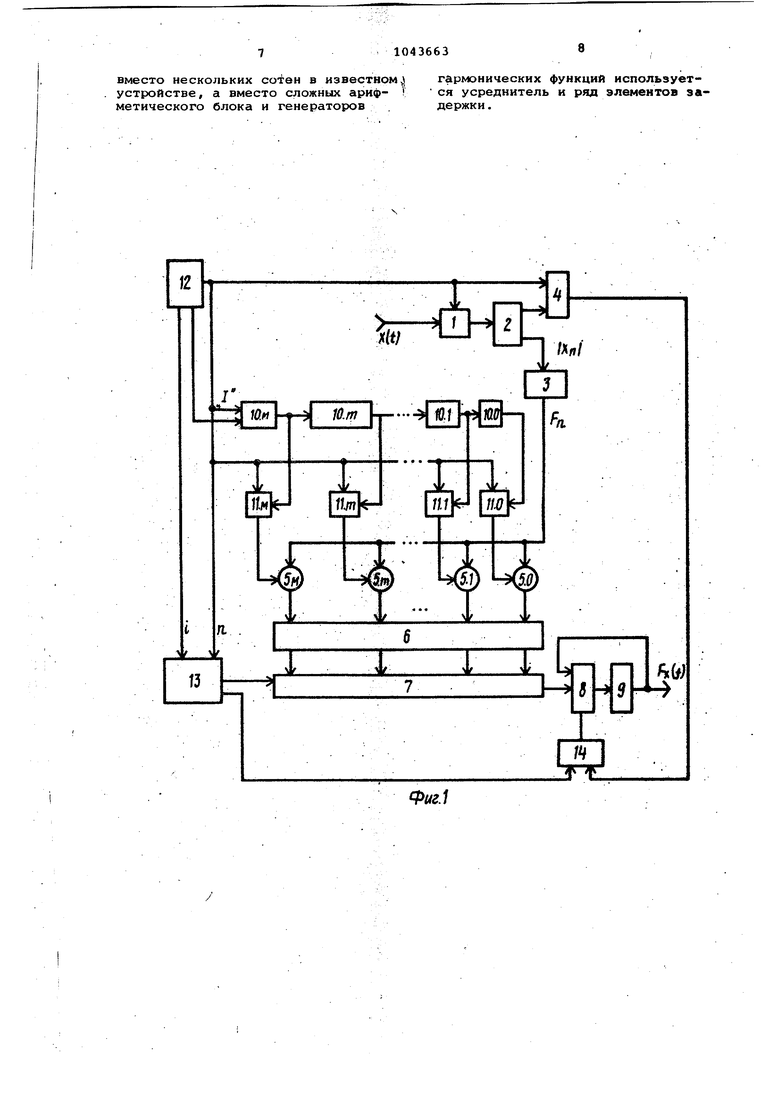

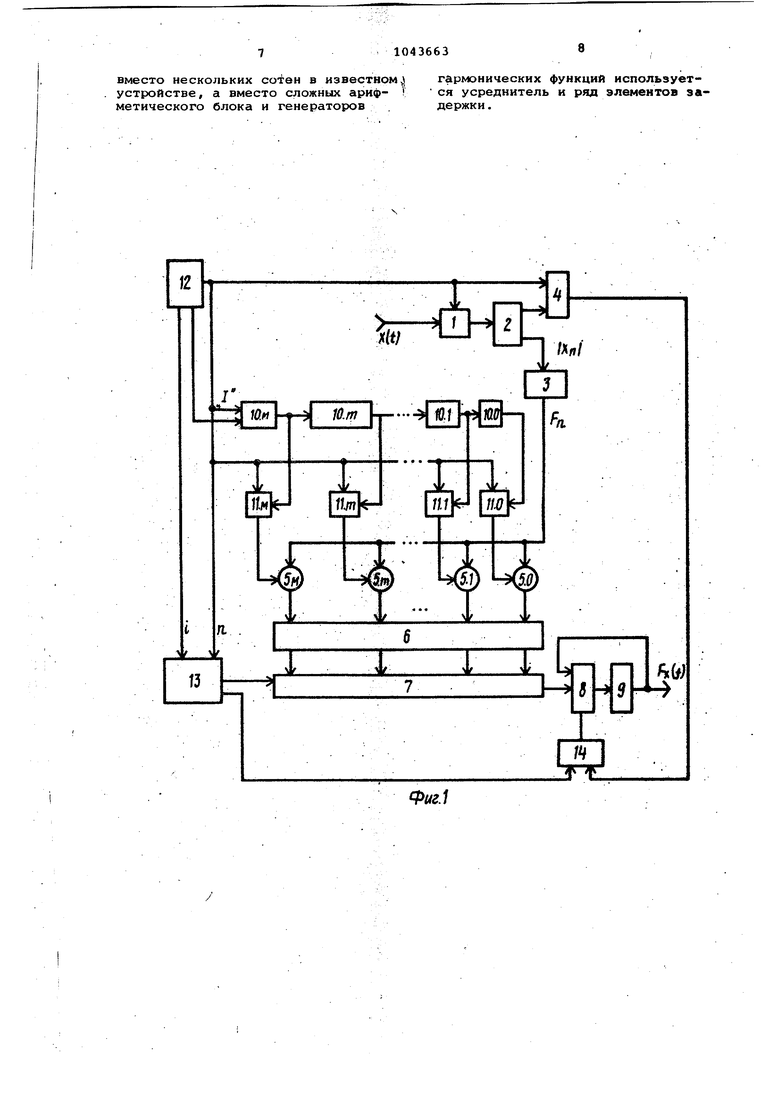

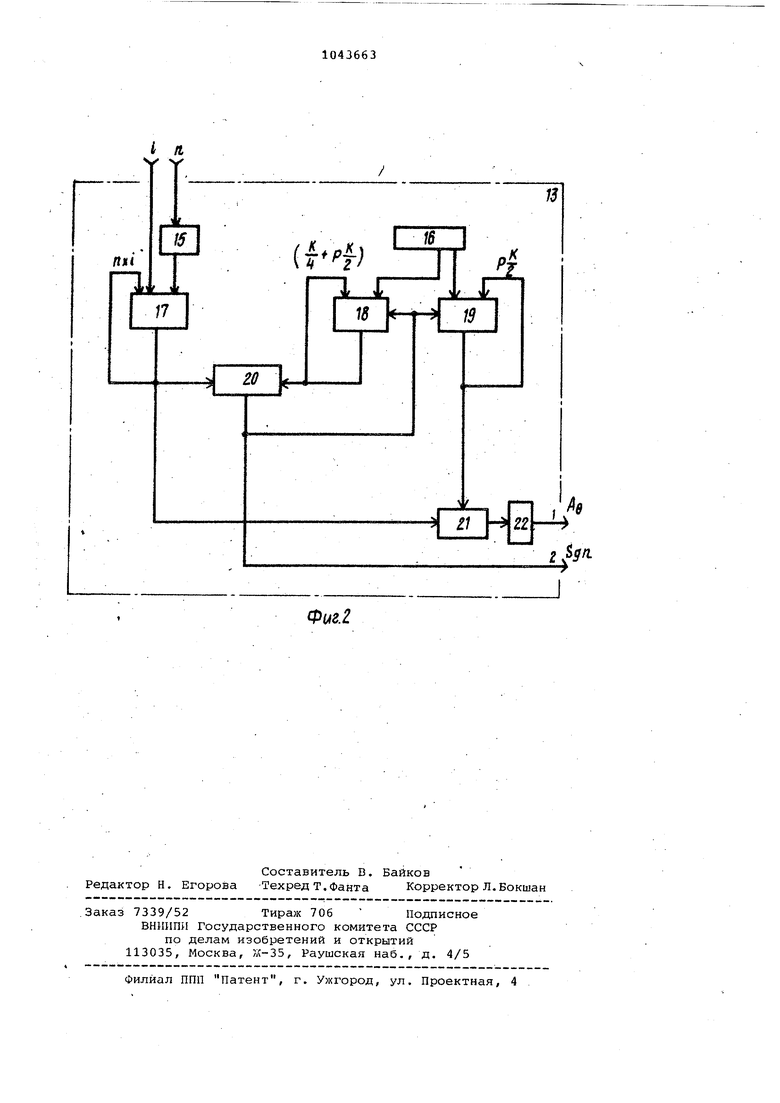

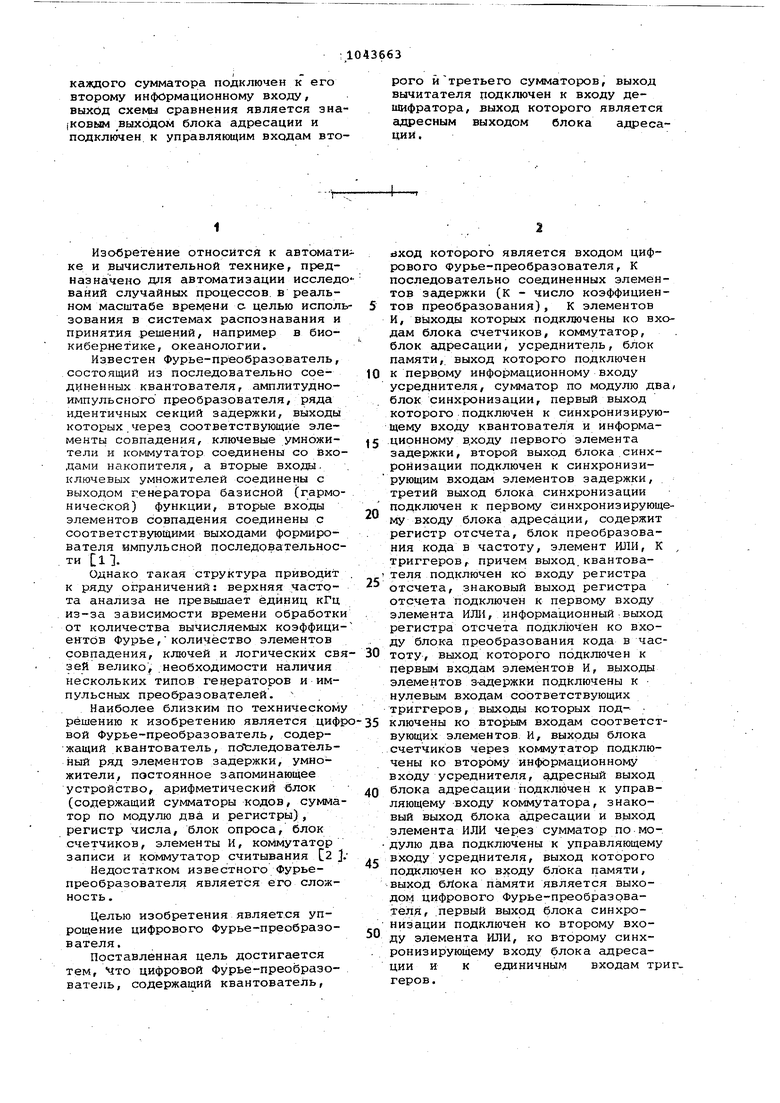

Изобретение относится к автомат ке и вычислительной технике, предназначено для автоматизации исслед ваний случайных процессов, в реальном масштабе времени с целью испол зования в системах распознавания и принятия решений, например в биокибернетике, океанологии. Известен Фурье-преобразователь, состоящий из последовательно соединенных квантователя, амплитудноимпульсного преобразователя, ряда идентичных секций задержки, выходы которых .через, соответствующие элементы совпадения, ключевые умножители и коммутатор соединены со вхо дами накопителя, а вторые входы. ключевых умножителей соединены с выходом генератора базисной (гармо нической) функции, вторые входы элементов совпадения соединены с соответствующими выходами формирователя импульсной последовательнос ти 11. Однако такая структура приводит к ряду ограничений: верхняя часто та анализа не превышает единиц кГц из-за зависимости времени обработк от количества вычисляемых коэффици ентов Фурье,количество элементов совпадения, ключей и логических св зей велико, .необходимости наличия нескольких типов генераторов и импульсных преобразователей. Наиболее близким по техническом решению к изобретению является циф вой Фурье-преобразователь, содержащий квантователь, пойледовательный ряд элементов задержки, умножители, постоянное запоминающее устройство, арифметический блок (содержащий сумматоры кодов, сумма тор по модулю два и регистры), регистр числа, блок опроса, блОк счетчиков, элементы И, коммутатор записи и коммутатор считывания 2 J Недостатком известного Фурьепреобразователя является его сложность. Целью изобретения является упрощение цифрового Фурье-преобразователя. Поставленная цель достигается тем, Что цифровой Фурье-преобразователь, содержащий квантователь. ., 2 вход которого является входом цифрового Фурье-преобразователя, К последовательно соединенных элементов задержки (К - число коэффициентов преобразования), К элементов И, вь1хоДы которых подключены ко входам блока счетчиков, коммутатор, блок адресации, усреднитель, блок памяти,; выход которого подключен к первому информационному входу усреднителя, сумматор по модулю два/ блок синхронизации, первый выход которого подключен к синхронизирующему входу квантователя и информационному входу первого элемента задержки, второй выход блока синхронизации подключен к синхронизирующим входам элементов задержки, третий выход блока синхронизации подключен к первому синхронизирующему входу блока адресации, содержит регистр отсчета, блок преобразования кода в частоту, элемент ИЛИ, К , триггеров, причем выход, квантователя подключен ко входу регистра отсчета, знаковый выход регистра отсчета подключен к первому входу элемента ИЛИ, информационный-выход регистра отсчета подключен ко вхо ду блока преобразования кода в частоту, выход которого подключен к первым входам элементов И, выходы элементов з-адержки подключены к нулевым входам соответствующих триггеров, выходы которых под- ключены ко вторым входам соответствующих элементов и, выходы блока счетчиков через коммутатор подключены ко второму информационному ВХОДУ усреднителя, адресный выход блока адресации подклзочен к управляющему входу коммутатора, знаковый выход блока адресации и выход элемента ИЛИ через сумматор по модулю два подключены к управляющему входу усреднителя, выход которого подключен ко входу блока памяти, выход бЛока памяти является выходом цифрового Фурье-преобразователя, .первый выход блока синхронизации подключен ко второму входу элемента ИЛИ, ко второму синхронизирующему входу блока адресации и к единичным входам триггеров. Кроме того, блок адресации со держит счетчик, три сумматора,вычитатель, дешифратор, схему сравне ния и регистр констант, причем синхронизирующий вход первого сумматора и вход счетчика являются соответственно первым и вторым синхронизирующими входами блока, адресации, выход счетчика подключен к первому информационному входу первого сумматора, выход которого подключен к первым входам схемы сравнения и вычитателя, первые информационные входы второго и третьего сумматоров подключены к соответствующим выходам регистра констант, выходы второго и третьего сумматоров подключены ко вторым входам схемы сравнения и вычитателя соответственно, выход каждого сумматора подключен к его второму информационному входу, вы ход схемы сравнения является знако вым выходом блока адресации и под ключен к управляющим входам второ го и третьего сумматоров, выход вычитателя подключен ко входу дешифратора, выход которого является адресным выходом блока адресаци .На фиг. 1 представлена функцио нальная схема цифрового Фурье-пре образователя; на фиг. 2 - функцио нальная схема блока.адресации. Цифровой Фурье-преобразователь содержит квантователь 1, регистр 2 отсчета, блок 3 преобразования кода в частоту, элемент ИЛИ 4, элемент и 5, блок 6 счетчиков, коммутатор 7, усреднитель 8, блок памяти, элементы 10 задержки, . триггеры 11, блок 12 синхронизации, блок 13 адресации и сумматор 14 по модулю два. Блок адрес.ации состоит из счет чика-15, регистра 16 констант, сумматоров 17-19, схемы 20 сравне ния, вычитателя 21 и дешифратора 2 .Цифровой Фурье-преобразователь работает следующим образом. Исследуемый случайный сигнал X(t) подается на вход квантователя 1 и тактовыми п импульсами с. выхода блока 12 синхронизации преобразуется в дискретную форму Х(п- at). При получении первого отсчета Х(1 .flt) в регистре 2 фиксируется знак отсчета Sp-rt(X) и модуль I X I: знаковый импульс через элемент ИЛИ 4 подается на вход сумматора 14 по модулю два, задавая знак второго слагаемого в усреднителе 8.: У i ,+ {- 1 ) .i-i блоке 3 кед I Х-, I преобраз ся в поток импульсов соответствую щей частоты Р , которые поступают на первые входы ряда элементов И 5.0-5.М. Одновременно этот же ( , пульс с выхода блока 12 синхронизации поступает на вход первого .элемента 10 задержки, а также устанавливает одновременно все триггеры 11 в начальное состояние, при котором первые входы элементов И 5 открываются для прохождения потока импульсов F на входы блока 6 счетчиков. При этом поступающие со второго выхода блока 12 синхронизации на jmравляющий вход секций задержки 10 тактирующие импульсы продвигают одиночный импульс (п.1) по цепочке элементов задержки, в результате чего этот импульс поочередно поступает с выхода элементов задержки 10.м - lO.(M-l) - ... - 10.1 - 10.0, переводя поочередно соответствую1Дие триггеры 11.М - ll.(M-l) ... - 11.1 - 11.0 в нулевое состояние, вследствие чего поочередно запрещается прохождение потока импульсов F-( через элементы И 5 на входы соответствующих счетчиков блока 6. Задержка сигнала в i-ом элементе задержки пропорциональна значению i-ro отсчета базисной функции на четверти периода ее измене Бак как частота импульсов Ь пропорциональна амплитуде Х, то в какдом из i счетчиков сформируется код б-1.,-/1ропорциональныи произведении отсчета Xf-l-ut). на один из -коэффициеитов четверти периода базисной Сев -функции: г41г|, ,(). e.X{ --iltlcos2J7 т где К количество коэффициентов Фурье,ДТ - шаг отсчетов Cos-функции; /Зр - масштабный коэффициент . После этого по тактовым командам с третьего выхода блока 12 синхронизации в блоке 13 адресации начинается формирование номеров адресов для сч-итывания ряда К-кодов произведений в. из блока 6 счетчиков: через первый вход усреднителя 8 ряд кодов поступает- в соответствующие ячейки(1,2,3..,К/4) блока 9 памяти, (так как перед первым циклом в блоке 9 памяти не было на- коплено информации, то на второй вход усреднителя 8 коды пока не поступают).После считывания кода с последнего из К/4 счетчиков блока 6 из блока 13 адресации на вход су1иматора 14 по модулю два поступает, импульс и изменяет состояние е.го знакозадающего выхода для управления режимом усреднения усреднителя 8: ряд кодов теперь поступает в обратном порядке (xjf )-) 2, i)

И усредняется с отрицательным знаком (в соответствии со знаком СсБ-функции на второй четверти периода), Tie..: .

rrV-.- - Работа блока 13 в каждом г.-ом цикле обработки производится аналогичным образом.

От блока 12 синхронизации п-й импульс одновременно подается на Управляющий вход квантователя 1 и На вход блока 13 опроса: счетчик 1 Производит счет этих тактовых импульсов, причем номер импульса п .задает шаг спроса последовательности счетчиков в блоке 6. Этот ко шага п с выхода счетчика 15 подается на второй вход накапливающего сумматора 17 и при каждой i-ой микрокоманде сложение в нем осуществляется суммирование кода п с предыдущим кодом n(i-1), накопленым в сумматоре 17. Новая АЙ ()) п1 с выхода сумматора 17 подается на первый вход схемы 20 сравнения.

Одновременно с этими прео.бразованиями ко второму входу схемы 20 сравнения подключен код числа К/4, считываемый предварительно из регистра 16 в накапливающий сумматор 18. При каждом i-ом командном импульсе в Схеме 20 сравнения проверяется выполнение соотношения

0 - тПри нарушении этого соотношения схема 20 сравнения вырабатывает импульс, являющийся микрокомандой Изменение знака для сумматора 14 по модулю два, на выходе которого появляется потенциал, -соответствующий, например, знаку отрицательного полупериода Cos -функции на входе усреднителя 8. Этот импульс являет ся также микрокомандой Сложение для сумматоров 18 и 19, в которых крды суммируются с предыдущими кодами, считанными с соответствующих выходов регистра 16 (соответственно код К/4 и код К/2). В результате этого на выходе вычитателя 21 сформируется- код адреса опроса

4/1 71,С,1,...,К-,

а схема 20 сравнения задает закон изменения знаков в усреднителе 8 через сумматор 14 по модулю два: в усреднителе 8 будут изменяться знаки, сос тветствующие номеру опрашивгхемрго счетчика в блоке 6 по следующему соотношению:

предыдущий знак: при

{предыдущий знак: Jnu.( измененный знак:

(p1)

21

Дешифратор 22 преобразует код Ад в соответствующий импульс опроса определенного счетчика в блоке 6, т.е.,

че.рез соответствующий ключ коммутатора 7 производится считывание кода из счетчика с соответствующим номером и подача его на вход усреднителя 8.

После микрокоманд во всех К ячейках блока 9 памяти будет накоплен результат обработки в п-ом цикле, после чего блоки Фурье-преобразователя подготовлены для осуществления преобразований (.)-го цикла.

Так, при втором цикле (п 2} преобразования осуществляются следующим образом.

По п 2 импульсу от блока 12 синхронизациии в квантователе 1 формируется отсчет X (2 at) входного сигнала, который поступает в регистр 2. Выделенный знак этого

отсчета поступает через элемент ИЛИ 4 на вход начальной установки знака в сумматоре 14 по модулю два (т.е. операции Сложение или Вычитание в усреднителе 8 припервых к/4 тактах усреднения). В блоке 3 преобразования формируются импульсы частоты F пропорциональной амплитуде X (2 At), которые поступают через э.лементы И 5 на вя:о;ды блока 6 счетчиков.

После сдвига одиночного импульса п на выход элемента задержки 10.О прекращается формирование произведений Начинается их считывание в усреднитель 8 при помощи блока 13 адресации, аналогично описанной последовательности, но с шагом опроса Л1 , т.е. опрашивая счетчики в блоке 6 с номерами i 0,2,4..-., а после усреднения результат, как и в любом цикле, записывается в последовательность ячеек Е 1,2,3... до к-ой в блоке 9 памяти.

После К-го цикла обработки входнего сигнала в блоке 9 памяти накапливается сумма, описываемая

следующим выражением: 4п

F (Б л) (- ©„X

,

xcTCf- ),

где р - .номер полупериода базисной ССБ -функции.

Предлагаемая конструкция характеризуется небольшим количеством (несколько десятков) элементов И вместо нескольких сотен в известному устройстве, а вместо сложных ариф- { метического блока и генераторов гармонических функций используется усреднитель и ряд элементов задержки.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дискретный статистический анализатор | 1976 |

|

SU657368A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Анализатор спектра | 1977 |

|

SU669295A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-09-23—Публикация

1982-04-14—Подача