(54) УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ЭКРАНЕ ТЕЛЕВИЗИОННОГО ПРИЕМНИКА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1494778A1 |

| Устройство для контроля видеосигнала | 1982 |

|

SU1069190A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1387039A1 |

| Устройство для воспроизведения изображения | 1980 |

|

SU1085014A1 |

| Устройство для воспроизведения видеосигнала | 1987 |

|

SU1555918A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1979 |

|

SU868825A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2051416C1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1469518A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1361615A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к созданию специализированных внешних устройств ЦВМ - устройств отображения информации на экране телевизионного приемника.

Известно устройство для отображения информации на экране телевизионного приемника, содержащее оперативное запоминающее устройство (ОЗУ), буферный регистр сдвига, счетчик адреса и формирователь l.

Недостатком данных устройств является -невозможность отображения информации с несколькими градациями яркости..

Наиболее близким техническим решением к предлагаемому является устройство, содержащее последовательно соединенные блок сопряжения, блок сокращения избыточности видеосигнала, блок записи, блок памяти, блок считывания, блок восстановления видеосигнала, соединеннре с синхронизатором, преобразователь код - аналог, соединенный с блоком восстановления видеосигнала и телевизионным приемником 2.

Это устройство позволяет более эффективно использовать памятБ путем записи в нее кода разности яркостей

соседних точек, которыйобразуется в блоке сокращения избыточности видеосигналов, и затем восстановления его после считывания из памяти в блоке восстановления видеосигнала.

Однако известное устройство имеет ограниченные возможности, так как не позволяет отобразить резкие изменения яркости, что приводит к размы10ванию контрастных изображений и снижает разрешающую способность при анализе изображения на экране.

Целью изобретения является повышение точности отображения информации.

15

Поставленная цель достигается тем, что устройство для отображения информации на экране телевизионного приемника, содержащее последовательно соединенные блок сопряжения и блок сок20ращения избыточности видеосигнала, соединенные с блоком синхронизации, последовательно соединенные блок записи, блок памяти и блок считывания, соединенные с блоком синхронизации,

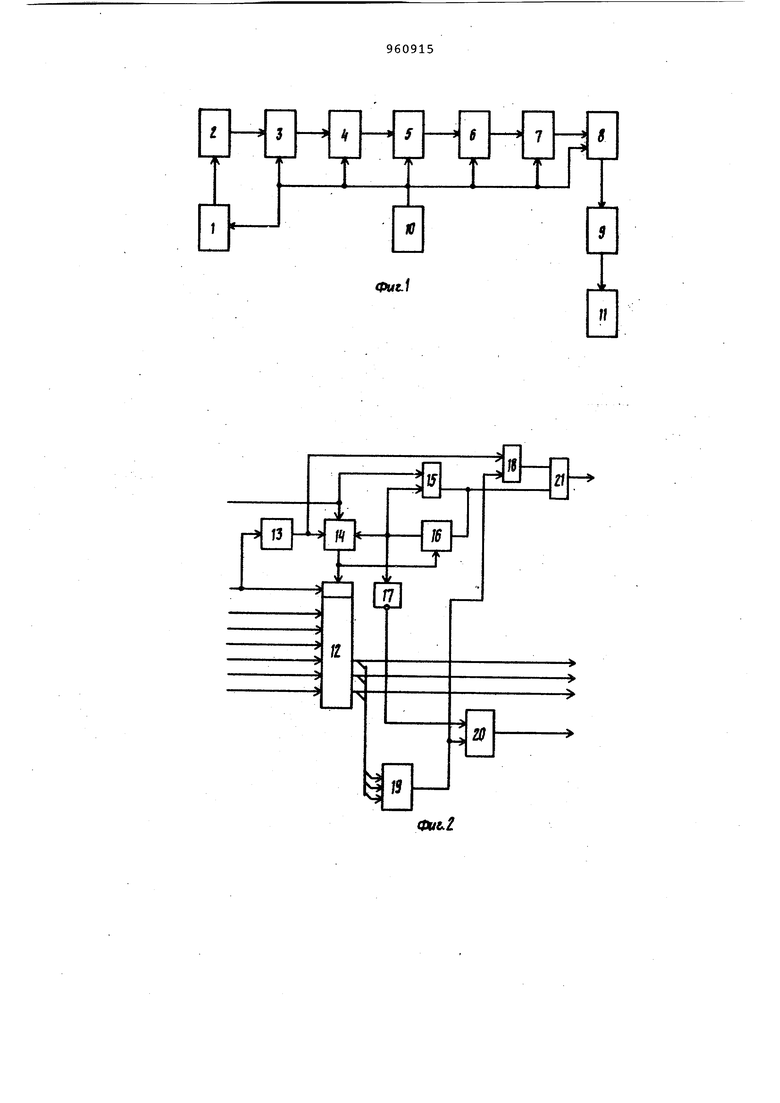

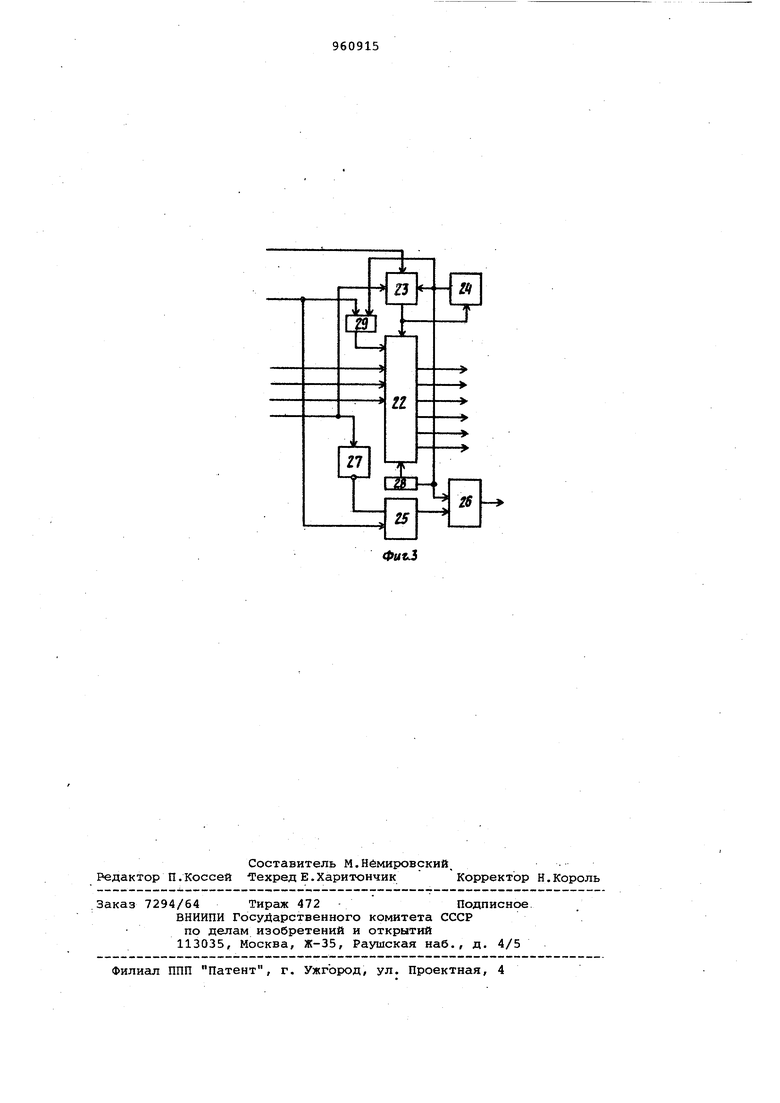

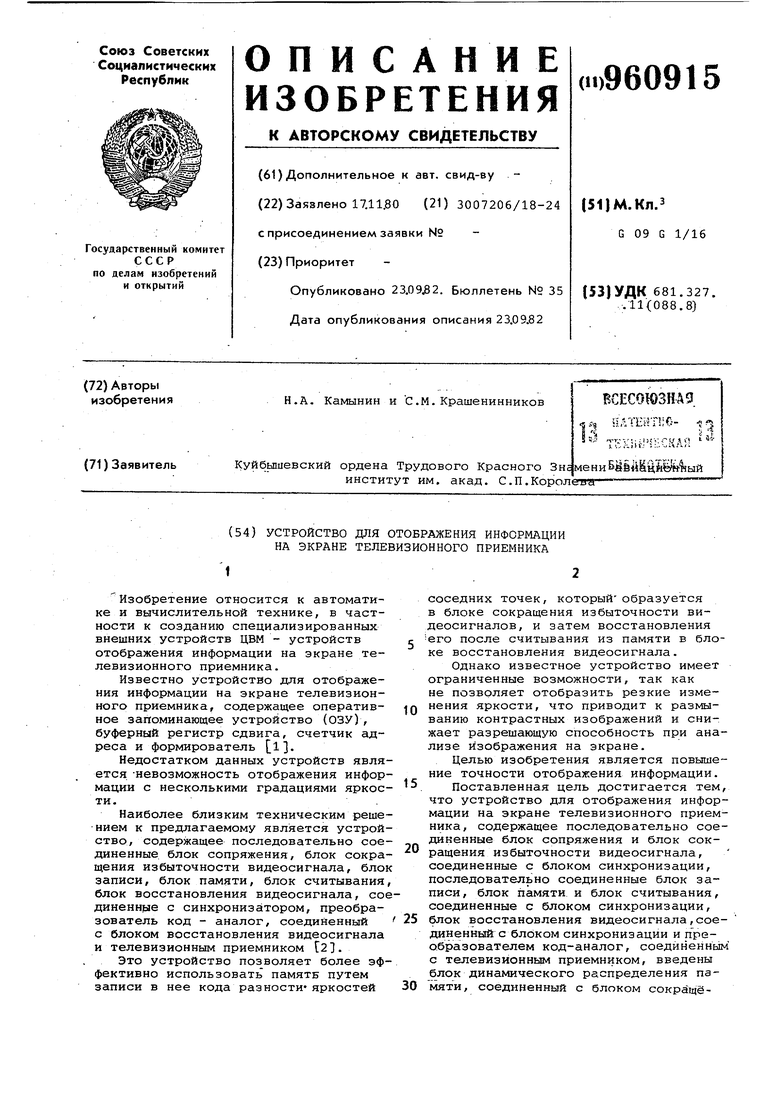

25 блок восстановления видеосигнала,соединенный с блЬк ом синхронизации и преобразователем код-аналог, соединенным с телевизионнь м приемником, введены блок динамического распределения па30мяти, соединенный с блоком сокращёния избыточности видеосигнала, блоко записи и блоком синхронизации, и блок восстановления кода соединенны с блоком считывания, блоком восстано ления видеосигнала и блоком синхрони .эации. Блок динамического распределения памяти содержит первый элемент задер ки, первый элемент запрета,- первый инвертор, первый делитель частоты, (три элемента И, два элемента ИЛИ и первый регистр сдвига, первый вход которого является первым входом блока, второй вход которого соединен с вторым входом первого регистра сдвига и входом первого элемента задержки, выход которого соединен с первым входом первого элемента запрета и пер вым входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, -выход которого является первым выходом блока, а второй вход соединен с выходом второго. элемента И и первым входом первого делителя частоты, второй вход которого соединен с третьим входом первого регистра сдвига, и выходом первого элемента запрета, второй вход которо го соединен с третьим входом блока и первым входом второго элемента И,вто рой вход которого соединен с третьим входом первого элемента запрета, с выходом первого деЛителя частоты и входом первого инвертора, выход кото рого соединен с первым входном третье -го элемента И, выход первого регистра сдвига, являющийся вторым выходом блока, соединен со входом, второго элемента ИЛИ, выход которого соединен со вторым входом первого элемент И и вторым входом третьего элемента выход которого является третьим выходом блока. Блок восстановления кода содержит вторые элементы запрета, задержки, второй Инвертор, второй делитель частоты, третий и четвертый элементы ИЛИ четвертый элемент И и второй регистр сдвига, первый вход которого является первым входом блока, а второй вход соединен с выходом третьего элемента ИЛИ, первый вход Которого соединен с первым входом четвертого элемента И и является вторым входом блока,третий вход которого соединен с первым входЬм второго элемента запрета, второй хрд которого соединен с вторым Входом третьего элемента ИЛИ и выходом второго делителя частоты, вход которого соединен с выходом второго элемента запрета и третьим входом второго регистра сдвига, выход которого является первым выходом блока, а четвертый вход соединен с выходом второго элемента задержки, вход которого соединен с выходом второго делителя частоты и с первым входом четвертого элемента ИЛИ, выход которого является вторым выходом блока, а второй вход.соединен с выходом четвертого элемента И, второй вход которого соединен с выходом второго инвертора, вход которого соединен с третьим .входом второго элемента запрета и является входом блока. На фиг. 1 представлена блок-схема устройства для отображения информации на экране телевизионного приемника/ на фиг. 2 - блок динамического распределения памяти; на фиг.З блок восстановления кода. Устройство для отображения информации на экране телевизионного приемника содержит блок 1 сопряжения , блох 2 сокращения избыточности, блок 3 динамического распределения памяти, блок 4 записи, блок 5 памяти,блок 6 считывания, блок 7 восстановления рода, блок 8 восстановления видеосигнала-, преобразователь 9 код - аналог, блок 10 синхронизации и телевизионный приемник 11. Блок динамического распределения памяти содержит первый регистр 12 сдвига, первый элемент 13 задержки, первый элемент 14 запрета, второй элемент И 15,первый делитель 16 частоты, первый инвертор 17, первый элемент И 18, второй элемент ИЛИ 19, третий элемент И 20, первый элемент ИЛИ 21. Блок восстановления кода содержит второй регистр 22 сдвига, второй элемент 23 запрета, второй делитель 24 частоты, четвертый элемент И 25, четвертый элемент ИЛИ 26, второй инвертор 27, второй элемент 28 задержки, третий элемент ИЛИ 29. Цифровая информация с ЦВМ через блок 1 сопряжения поступает на вход блока сокра.щения избыточности, в котором осуществляется преобразование видеосигнала таким образом, что абсолютный уровень:сигнала яркости преобразуется в разность между соседними значениями этого сигнала,причем эта разность передаетсяв коде, имеющем столько же разрядов, сколько их было в коде исходного видеосигнала N. С выхода блока 2 сокращение избыточности информации поступает на блок 3 динамического распределения памяти, где происходит преобразование кода таким образом, что он- представляется в виде п -разрядных слов, где п -и разряд является служебным и показывает, ;является ли данное слово самостоятельным или продолжением предыдущего. С выхода .Яблока 3 динамического распределения памяти п -разрядный код поступает через блок 4 за-писи в блок 5 памяти. При воспроизведении информация списывается с блока 5 памяти блоком 6 считывания и поступает в блок 7 восстановления кода,,где п -разряд- . ные слова преобразуются в М -разрядный код, который затем поступает в блок 8 восстановления видеосигнала/ где происходит восстановление исходного видеосигнала. Синхронизация все этих блоков осуществляется синхросиг налами, которые поступают на :них из блока 10 синхронизации. С выхода,бло ка 8 восстановления видеосигнала цифровой видеосигнал поступает в пре образователь 9 код - аналог, в котором формируется аналоговый видеосигнал, который поступает на вход телевизионного приемника. Блок 3 динамического распределения памяти работает следующим образом. : Информация с выхода блока сокращения избыточности в виде N-разрядного параллельного кода (в данном случае N 6) поступает на информационные входы регистра 12 сдвига. Одновременно с синхронизатора навход Запись регистра 12 сдвига и вход элемента 13 задержки поступают импульсы с частотой Р, а на вход элемента 14 запрета и первый вход первого элемента И 15 - импульсы ча то той 5 FT синхронизирующая частота остальных блоков устрой ства. Импульс частотой F, поступая 1на вход Запись регистра 12 сдвига записывает в него информацию. При этом значения п -1 старших разрядо JC :выходов регистра 1 сдвига подаются на входы второго элемента ИЛИ 19. Если хотя бы в одном из ti-l стар ших разрядов окажется сигнал логической единицы, то он пройдет на выход второго элемента ИЛИ 19 и с выхода инвертора 17 третьего элемента И 20 поступит на п-и вход блока записи, на остальные п-1 входов которого поступают сигналы с выходов регистра 1 сдвига. Кроме того, сигнал логической еди ницы с выхода второго элемента ИЛИ 19 открывает второй элемент И 15 ;и, задержанный на элементе 13 задерж ки, импульс частоты FT через открытый второй элемент И 15 и первый элемент ИЛИ 21 проходит на управляющий вход блока записи. Кроме того, импульс с выхода элемента 13 задержки открывает элемент 14 запрета, через который импульсы с частотой 5 F поступают на сдвиговый вход регистра 12 сдвига и сдвигают информацию из младших разрядов в старшие. Пропусти три импульса, элемент 14 запрета зак рывается сигналом с выхода делителя 16 частоты. Этот же сигнал закрывает третий элемент И 20 и открывает второй элемент И 15. Три импульса, пришедшие на сдвиговый вход регистра 12 сдвига, сдвигают п-1 младших разрядов на место п-1 старших. Четвертый импульс частоты 5 FT через открытый первый элемент И 18 и первый элемент ИЛИ 21 проходит на вход блока записи как импульс Запись. Происходит считывание, информации с выхода регистра 12 сдвига и значения логического нуля с выхода третьего элемента И 20. Этот же импульс устанавливает делитель 16 частоты в О, второй элемент И 15 закрывается. Цикл овонче н. Если на п -1 ,старших разрядах регистра 12 сдвига не окажется ни одной логической единицы, то первый 18 и третий элементы 20 И будут закрыты и считывания сигнала О не произойдет. Очередной импульс частоты FT через элемент 13 задержки открывает элемент запрета 14 и устройство переходит в исходное состояние. Блок 7 восстановления кода (фиг. 3) работает следующим образом. С выхода блока считывания на информационные входы регистра 22 сдви.га подается п -разрядное слово. Од- новременно на вход Запись регистра 22 сдвига через третий элемент ИЛИ 29 и первый вход четвертого элемента И 25 из блока синхронизации подаются синхроимпульсы с частотой F.. На вход элемента 23 запрета с синхронизатора подаются синхроимпульсы с частотой 5 F. Импульс, поступивший на вход Запись регистра 22 сдвига, записывает в его п-1 младших разрядов п -1 разрядное слово. Бели в старшем п -ном разряде окажется сигнал логического нуля, то он через инвертор 27 откроет элемент И 25, и импульс частоты Fy через открытый элемент И 25 и элемент ИЛИ 26 пройдет на вход блока восстановления Видеосигнала. Этот импульс перепишет информацию с выхода регистра 1 сдвига в блок восстановления видеосигнала. Если в п-ном старшем разряде п-разрядного слова будет записана логическая единица, то сигнал через инвертор 27 закроет элемент и 25 и откроет элемент 23 запрета, через который на сдвиговый вход регистра 12 сдвига пройдет три импульса частоты 5 F. Эти импульсы сдвинут информацию из п -1 младших разрядов в п-1 старших. Элемент запрета закрывается импульсом с выхода делителя 24 частоты. Этот же импульс через элемент ИЛИ 29 проходит на вход Запись регистра 12 сдвига и записывает информацию в h-1 младших разрядов, через элемент 26 ИЛИ проходит как импульс Запись на вход блока восстановления и через элемент 28 задержки устанавливает в О выходные сигналы на всех шинах регистра 22 сдвига. Таким образом, происходит преобразование п -разрядного кода в N -разядный. С приходом следующего импульса частоты FT цикл работы повторяется . Таким образом, введение блока ди-. намического распределения памяти и блока восстановления кода позволяет точно отображать контрастные изображения при эффективном использовании объема оперативной памяти устройства. Это существенно расширяет сферу применения предложенного- устройства. Формула изобретения 1.Устройство для отображения информации на экране телевизионного приемника, содержащее последовательно соединенные блок сопряжения и блок избыточности видеосигнала, соединенные с блоком синхронизации, последовательно соединенные блок записи, блок памяти и блок считывания, соединенные с блоком синхронизации, блок восстановления видеосигнала, соединенный с блоком синхронизации и преобразователем код-аналог, соединенным с телевизионным приемником, отличающее С я тем, что, с целью повышения точности отображения информации, оно содержит блок динамического распределения памяти, соединенный с блоком сокращения избыточ ности видеосигнала, блоком, записи и блоком синхронизации, и блрк восстановления кода, соединенный с блоком считывания, блоком восстановления ви деосигнала и блоком синхронизации. 2.Устройство по п. 1, о т л и чающееся тем, что блок динамического распределения памяти содержит первый элемент задержки, первый элемент запрета, первый инвертор первый делитель частоты, три элемента И, два элемента ИЛИ и первый регистр сдвига, первый вход которого является первым входом блока, второй вход которого соединен с вторым входом первого регистра сдвига и входом первого элемента задержки, выход которого соединен с первЕлм входом первого элемента запрета и первым входом первого элемента И, выход которого соединен с первым входом первото элемента ИЛИ,1 выход которого явля етсщ первым выходом блока, а второй вхо4 соединен с выходом второго элемента И и первым входом первого дели теля частоты, второй вход которого соединен с третьим входом первого регистра сдвига и выходом первого элемента запрета, второй вход которого соединен с третьим входом блока и первым входом второго элемента И, второй вход которого соединен с третьим входом первого элемента запрета, с выходом первого делителя частоте и входом первого инвертора, выход которого соединён с первым входом третьего элемента И, выход первого регистра сдвига, который является вторым выходом блока, соединен со входом второго элемента ИЛИ,- выход которого соединен со вторым входом первого элемента И и вторым входом третьего элемента И, выход которого является третьим выходом блока. 3. Устройство по п. 1,отличающееся тем, что.блок восстановления кода содержит вторые элементы запрета, задержки, второй инвертор, второй делитель частоты,третий и четвертый элементы ИЛИ, четвертый элемент И и второй регистр сдвига, первый вход которого является первым входом блока, а второй вход соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с первым входом четвертого элемента И и является вторым входом блока, третий вход которого соединен с первым входом второго элемента запрета, второй вход которого соединен с вторым входом третьего элемента ИЛИ и выходом второго делителя частоты, вход которого соединен с выходом второго элемента запрета и третьим входом второго регистра сдвига, выход которого является первым выходом блока, а четвертый вход соединен с выходом второго элемента задержки, вход которого соединен с выходом второго делителя частоты и с первым входом четвертого элемента ИЛИ, выход которого является вторым выходом блока, а второй вход соединен с выходом четвертого элемента И, второй вход которого соединен с выходом второго инвертора, вход которого соединен с третьим входом второго элемента запрета и -является четвертым входом блока. Источники информации, принятые во внимание при экспертизе 1.Телевизионные методы и устройства отображения информации.Под.ред. Кривсядеева М.И.;м. , Советское радио, 1975. 2.Авторское свидетельство СССР 633043, кл. G 06 К 15./20, 1978 (прототип).

Авторы

Даты

1982-09-23—Публикация

1980-11-17—Подача