(5) ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный мультивибратор | 1979 |

|

SU809499A1 |

| Формирователь импульсов | 1979 |

|

SU809353A1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| Реле времени периодических включений | 1980 |

|

SU868871A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU826565A1 |

| Двухтактный сдвигающий регистр | 1968 |

|

SU736172A1 |

| Импульсный стабилизатор напряжения постоянного тока | 1981 |

|

SU983679A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Формирователь импульсов | 1984 |

|

SU1401574A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1994 |

|

RU2114500C1 |

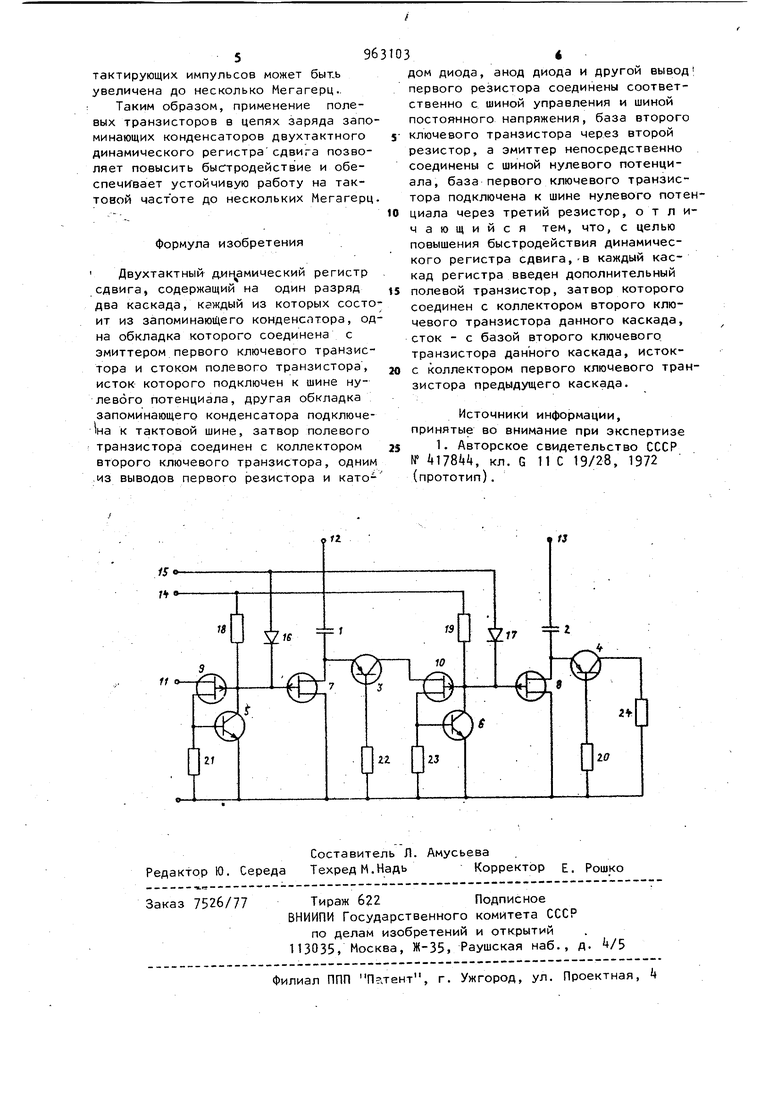

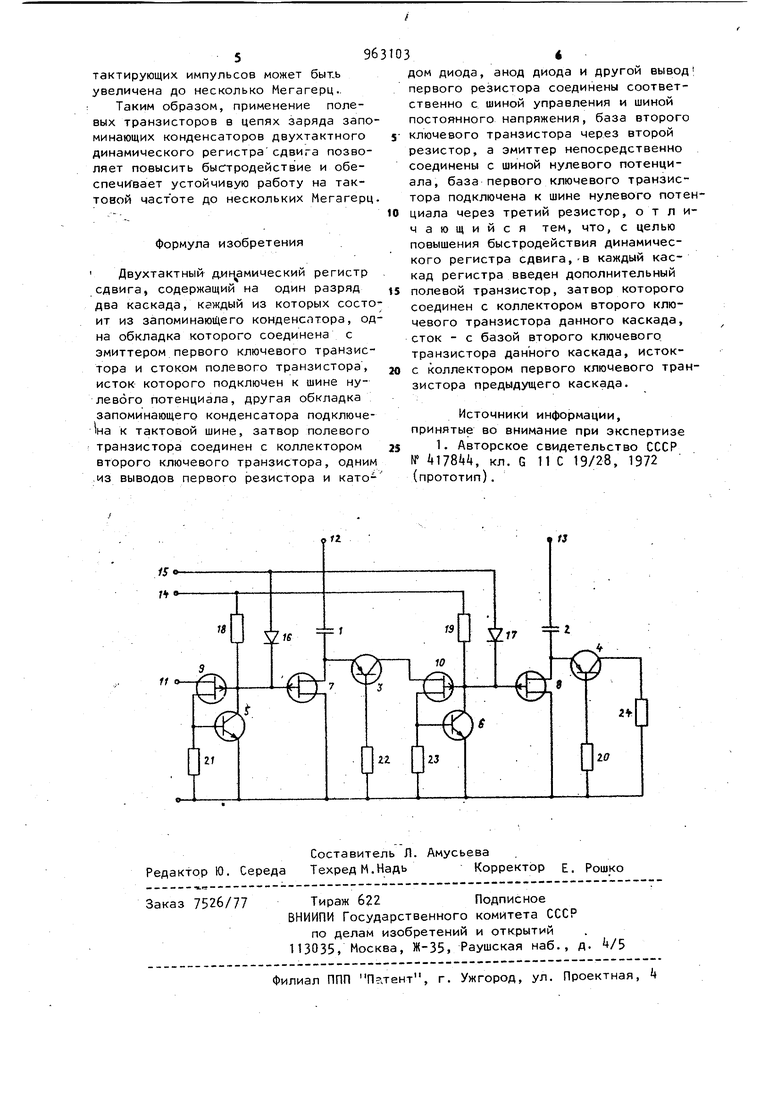

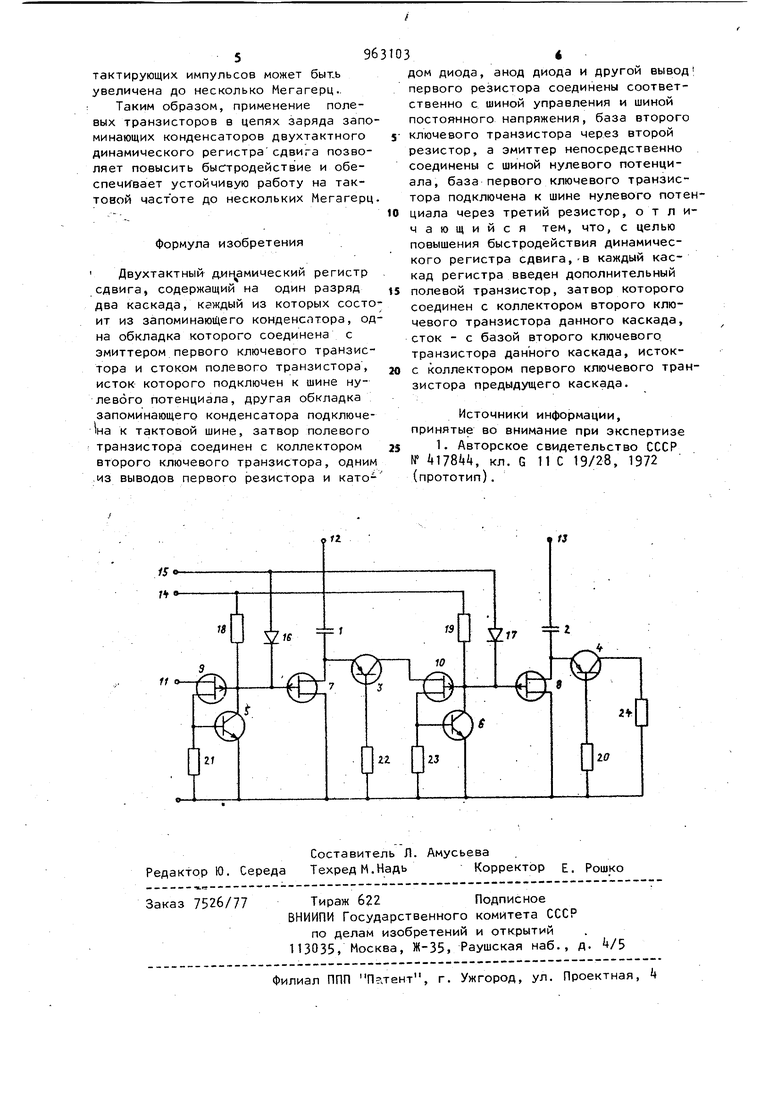

Изобретение относится к импуль1СНОЙ теЛ1ике и может быть использовано в радиоэлектронных устройствах систем автоматического управления, для построения функциональных узлов вычислительных устройств. Известен регистр сдвига, содержащий запоминающие конденсаторы, транзисторы п-р-п типа, резисторы, источник положительного постоян ного напряжения, диоды, источник им пульсов управления, источник тактового питания, источник входного сиг нала, транзисторы р-п-р типа, полевые транзисторы, выходную нагрузку r Одним из основных недостатков да ного устройства является низкое быс родействие. Цель изобретения - повышение быс родействия динамического регистра сдвига. Поставленная цель достигается тем, что в двухтактный динамический регистр сдвига, содержащий на ОДИН разряд два каскада, каждый из которых состоит из запоминающего конденсатора, одна обкладка которого соединена с эмиттером первого ключевого транзистора и стоком полевого транзистора, исток которого подключен к шине нулевого потенциала, другая обкладка запоминающего конденсатора подключена к тактовой шине, затвор полевого транзистора соединен с коллектором второго ключевого транзистора, одним из выводов первого резистора и катодом диода, анод диода и другой вывод первого резистора соединены соответственно с шиной управления и шиной постоянного напряжения, база второго ключевого транзистора через второй резистор, а эмиттер непосредственно соединены с шиной нулевого потенциала, база первого ключевого транзистора подключена к шине нулевого потенциала через третий резистор, в каждый каскад регистра введен дополнительный 39 полевой транзистор, затвор которого соединен с коллектором второго ключевого транзистора данного каскада, сток - с базой второго ключевого транзистора данного каскада-, исток с коллектором первого ключевого тран зистора предыдущего каскада. На чертеже приведена принципиальная схема предлагаемого регистра, сдвига. Двухтактный динамический регистр сдвига содержит запоминающие конденсаторы 1 и 2, транзисторы 3 и типа, полевые транзисторы с затвором типа п, транзисторы 9 и 10 р-п-р типа, и источник 11 входного сигнала , источники 12 и 13 тактового питания, источник Н положительного постоянного напряжения , источник 15 импульсов управления, диоды 1б и 17, резисторы 18 и 19, выходную нагрузку 20, резисто ры 21-24. Устройство работает следующим об разом. Полевые- транзисторы 5 и 6 включе ны таким образом, что исток через п реход коллектор-эмиттер выходного транзистора второго саскада регистр сдвига предыдущего разряда и выходного транзистора первого каскада ре гистра сдвига данного разряда подключен к запоминающим конденсаторам сток - к базам транзисторных ключей затвор - к коллекторам транзисторов этих же транзисторных ключей. При поступлении входного сигнала от источника .11 в момент отсутствия тактирующего импульса от источника 12 регенеративное устройство, представляющее совместно включенные поле вой транзистор 5 и транзистор 3, открывается. При этом на затворе полевого транзистора 7 устанавливается низкий потенциал и транзистор 7 открывается. Происходит разряд запоминающего конденсатора 1. Постоян ная времени цепи разряда составляет несколько микросекунд. Р I где С - емкость конденсатора 1; - сопротивление канала открытого полевого транзистора 7После разряда запоминающего конденсатора 1 импульс управления от источника импульсов управления через диод 1б поступает на затвор полевого транзистора 7, повышает положительный его потенциал и закрывает его. При поступлении так.тирующего импульса от источника 12 тактового питаНИИ происходит заряд запоминающего конденсатора 1 по цепи : переход эмиттер-коллектор транзистора 9, канал полевого транзистора 6, переход база-эмиттер транзистора А. При заряде запоминающего конденсатора 1 до определенного уровня открывается транзистор l и. на затворе полевого транзистора 8 устанавливается низкий потенциал. Полевой транзистор 8 открывается и происходит разряд запоминающего конденсатора 2 через открытый канал полевого транзистора 8. Время начала разряда запоминающего конденсатора 2 зависит от времени срабатывания транзистора 4. Применение полевого транзистоpa 6 позволяет значительно уменьшить время переключения транзистора А по сравнению с временем переключения известного транзистора регистра сдвига, так как время переключения регенеративного устройства составляет несколько наносекунд. После разряда запоминающего конденсатора 2 и заряда запоминающего конденсатора 1 импульс управления от источника 15 импульсов управления через диод 17 поступает на затвор полевого транзистора 8, повышает положительный потенциал и закрывает его. При поступлении тактирующего импульса от источника 13 тактового питания происходит процесс заряда запоминающего конденсатора 2. Процесс заряда запоминающего конденсатора 2 такой же, как и конденсатор 1. 8 этом случае на нагрузке 20 выделяется сигнал, который является входным для регистра сдвига последующего разряда. 8 предлагаемой схеме быстродействие регистра сдвига зависит от переходных процессов при заряде и разр 1де запоминающих конденсаторов и от скорости переключения регенеративного устройства. Так как момент нача-, ла разряда запоминающего конденсатора 2 наступает значительно раньше , чем в известном регистре сдвига , то тактирующий импульс цсточника 13 тактового питания подается по отношению к моменту поступления тактирующего импульса от источника 12 тактового питания значительно раньше. Следовательно, частота

Авторы

Даты

1982-09-30—Публикация

1981-02-25—Подача