Изобретение относится к области вычислительной техники. Известна экономичная схема на полевых транзисторах с изолированным затвором, выполненных по технологии металл-окисел-полупроводник (МОП), в которой каждый разряд регистра содержит один потенциальный триггер с триггерными обратными связями, выполненными в виде двух МОП-транзис торов, отключаемых первым сдвигающим импульсом. Второй сдвигающий импульс подаваемый во время действия первого открывает ключевой транзистор, соединяющий источник ВХОДНОГО сигнала с затвором левого транзистора триггера (так называемый квазистатический регистр) 1 . Кратковременное промежуточное хра нение информации при сдвиге осуществляется на емкости цепи затвора одного из транзисторов триггера, а соответствующий выбор параметров МОП транзисторов, коммутирующих триггерные связи, обеспечивает надлежащую последовательность включения этих связей при записи информации в тригге Однако известная схема требует повышенной (по сравнению с входными и выxoдчн ги сигналагаг) амплиту.пы первого сдвигающего импульса, что усложняет генераторы импульсов сдвига и цепи распределения этих импульсов . - Известны двухтактные сдвигающие регистры, выполненные на основе статических потенциальных триггеров с раздельными входами, коммутируемыми по схеме И последовательно с ними включенным общим транзистором. Каждай разряд содержит два таких триггера|{2 , Недостатком регистра является его неэкономичность (требуется два триггера на один разряд регистра) ,. Цель изобретения - упрощение регистра, т.е.создание экономичной схемы сдвигающего регистра, использующей в каждом разряде только один триггер и не требующей повышенной ,«мплитуды тактовых т шпульсов. Уменьшение амплитуды тактовых импульсов достаточно важно в целом ряде применений регистров сдвига, Снижение амплитуды тактовых импульсов до величины входных и выходных сигналов разрядов регистра псэзволяет упростить генераторы тактовых импульсов и цепи распределения их, заменив

специальные устройства логическими элементами того же класса, на основе которого построен регистр и (или) логика устройства, в котором он работает.

Поставленная цель достигается тем, что в каждом разряде регистра пр:именен один триггер; триггер дополнен ключевым МОП-транзистором, через который входной сигнал подается на затвор левого входного МОП-транзистора; ключевой транзистор открывается первым тактовым импульсом, а второй тактовый импульс подается на затворы первого входного и общего МОП-транзисторов.

Для промежуточного хранения информации п-ри сдвиге применяется запоМина;ние сигнала на емкость цепи затвора: левого входного МОП-транзистора; соединение затворов правого входного и последовательно с ним включенного общего МОП-транзистора обеспечивает при записи информации в триггер надлежащую последовательность включения этих МОП-транзисторов.

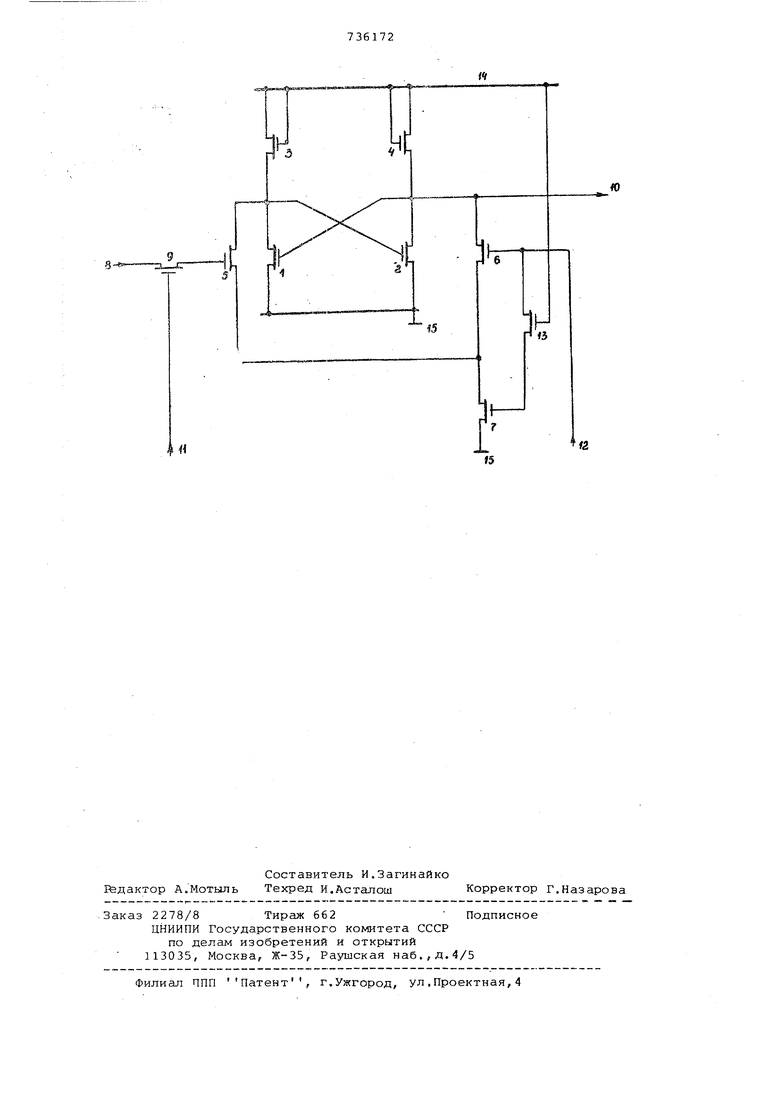

На чертеже приведена схема одного разряда двухтактного сдвигающего регистра.

Регистр содержит переключающие МОП-транзисторы 1 и 2, нагрузочные МОП-транзисторы 3 и 4 (которые об разуют триггер), сигналы на триггер подаются с помощью входных МОП-транзисторов 5 и 6, последовательно с которыми включен стабилизирующий МОП-транзистор 7.

Входной сигнал подается по входной шине 8 через ключевой МОП-транзистор 9 на затвор входного МОПтранзистора 5, Выходной сигнал 10 . снимается с правого инвертора триггера, собранного на МОП-транзисторах 3 и 4. Первый тактовый импульс подается по тактовой шин-е 11 на затвор ключевого МОП-транзистора 9, второй- по тактовой шине 12 на затворы МОП-транзисторов 6 и 7.

В схеме регистра выходной сигнгш триггера каждого разряда служит входным сигналом последующего, а шины одноименных тактовых сигналов объединены.

Вариант соединения затворов МОПтранзисторов 6 и 7 представлен через элемент 13 задержки, выполненный на МОП-транзисторе, образующим совместно с емкостью цепи затвора МОПтранзистора 7 замедляющую НС-цепочку

Рассмотрим работу двухтактного сдвигающего регистра на примере выполнения его на полевых- МОП-транзисторах. Уровень сигнала, близкий к напряжению на шине 14 питания, принят за логическую , уровень сигнала, близкий к потенциалу щины 15 нулевого потенциала - за логический О .

Записанная информация хранится в ячейках регистра до поступления тактовых импульсов. Сдвиг информации осуществляется двумя тактовыми импульсами 11 и 12 уровня иливышепоступающим на регистр поочередн Съем информации производится в интервалах между тактовыми импульсами 12,

В отсутствие тактовых импульсов МОП-транзисторы 9,6 и 7 заперты. Первый тактовый импульс 11 открывает МОП-транзистор 9 на время, достаточное для заряда или оазряда емкост цепи затвора МОП-транзистора 5 до уровня, близкого к уровню входног сигнала по шине 8. В дальнейшем напряжение на затворе МОП-транзистора 5 изменяется с постоянной времени, которая для МОП-транзисторов обычно составляет несколько сотен микросекунд или больше. Интервал между тактовыми импульсами по шинам 11, 12 и длительность второго тактового импульса по шине 12 выбираются достаточно малыми, чтобы к моменту снятия импульса по шине 12 этот уровень не успел существенно изменитьс 1ак как до подачи второго тактового импульса по 12 МОП-транзисторы 6 и 7 закрыты, то МОП-транзистор 5 не оказывает влияния на состояние триггера.

Второй тактовый импульс по шине 12 открывает МОП-транзисторы 6 и 7, в результате чего на выходе 10 устанавливается уровень О, а МОПтранзистор 1 закрывается.

Если на шину 8 поступает О, то закрытый МОП-транзистор 5 не оказывает влияния на состояние триггер и после открывания МОП-транзисторов б и 7. После исчезновения импульса по шине 12 в триггере будет записан О .

Если на выход разряда регистра

1

МОП-транпоступает сигнал

зистор 5 будет в проводящем состоянии, поэтому когда тактовый импульс по шине. 12 открывает МОП-транзисторы 6 и 7, уровень О устанавливается не только на выходе 10, но и на сток МОП-транзистора 1, а МОП-транзистор 4 закрывается.

Для записи 1 в триггер необходимо, чтобы ток в цепи МОП-транзисторов -2-5-7 существовал некоторое, время после исчезновения (или существенного уменьшения) тока в цепи МОП-транзисторов 3-6-7. Это обеспечивает открывание МОП-транзистора 1 при запертом МОП-транзисторе 4. При снятии второго тактового импульса 12 МОП-транзистор 6 закрывается раньше чем МОП-транзистор 1.

Такая последовательность может быть достигнута несколькими путями. Падение напряжения на МОП-транзисторе 7 создает смещение на истоке МОПтранзистора 6, повышая его пороговое напряжение. При необходимости порого вое напряжение МОП-транзистора 6 мож быть повышено технологическим путем, например увеличением толщины слоя окисла под его затвором. Большее пороговое напряжение МОП-транзистора 6 по сравнению с МОП-транзистором 7 обеспечивает требуемую последовательность закрывания этих транзисторов во время действия заднего фронта так1-ового импульса по шине 12 Этот же эффект может быть достигнут, если второй тактовый импульс по. шине 12 с затвора МОП-транзистора 6подать на затвор МОП-транзистора 7через элемент задержки, например через шину с повышенн лми распределительными сопротивлением и емкостью , или через постоянно открытый МОПтранзистор 13, образующий интегральну цепочку совместно с емкостью цепи затвора МОП-транзистора 7. В описанном регистра приведен известный вариант статического потенциального триггера, в котором МОПтранзисторы 2 и 3 применены в качестве нагрузочных резисторов, а остальные МОП-транзисторы - в качестве переключателей. Очевидно, что регистр допускает реализацию и на других схемах статических потенциальных триггеров. С учетом ограничений, упомянутых в описании, он может также быть выполнен и на других элементах-транзисторах, реле и Т .д,. Однако интегральное исполнение на полевых транзисторах представляется наиболее- целесообразной его реализ:ацией. Формула изобретения 1. Двухтактный сдвигающий регистр содержащий два переключающих МОПтранзистора, истоки которых.соединены с шиной нулевого потенциала, стоки соединены с истоками нагрузочных МОП-транзисторов, стоки и затворы которых подключенык шине питания, и стоки входных МОП-транзисторов, истоки которых соединены со стоками стабилизирующего МОП-транзистора, исток которого подключен к шине нулевого потенциала, затвор первого переключающего МОП-транзистора подключен к стоку второго, а затвор второго переключающего МОП-транзистора - к стоку первого, отличающийся тем,что, с целью упрощения регистра, он содержит iключeвoй МОП-транзистор, затвор одного из входных МОП-транзисторов соединен с однойиз тактовых шин и с затвором стабилизирующего МОП-транзистора, затвор ключевого МОП-транзистора соединен с другой тактовой шиной, исток - с затвором другого входного МОП-транзистора, сток - с входной шиной. 2. Регистр по П.1, о тли ч ающ и и с я тем, что он содержит эле-. мент задержки, выполненный, например, в виде МОП-транзистора,исток и сток которого соединен соответственно с затворами стабилизирующего и одного из входных МОП-тракзисторов, а затвор с шиной питания. Источники информации, принятые во внимание при экспертизе 1.-,Электроника, № 17 40 1967, с.53-54. .. 2. Каталог МОП интегральные схемы . 1967, с. 15, микросхема 1 ЦТ1 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Ч.:.СОЮЗНАЯ | 1973 |

|

SU387437A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| Д-триггер | 1971 |

|

SU677073A1 |

| Двухтактный динамический регистр сдвига | 1981 |

|

SU963103A1 |

| Устройство для выборки адресов из блоков памяти | 1976 |

|

SU744722A1 |

| ТРИГГЕР НА МОП—ТРАНЗИСТОРАХ | 1973 |

|

SU391709A1 |

| Преобразователь напряжения для кварцевых наручных часов | 1988 |

|

SU1497695A1 |

Авторы

Даты

1980-05-25—Публикация

1968-05-31—Подача