(54) РАНГОВЫЙ ОБНАРУЖИТЕЛЬ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный ранговый обнаружитель | 1975 |

|

SU566218A1 |

| Адаптивный ранговый обнаружитель | 1979 |

|

SU800927A2 |

| Обнаружитель сигналов | 1980 |

|

SU907487A1 |

| Адаптирующийся ранговый обнаружитель | 1981 |

|

SU995042A1 |

| ВЫЧИСЛИТЕЛЬ РАНГОВОЙ СТАТИСТИКИ | 1997 |

|

RU2122746C1 |

| Устройство для автоподстройки частоты и цифровой обнаружитель-измеритель частоты | 1982 |

|

SU1092733A1 |

| Устройство для распознавания случайных процессов | 1988 |

|

SU1621046A1 |

| РАНГОВЫЙ АДАПТИВНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ ОБНАРУЖИТЕЛЬ СИГНАЛОВ | 1996 |

|

RU2100822C1 |

| Цифровой фазометр | 1982 |

|

SU1033983A1 |

| Измеритель сдвига фаз | 1986 |

|

SU1366966A1 |

Изобретение относится к радиотехнике и может использоваться в радиолокационных и связных устройствах для обнаружения сигналов на фоне помех при наличии нескольких сигналов в соседних каналах.

Известен ранговый обнаружитель сигналов, содержащий последовательно включенные согласованный фильтр, ;первый детектор, многоотводную линию задержки,М отводов которой соединены с соответствующими М-входами первого вычислителя ранга, (М-,)-й вход которого соединен с выходом первого детектора, последовательно включенные генератор ожидаемого сигнала, сумматор и второй детектор, последовательно включенные второй вычислитель ранга, блок вычисления вероятности, вычитатель и накапливающий сумматор, и последовательно включенные перемножитель и решающий блок, при этом выход согласованного фильтра соединен с вторым входом cyr iMaтора, М входов второго вычислителя ранга соединены с соответствующими М выходами многоотводной линии Задержки, а (М+1)-и вход - с выходом второго детектора, а выход первого .

вычислителя ранга соединен с вторым входом вычитателя Cl.

Однако известное устройство имеет малую вероятность правильного обнаружения при наличии нескольких сигналов в пределах опорной выборки, что приводит к подавлению одного сигнала другим и резкому ухудшению характеристик обнаружителя. Такой

10 обнаружитель не обеспечивает расчетных характеристик вероятности правильного обнаружения при наличии сигналов в сравнительно близких каналах, что, учитывая относительно

15 больст1е размеры рекомендуемых опорных выборок (-f 20-30), является вполне реальной практической ситуацией.

Цель изобретения - увеличение ве20роятности правильного обнаружения при наличии нескольких сигналов в пределах опорной вяборки.

Поставленная цель достигается тем, что в ранговый обнаружитель

25 сигналов, содержащий последовательно включенные согласованньлй фильтр, первый детектор, многоотводную линию задержки, М отводов которой соединены с соответствующими М входами первого вычислителя ранга; (М+1)-и

30 вход которого соединен с выходом первого детектора, последовательно включенные генератор ожидаемого сиг нала, сумматор и второй детектор, последовательно включенные второй вычислитель ранга, блок вычисления вероятности,, вычитатель и накапли.вающий сумматор, и последовательно включенные перемножитель и решающий блок, при этом выход согласованного фильтра соединен с вторым входом сумматора, М входов второго вычислителя ранга соединены с соответствующим М выходами многоотводной линии задержки, а (М+1)-й вход с выходом второго детектора, а выход первого вычислителя ранга соединен с вторым входом вычитателя, введены первый и второй дополнительные сумматоры, блок коррекции и синхрониза тор, при этом выход накапливающего сумматора соединен с первым входом первого дополнительного сумматора, второй вход которого подключен к первому выходу блока коррекции, выхо первого дополнительного сумма.тора соединен с первым входом перемножителя, второй вход которого через второ{ дополнительный суглматор подключен к второму выходу блока вычис ления вероятности, второй выход блока коррекции подключен к второму вхо ду второго дополнительного сумматор вход синхронизатора и первый вход блока коррекции подключены соответственно к первому и второму выходам решающего блока, вторые входы блоков вычисления вероятности и коррекции объединены и подключены к первому выходу синхронизатора, второй и третий выходы которого соединены с одноименными входами накапливающего сумматора, а четвертый выход синхронизатора соединен с третьими входами блоков вычисления вероятности и коррекции. Вычислитель ранга содержит М компараторов , выходы которых соединены с соответствующими из М входов сумматора, при этом М входами, (М+1)-м входом и выходом вычислителя ранга соответственно являются первые входы М компараторов, соединенные между собой вторые входы М компараторов и выход сумматора. Блок вычисления вероятности содер жит делитель на два, К-разрядный регистр сдвига, первый сумматор, пер вый блок вычитания,, последовательно соединенные второй сумматор, делител на К, второй блок вычитания, делитель на п, третий сумматор и N-разрядный регистр сдвига, при этом каждый из К выходов К-разрядного регист ра сдвига соединен с соответствующим входом второго сумматора, выход N-ro разряда N-разрядного регистра сдвига соединен с вторыми входами второго блока вычитания и третьего сумматора, первый выход первого блока вычитания подключен к выходу первого разряда N-разрядного регистра сдвига, первый вход и выход первого сумматора соответственно подключена к второму выходу делителя на К и входу делителя на два, вторые входы первого сумматора и первого блока вычитания являются входами сигналов коэффициентов, тактовые входы К и N-разрядных регистров сдвига соединены между собой, а первым, вторым и третьим входами и первым и вторым выходами блока вычисления вероятности являются соответственно информационный вход К-разрядного регистра сдвига, объединенные тактовые входы К и N-разрядных регистров сдвига и второй вход делителя на п и выходы первого блока вычитания и делителя на два. Накапливающий сумматор содержит последовательно включенные сумматор и блок памяти, выход которого соединен с вторым входом сумматора, при этом первым, вторым и .третьим входами и выходом накапливающего сумматора соответственно являются второй вход сумматора, второй и третий входы блока памяти и выход сумматора. Ре1г1аю1№1й блок содержит первый пороговый блок и последовательно соединенные второй пороговый блок и элемент ИЛИ, второй вход которого подключен к выходу первого порогового блока, входы первого и второго пороговых блоков объединены и являются входом решающего блока, а выходы элемента ИЛИ и первого порогового блока являются соответственно перВ1 1м и вторым выходами решающего блока. Блок коррекции содержит последовательно соединенные делитель и первый перемножитель, а также последовательно соединенные (М+1)-разрядный регистр сдвига, счетчик и второй перемножитель, приэтом первый вход (M+l)-разрядного регистра сдвига соединен с вторым входом счетчика, выход которого соединен с вторым входом первого перемножителя, причем информационный и тактовый входы () -разрядного регистра сдвига и вход делителя являются соответственно первым, вторым и третьим входами блока коррекции, первым и вторым выходами которого соответственно являются выходы первого и второго перемножителей . .Синхронизатор содержит формирователь адреса и последовательно включенные генератор тактовых импульсов, счетчик реиений, блок сравнения и счетчик периодов наблюдений, соединенный своим вторым входом с первым выходом генератора тактовых импульсов, второй ВЫХОД которого соединен

с входом формирователя адреса, при :ЭтоМ входом и первым, вторым, третьим и четвертым выходами синхронизатора соответственно являются второй вход счетчика решений, второй выход генератора тактовых импульсов, выход формирователя адреса , выход блока сравнения и выход счетчика периодов наблюдений.

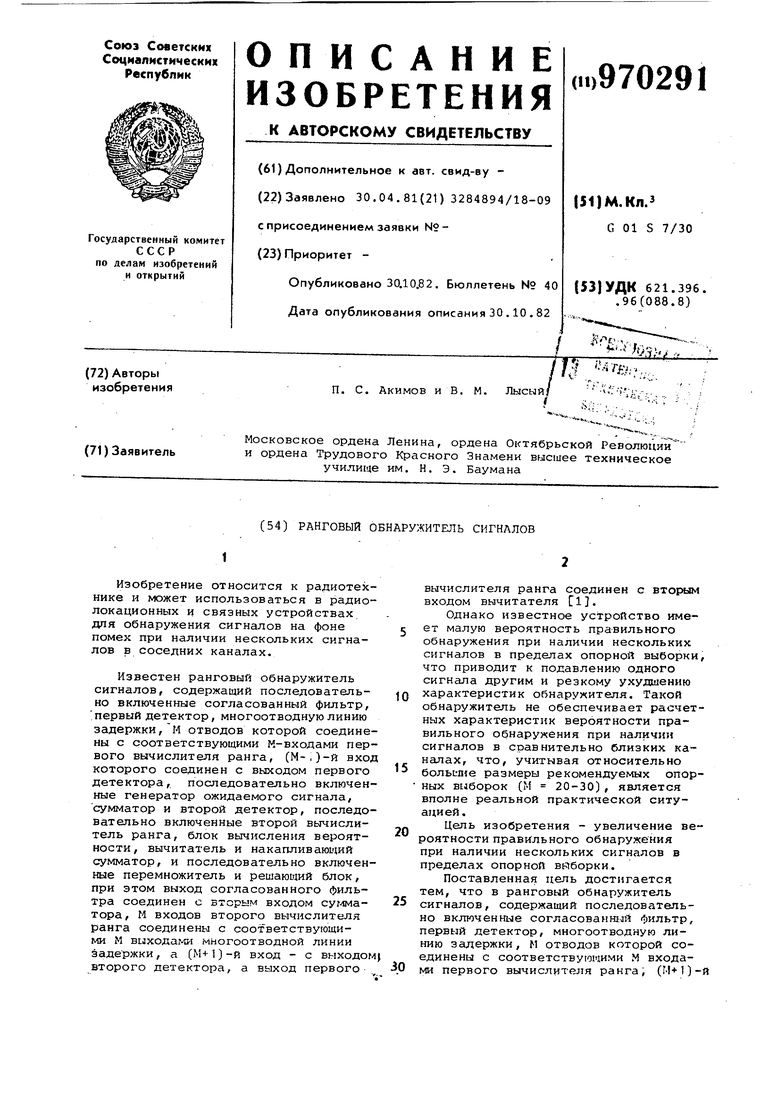

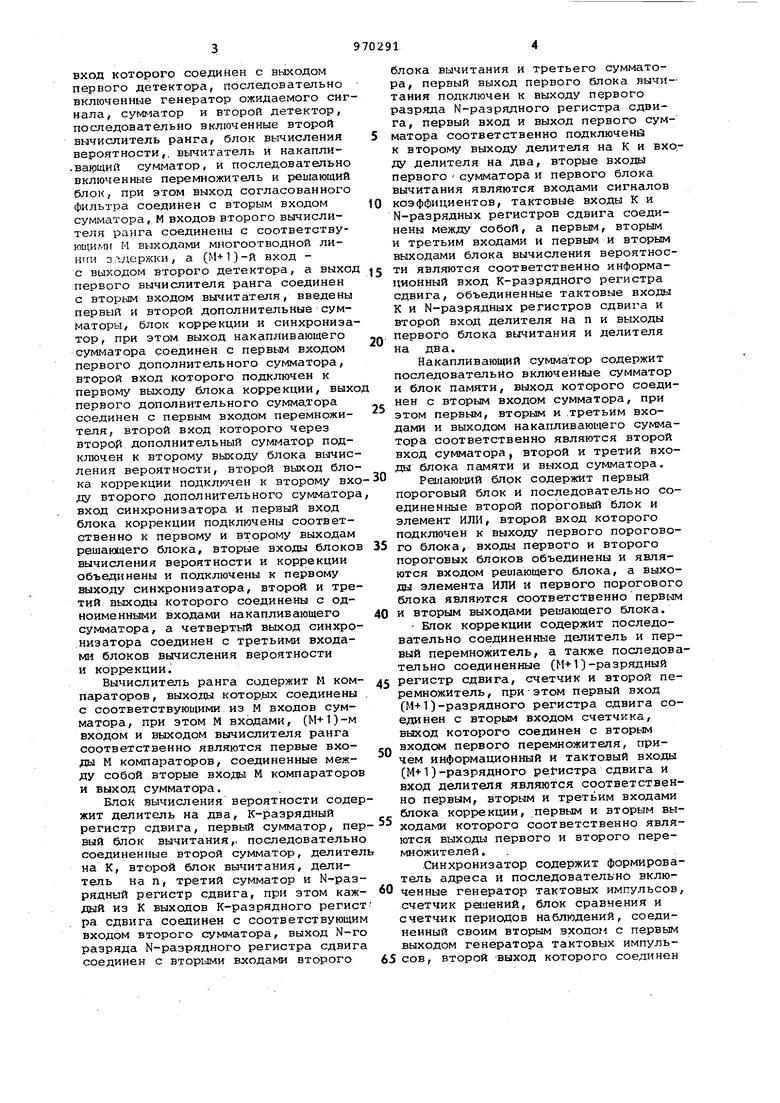

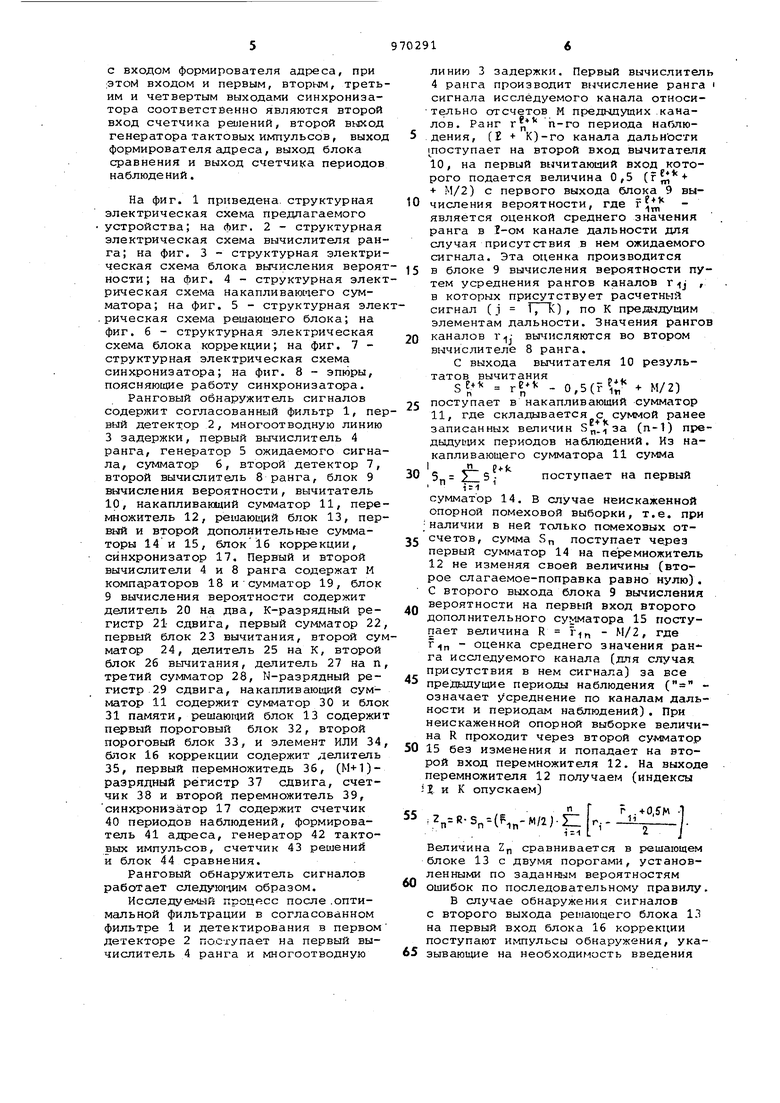

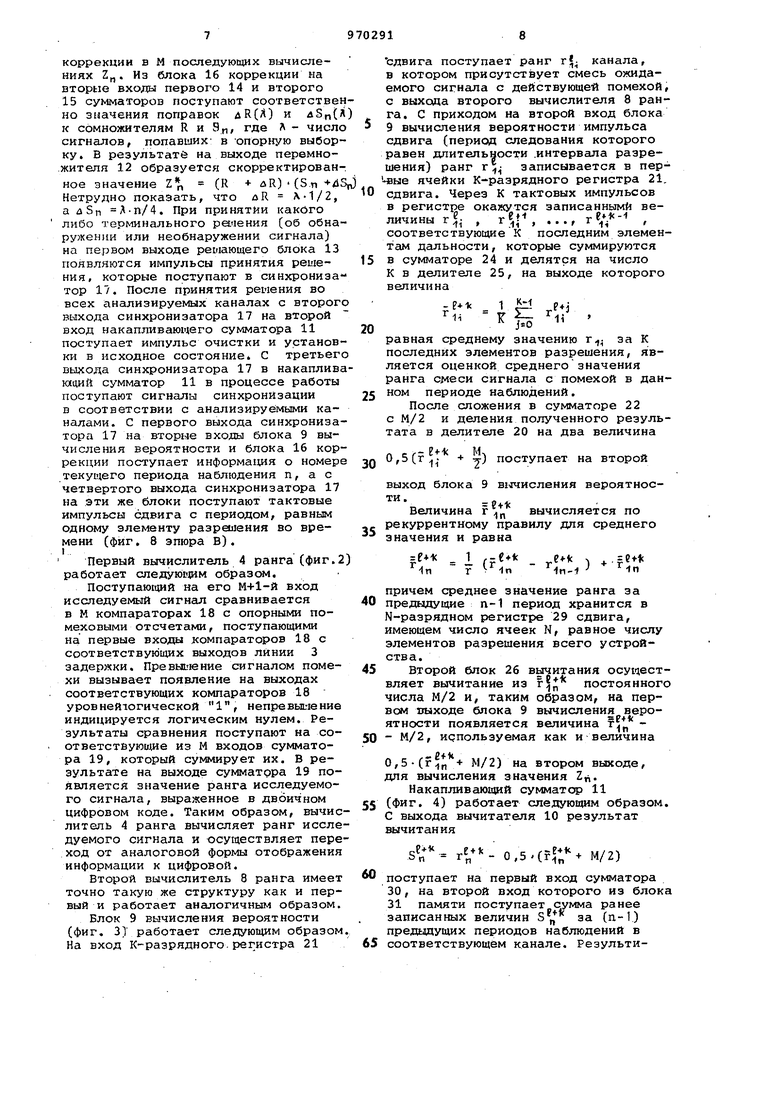

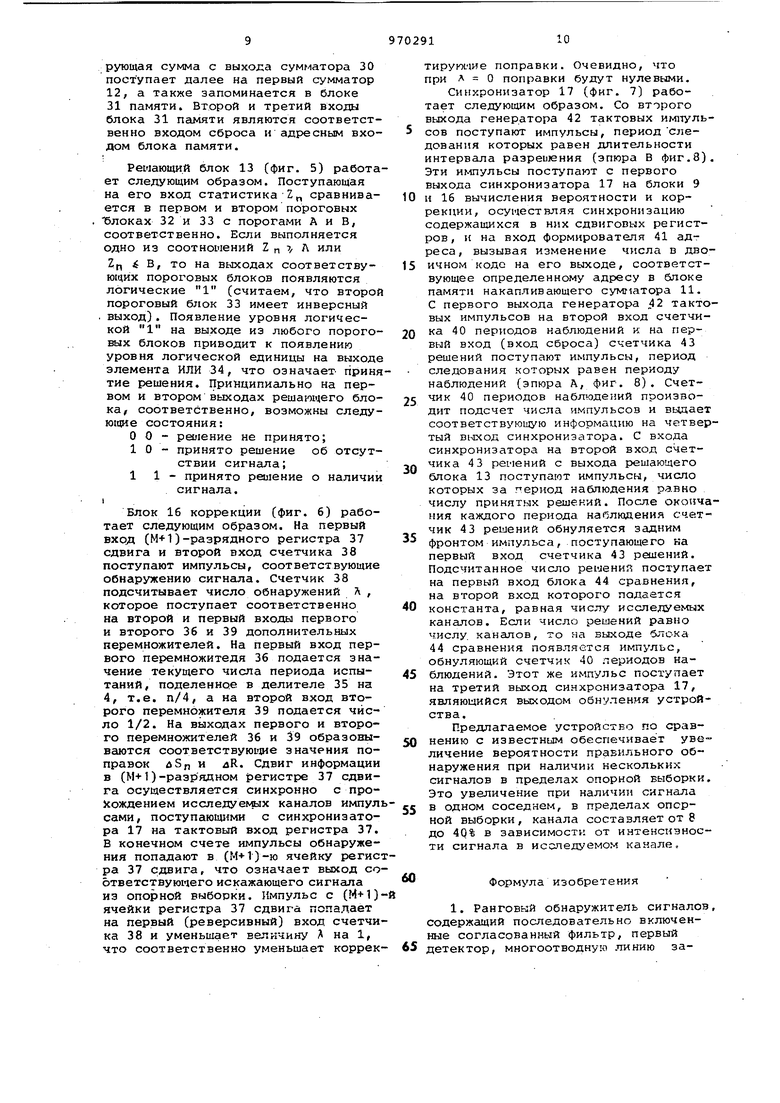

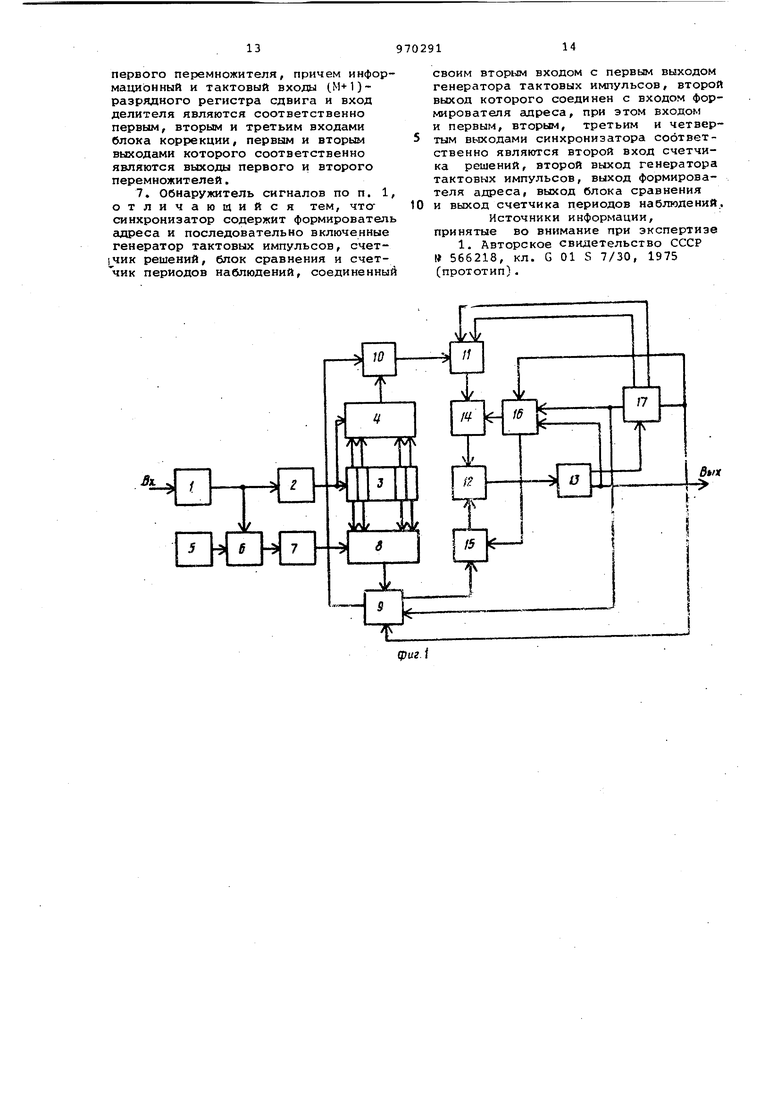

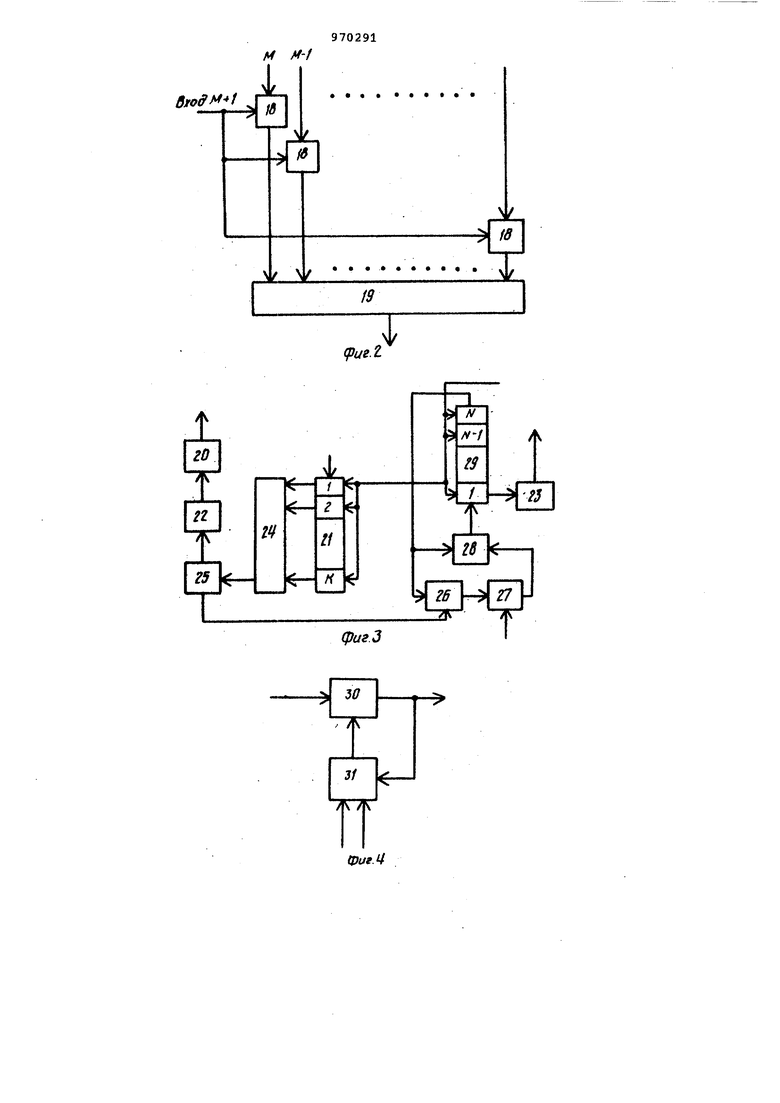

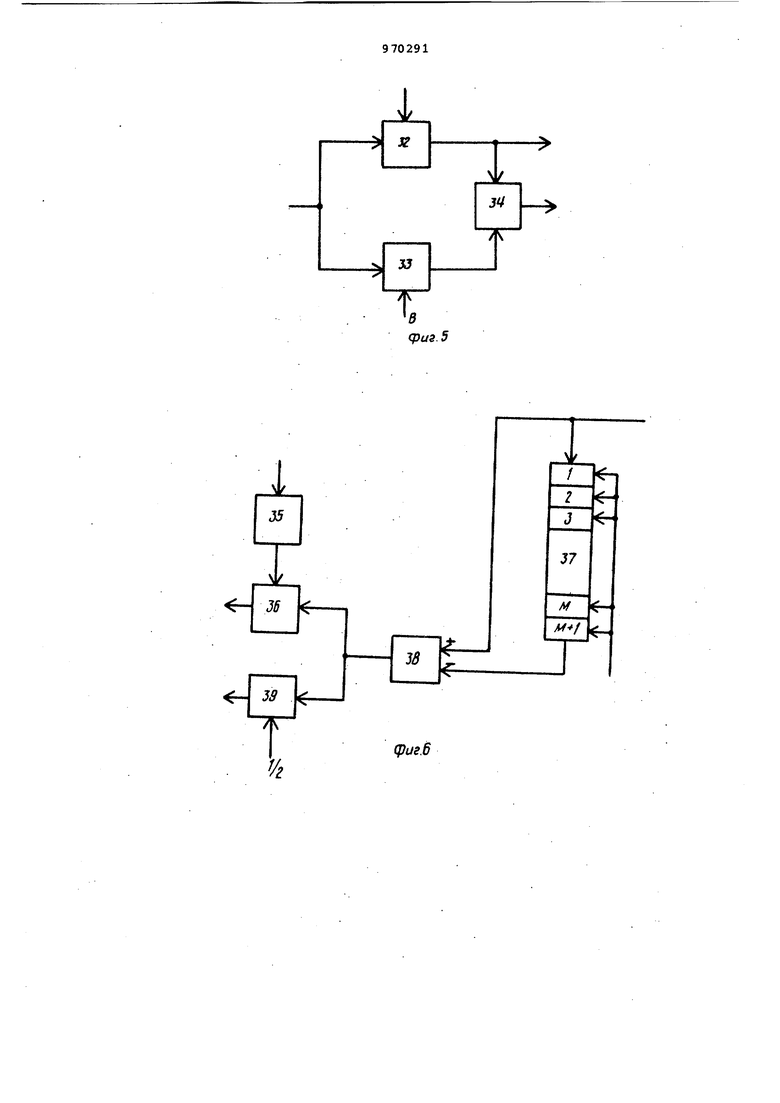

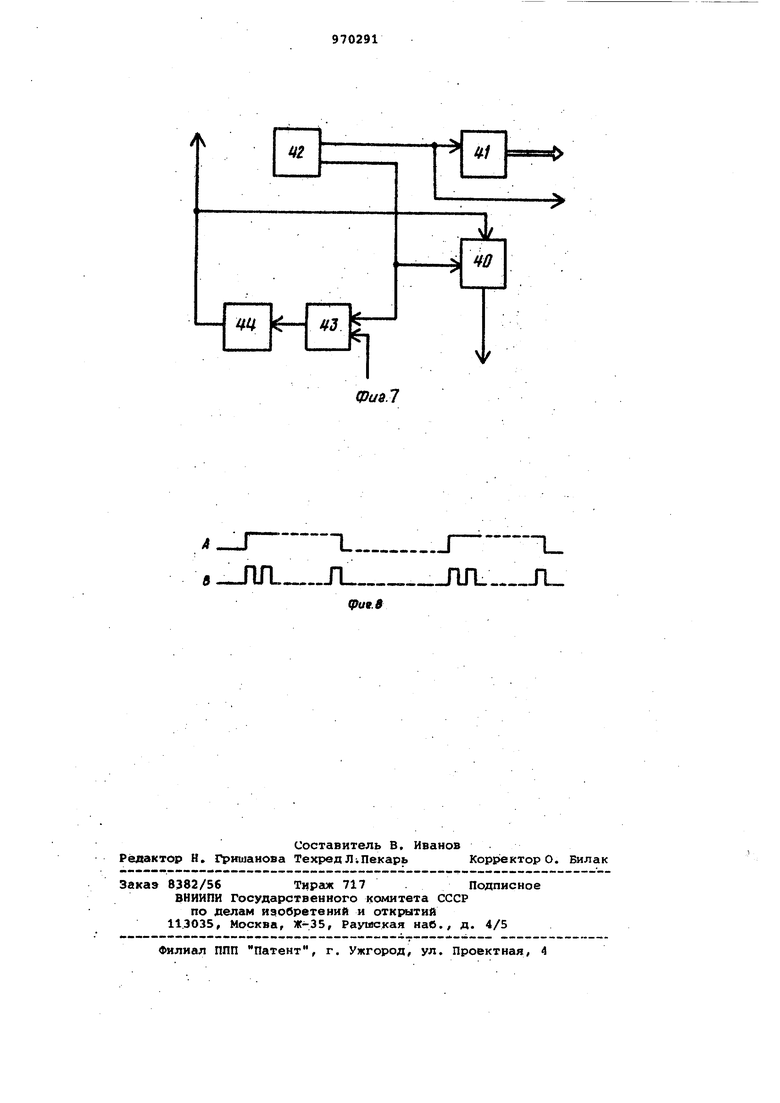

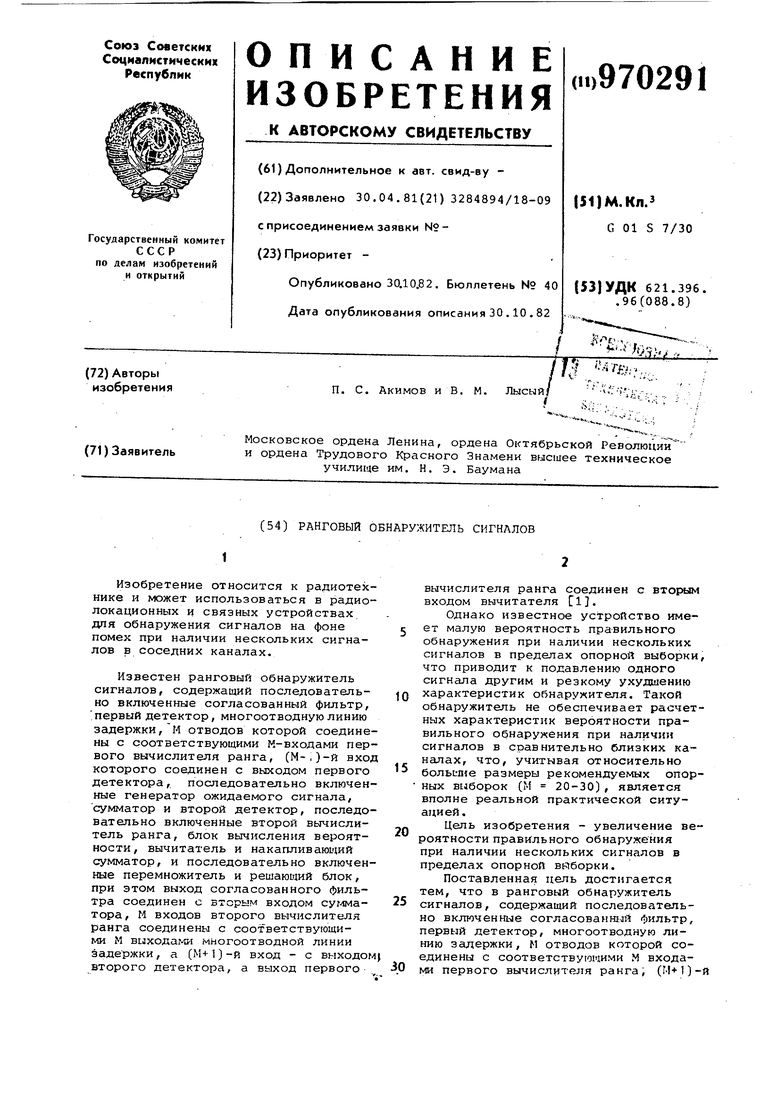

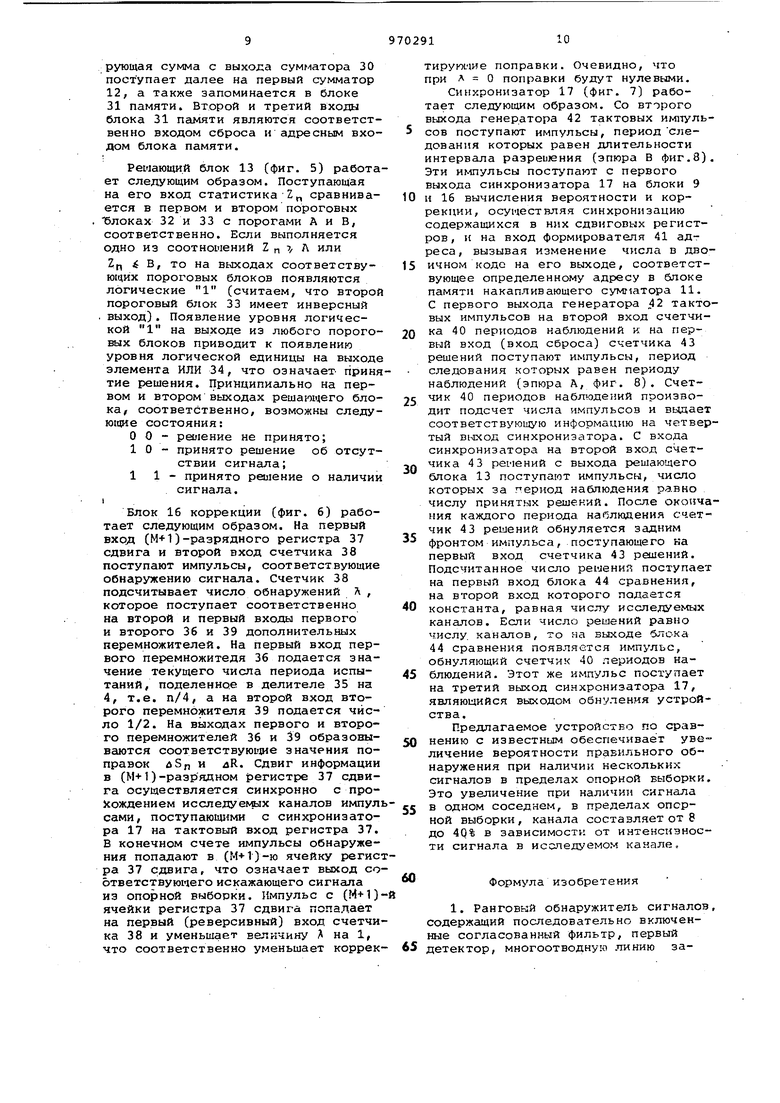

На фиг. 1 приведена, структурная электрическая схема предлагаемого устройства; на фиг. 2 - структурная электрическая схема вычислителя ранга; на фиг. 3 - структурная электрическая схема блока вычисления вероятности; на фиг. 4 - структурная электрическая схема накапливающего сумматора; на фиг. 5 - структурная элек рическая схема решающего блока; на фиг. 6 - структурная электрическая схема блока коррекции; на фиг. 7 структурная электрическая схема синхронизатора; на фиг. 8 - эпюры, поясняющие работу синхронизатора.

Ранговый обнаружитель сигналов содержит согласованный фильтр 1, первый детектор 2, многоотводную линию 3 задержки, первый вычислитель 4 ранга, генератор 5 ожидаемого сигнала, сумматор 6, второй детектор 7, второй вычислитель 8 ранга, блок 9 вычисления вероятности, вычитатель 10, накапливающий сумматор 11, перемножитель 12, решающий блок 13, первый и второй дополнительные сумматоры 14 и 15, блок 16 коррекции, синхронизатор 17. Первый и второй вычислители 4 и 8 ранга содержат М компараторов 18 и сумматор 19, блок 9 вычисления вероятности содержит делитель 20 на два, К-разрядный регистр 21 сдвига, первый сумматор 22, первый блок 23 вычитания, второй сумматор 24, делитель 25 на К, второй блок 26 вычитания, делитель 27 на п, третий сумматор 28, N-разрядный регистр 29 сдвига, накапливающий сумматор 11 содержит сумматор 30 и блок 31 памяти, решающий блок 13 содержит первый пороговый блок 32, второй пороговый блок 33, и элемент ИЛИ 34, блок 16 коррекции содержит делитель 35, первый перемножитедь 36, (М+1)раэрядный регистр 37 сдвига, счетчик 38 и второй перемножитель 39, синхронизатор 17 содержит счетчик 40 периодов наблюдений, формирователь 41 адреса, генератор 42 тактовых импульсов, счетчик 43 решений и блок 44 сравнения.

Ранговый обнаружитель сигналов работает следующим образом.

Исследуемь1й процесс после .оптимальной фильтрации в согласованном фильтре 1 и детектирования в первом детекторе 2 поступает на первый вычислитель 4 ранга и многоотводную

линию 3 задержки. Первый вычислитель 4 ранга производит вычисление ранга i сигнала исследуемого канала относительно отсчетов М предыдущих .каналов. Ранг г п-го периода наОлюдения, ( К)-го канала дальности поступает на второй вход вычитатепя

10,на первый вычитающий вход которого подается величина 0,5 ( М/2) с первого выхода блока 9 вычисления вероятности, где

является оценкой среднего значения ранга в 1-ом канале дальности для случая присутствия в нем ожидаемого сигнала. Эта оценка производится

5 в блоке 9 вычисления вероятности путем усреднения рангов каналов г j , в которых присутствует расчетный сигнал (J 1, К), по К предыдущим элементам дальности. Значения рангов

0 каналов вычисляются во втором вычислителе 8 ранга.

С выхода вычитателя 10 результатов вычитания ...

г - 0,5( М/2)

5 поступает в накапливающий сумматор

11,где складывается с суммой ранее записанных величин S.iSa (п-1) предыду11их периодов наблюдений. Из накапливающего сумматора 11 сумма

1 п PJ.J;,

0 5 Z- 5 поступает на первый in

сумматор 14. В случае неискаженной опорной помеховой выборки, т.е. при наличии в ней только помеховых отсчетов, сумма Sn поступает че.рез первый сумматор 14 на пере множитель 12 не изменяя своей величины (второе слагаемое-поправка равно нулю). С второго выхода блока 9 ВЕЛЧислвния

Q вероятности на первый вход второго дополнительного сумматора 15 поступает величина R г - М/2, где - оценка среднего значения ранга исследуемого канала (для случая присутствия в нем сигнала) за все

предыдущие периоды наблюдения ( означает Усреднение по каналам дальности и периодам наблюдений). При неискаженной опорной выборке величина R проходит через второй суммато.р

0 15 без изменения и попадает на второй вход перемножителя 12. На выходе перемножителя 12 получаем (индексы .Ни К опускаем)

(.,.

55

Величина Zp сравнивается в решающем блоке 13 с двумя порогами, установленными по заданным вероятностям ошибок по последовательному правилу.

В случае обнаружения сигналов с второго выхода решающего блока 13 на первый вход блока 16 коррекции поступают импульсы обнаружения, указывающие на необходимость введения коррекции в М последующих вычислениях Z. Из блока 16 коррекции на вторые входы первого 14 и второго 15 сумматоров поступают соответствен но значения поправок дЯ(Д) и dSnt к сомножителям R и Э,, где Л - число сигналов, попавших в -опорную выборку. В результате на выходе перемножителя 12 образуется скорректированное значение , (R + R) (S.n Нетрудно показать, что , а л5п Д-п/4. При принятии какого либо терминального ре1чения (об обнаружении или необнаружении сигнала) на первом выходе решающего блока 13 появляются импульсы принятия решения, которые поступают в синхронизатор 17. После принятия решения во всех анализируемых каналах с второг выхода синхронизатора 17 на второй вход накапливающего сумматора 11 поступает импульс очистки и установки в исходное состояние С третьег выхода синхронизатора 17 в накаплива ющий сумматор 11 в процессе работы поступают сигналы синхронизации в соответствии с анализируемыми каналами. С первого выхода синхронизатора 17 на вторые входы блока 9 вычисления вероятности и блока 16 коррекции поступает информация о номере TeKytuero периода наблюдения п, а с четвертого выхода синхронизатора 17 на эти же блоки поступают тактовые импульсы сдвига с периодом, равным одному элементу разрешения во времени (фиг. 8 эпюра В). Первый вычислитель 4 ранга (фиг.2 работает спедую11|им образом. Поступающий на его М+1-й вход исследуемый сигнал сравнивается в М компараторах 18 с опорными помеховыми отсчетами, поступающими на первые входы компараторов 18 с соответствук щих выходов линии 3 задержки. Превышение сигналом помехи вызывает появление на выходах соответствующих компараторов 18 уровнейюгической 1, непревьпление индицируется логическим нулем. Результаты сравнения поступают на соответствующие из М входов сумматора 19, который суммирует их. В результате на выходе сумматора 19 появляется значение ранга исследуемого сигнала, выраженное в двоичном цифровом коде. Таким образом, вычис литель 4 ранга вычисляет ранг иссле дуемого сигнала и осуществляет пере ход от аналоговой формы отображения информации к цифровой. Второй вычислитель 8 ранга имеет точно такую же структуру как и первый и работает аналогичным образом. Блок 9 вычисления вероятности (фиг, 3Т работает следующим образом На вход К-разрядного. рег истра 21 сдвига поступает ранг канала, в котором присутствует смесь ожидаемого сигнала с действующей помехой, с выхода второго вычислителя 8 ранга. С приходом на второй вход блока 9 вычисления вероятности импульса сдвига (период следования которого равен длительности .интервала разрешения) ранг записывается в пер-аые ячейки К-разрядного регистра 21. сдвига. Через К тактовых импульсов в регистре окажутся записанными величины г - , , ..., , соответствующие К последним элементам Дсшьности, которые суммируются в сумматоре 24 и делятся на число К в делителе 25, на выходе которого величина 1 1 1 - 1 1i равная среднему значению г за К последних элементов разрешения, является оценкой среднего значения ранга смеси сигнала с помехой в данном периоде наблюдений. После сложения в сумматоре 22 с М/2 и деления полученного результата в делителе 20 на два величина 0,5(г. + 4-) поступает на второй выход блока 9 вичисления вероятнос™- -г+к Величина г „ вычисляется по рекуррентному правилу для среднего значения и равна 1 г 4- « г причем среднее значение ранга за предыдущие п-1 период хранится в N-разрядном регистре 29 сдвига, имеющем число ячеек N, равное числу элементов разрешения всего устройства. Второй блок 26 вычитания осуществляет вычитание из г постоянного числа М/2 и, таким образом, на первом выходе блока 9 вычисления вероятности появляется величина , М/2, идпользуемая как и величина f fit It 0,5-( М/2) на втором выходе, для вычисления значения Z. Накапливающий сумматор 11 (фиг. 4) работает следующим образом. С выхода вычитателя 10 результат вычитания - 0,5(r поступает на первый вход сумматора 30, на второй вход которого из блока 31 памяти поступает сумма ранее записанных величин SJ за (п.-1) предаддущих периодов наблюдений в соответствующем канале. Результирующая сумма с выхода сумматора 30 поступает далее на первый сумматор 12, а также запоминается в блоке 31 памяти. Второй и третий входы блока 31 памяти являются соответственно входом сброса и адресным входом блока памяти.

Решающий блок 13 (фиг. 5) работает следующим образом. Поступающая на его вход статистика Z, сравнивается в первом и втором пороговых Тблоках 32 и 33 с порогами А и В, соответственно. Если выполняется одно из соотношений Z п / Л или Zf, В, то на выходах соответствующих пороговых блоков появляются логические 1 (считаем, что второй пороговый блок 33 имеет инверсный . выход). Появление уровня логической 1 на выходе из любого пороговых блоков приводит к появлению уровня логической единицы на выходе элемента ИЛИ 34, что означает принятие решения. Принципиально на первом и втором выходах решающего блока, соответственно, возможны следующие состояния:

0О - решение не принято;

1О - принято решение об отсутствии сигнала; 1 1 - принято решение о наличии

сигнала.

I

Блок 16 коррекции (фиг. 6) работает следующим образом. На первый вхрд (M+l)-разрядного регистра 37 сдвига и второй вход счетчика 38 поступают импульсы, соответствующие обнаружению сигнала. Счетчик 38 подсчитывает число обнаружений Л , которое поступает соответственно на второй и первый входы первого и второго 36 и 39 дополнительных неремножителей. На первый вход первого перемножитедя 36 подается значение текущего числа периода испытаний, поделенное в делителе 35 на 4, т.е. п/4, а на второй вход второго перемножителя 39 подается число 1/2. На выходах первого и второго перемножителей 36 и 39 образовываются соответствующие значения поправок й5л и лК. Сдвиг информации в (М+1)-разрядном регистре 37 сдвига осуществляется синхронно с прохождением исследуемых каналов импулсами, поступающими с синхронизатора 17 на тактовый вход регистра 37. В конечном счете импульсы обнаружения попадают в ()-ю ячейку регисра 37 сдвига, что означает выход соответствующего искажающего сигнала из опорной выборки. Импульс с (М+1) ячейки регистра 37 сдвига попадает на первый (реверсивный) вход счетчика 38 и уменьшает величину Д на 1, что соответственно уменьшает корректирующие поправки. Очевидно, что при л О поправки будут нулевыми.

Синхронизатор 17 (фиг. 7) работает следующим образом. Со второго выхода генератора 42 тактовых им1тульсов поступают импульсы, периодследования которых равен длительности интервала разрешения (эпюра В фиг.8). Эти импульсы поступают с первого выхода синхронизатора 17 на блоки 9

0 и 16 вычисления вероятности и коррекции, осуществляя синхронизацию содержащихся в них сдвиговых регистров, и на вход формирователя 41 адреса, вызывая изменение числа в дво5ичном коде на его выходе, соответствующее определенному адресу в блоке памяти накапливающего сумпатора 11. С первого выхода генератора 42 тактовых импульсов на второй вход счетчика 40 периодов наблюдений к на пер0вый вход (вход сброса) счетчика 43 решений поступают импульсы, период следования которых равен периоду наблюдений (эпюра А, фиг. 8). Счетчик 40 периодов наблюдений произво5дит подсчет числа импульсов и выдает соответствующую информацию на четвертый В1л1ход синхронизатора. С входа синхронизатора на второй вход счетчика 43 ре11ений с выхода решающего

0 блока 13 поступают импульсы, число которых за период наблюдения равно числу принятых решений. После око(5чамия каждого периода наблюдения счетчик 43 решений обнуляется задним

5 фронтом импульса, поступающего ка первый вход счетчика 43 решений. Подсчитанное число решения поступает на первый вход блока 44 сравнения, на второй вход которого подается

0 константа, равная числу исследуемых каналов. Если число решений равно числу, каналов, то на выходе блока 44 сравнения появляется импульс, обнуляющий счетчик 40 периодов на5блюдений. Этот же импульс поступает на третий выход синхронизатора 17, являющийся выходом обнуления устройства.

Предлагаемое устройство по сравнению с известным обеспечивает уве0личение вероятности правильного обнаружения при наличии нескольких сигналов в пределах опорной выборки. Это увеличение при наличии сигнала в одном соседнем, в пределах опор5ной выборки, канала составляет от 8 до 4Q% в зависимости от интенсивности сигнала в исследуемом канале.

60

Формула изобретения

65 детектор, многоотводную линию задержки, М отводов которой соединены с соответствующими М входами первого вычислителя ранга, (М+1)-й вход которого соединен с выходом первого детектора, последовательно включенные генератор ожидаемого сигнала, сумматор и второй детектор, последовательно включенные второй вычислитель ранга, блок вычисления вероятности, вычитатель и накапливающий сумматор и последовательно включенные перемножитель и реглающий блок, при этом выход согласованного фильтра соединен с вторым входом сумматора, М входов второго вычислителя ранга соединены с соответствующими М выходами многоотводной линии задержки , а (М+1)-и вход с выходом второго детектора, выход первого вычислителя ранга соединен с вторым входом вычитателя, отличающийс я тем, что, с целью увеличения вероятности правильного обнаружения при наличии нескольких сигналов в пределах опорной выборки, введены первый и второй дополнительные сумматоры, блок коррекции и синхронизатор, при этом выход накапливающего сумматора соединен с первым входом первого дополнительного сумматора, второй вход которого подключен к первому выходу блока коррекции, выхо первого дополнительного сумматора соединен с первым входом перемножителя, второй вход которого через второй дополнительный сумматор подключен к второму выходу блока вычисления вероятности, второй выход блока коррекции подключен к второму входу второго дополнительного сумматора, вход синхронизатора и первый вход блока коррекции подключены соответственно к первому и второму выходам решающего блока, вторые входы блоков вычисления вероятности и коррекции объединены и подключены к первому выходу синхронизатора, второй и третий выходы которого соединены с одноименными входами накапливающего сумматора, а четвертый выход синхронизатора соединен с третьими входами блоков вычисления вероятности и коррекции.

сдвига, первый сумматор, первый блок вычитания, последовательно соединенные второй сумматор, делитель на К, второй блок вычитания, делитель на п, третий сумматор и N-разрядный регистр сдвига, при этом каждый из К выходов К-разрядного регистра сдвига соединен с соответствующим входом второго сумматора, выход N-ro разряда N-разрядного регистра сдвига соединен с вторыми входами второго блока вычитания и третьего сумматора первый вход первого блока вычитания. подключен к выходу первого разряда .N-разрядного регистра сдвига, первый вход и выход первого сумматора соответственно подключены к второму выходу делителя на К и входу делителя на два, вторые входы перв.ого сумма- тора и первого блока вычитания яв.ляются входами сигналов коэффициентов, тактовые входы К и N-разрядных регистров сдвига соединены между собой, а первым, вторым и третьим входами и первым и вторым выходами блока вычисления вероятности являются соответственно информационный вход К-разрядного регистра сдвига, объединенные тактовые входы К и Nразрядных регистров сдвига и второй вход делителя на п и выходы первого блока вычитания и делителя на два„

и блок памяти, выход которого соединен с вторым входом сумматора, при этом первым, вторым и третьим входам и выходом накапливающего сумматора соответственно являются второй вход сумматора, второй и третий входы блока памяти и выход сумматора.

с вторым входом счетчика, выход которого соединен с вторым входом

первого перемножителя, причем информационный и тактовый входы (.М+1)разрядного регистра сдвига и вход делителя являются соответственно первым, вторым и третьим входами блока коррекции, первым и вторым выходами которого соответственно являются выходы первого и второго перемножителей.

своим вторым входом с первым выходом генератора тактовых импульсов, второй выход которого соединен с входом Формирователя адреса, при этом входом и первым, вторым, третьим и четвертым выходами синхронизатора соответственно являются второй вход счетчика решений, второй выход генератора тактовых импульсов, выход формирователя адреса, выход блока сравнения

и выход счетчика периодов наблюдений.

Источники информации, принятые во внимание при экспертизе

36

k33

/г

sL

V

M M-tf

14:M

сриг.б

чг

j

т

в ПЯ... JL- JUL--.JL

«/

Фив.7

(Рив.в

Авторы

Даты

1982-10-30—Публикация

1981-04-30—Подача