теля, а четвертый, пятый, шестой, се гьмой и восьмой входы решающего блока, стробируюи ие входы первого, второго, третьего, четвертого и пято го регистров, управляющий вход коммутатора, вход установки режима и адресные входы оперативного запоминающего устройства, управляющие входы постоянного запоминающего устройства и квадратора соединены с соответствующими выходами синхронизатора.

3. Обнаружитель-измеритель по П.2, отличающийся тем, что решаюп1ий блок содержит последовательно соединенные коммутатор, первый регистр, блок сравнения, выход которого через элемент ИЛИ дополнительно соединен со стробирующим входом первого регистра, второй регистр

сумматор и третий регистр, выходы которого являются выходами решаклцего блока и соединены с вторыми входами сумматора, а также счетчик, выходы разрядов которого соединены с входами соответствующих разрядов второго регистра, причем вторые входы блока сравнения объединены с первыми входами коммутатора и являются первыми входами решающего блока, а вторые входы коммутатора, объединенные входы установки в ноль второго и третьего регистров, стробирующие входы третьего регистра и блока сравнения, входы счетчика, второй вход элемента ИЛИ и управлякиций вход коммутатора являются соответственно вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым входами решающего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой обнаружитель-измеритель частоты | 1986 |

|

SU1370584A2 |

| Цифровой обнаружитель-измеритель частоты | 1988 |

|

SU1597760A2 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Цифровой измеритель частоты и фазы гармонического сигнала | 1988 |

|

SU1626176A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Цифровой измеритель частоты | 1988 |

|

SU1684710A1 |

| Цифровой измеритель задержки | 1980 |

|

SU930219A2 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Следящий измеритель частоты | 1985 |

|

SU1298675A1 |

| Синтезатор частот | 1986 |

|

SU1478328A1 |

I. Устройство для автоподстройки частоты, содержащее последовательно соединенные цифровой синтезатор частоты, смеситель, усилитель промежуточной частоты и цифровой обнаружитель-измеритель частоты, а также блок опорных частот, соединенный с вторым входом цифрового синтезатора частоты, причем второй вход смесителя является сигнальным входом устройства, отличающееся тем, что, с целью повышения чувствительности, выход цифрового обнаружителяизмерителя частоты через сумматор подключен к первому входу цифрового синтезатора частоты, а второй выход блока опорных частот подсоединен к второму входу обнаружителя-измерител1| частоты, второй вход сумматора является входом установки прогнозируемого значения частоты. 2. Цифровой обнаружитель-измеритель частоты, содержа1ц;1й формирова- . тель импульсов нуль-пересечений. вход которого является первым входом обнаружителя-измерителя, постоянное запоминающее устройство, первый сумматор и последовательно соединен-г ные квадратор и решающий блок, выход которого является выходом обнаружите ля-измерителя, отличающийс я тем, что, с целью повышения чувствительности, в него введены по-, следовательно соединенные счетчикделитель и синхронизатО15, причем вход счетчика-делителя соединен с выходом фop шpoвaтeля импульсов нуль-пересечений, а второй вход синхронизатора соединен с вторым входом обнаружителя-измерителя, между вторым входом обнаружителя-измерителя и адресным входом постоянного запоминающего устройства последовательно включены введенные сЧетчик, первый .регистр, второй сумматор, коммутатор & К вторые разрядные входы которого соединены с выходами соответствующих разрядов счетчика, и второй регистр, о выходы разрядов которого дополнительно соединены с вторыми входами разряN0 дов второго сумматора, выходы постоsj янного запоминающего устройства че:о рез третий регистр соединены с перг: вым входом первого сумматора, между выходом первого сумматора и первым входом квадратора последовательно включены четвертый регистр, оперативное запоминающее устройство и пя тый регистр, разрядные выходы которого дополнительно соединены с вторым входом первого сумматора, причем второй и третий входы решающего ка являются соответственно входами , установки порога обнаружения и нача-, льной установки обнаружителя-измери-;

Изобретение относится к радиотехнике и может быть применено в частности, в радиоприемных устройствах, осуществляющих связь с подвижным объектом, для выделения .сигнала с из меняющейся во времени несущей частотой.

Известно устройство для автоматической подстройки частоты, содержащее последовательно управляемый гене ратор, смеситель, второй вход которого является сигнальным входом устройства, и селективный усилитель про межуточной частоты, эталонный генератор и цифровой измеритель периода. Перестройка частоты управляемого генератора этого устройства производится как по входу начальной установки частоты пропорционально соответствукйцему коду, так и по цепи обратной связи пропорционально разности заданного и измеренного значений длительности единичного периода колебания дромежуточной частоты. При этом стабилизируется значение промежуточной частоты С 1 .

Однако это устройство имеет низкук чувствительность: практически устройство работоспособно только при большом отношении сигнал/помеха на усилителя промежуточной частоты.

Наиболее близким к предложенному является устройство для автоподстройки частоты, содержащее последовательно соединенные цифровой синтезатор частоты, смеситель, второй вход которого является сигнальным входом устройства, усилитель промежуточной частоты и обнаружитель, а также блок опорных частот. Обнаружитель осуществляет переключение устройства из режима обнаружения входного сигнала, при котором цифровой синтезатор частоты управляется кодом начальной установвдг частоты, в режим отслеживания (подстройки) , при котором цифровой синтезатор частоты управляется принимаемым сигналом. Такое реше ние позволяет сузить полосу пропуска ния усилителя промежуточной часто ы 2 Д.

Однако обнаружитель известного устройства находится вне кольца автоподстройки частоты и только управляет режимом работы этого кольца. При захвате сигнала с быстро изменяющейся частотой за время перехода КЗ режима обнаружения сигнала в релсим слежения за его частотой последняя может сильно измениться, что вызывает необходимость некоторого расшире ния полосы УПЧ и соответствующего

понижения- чувствительности устройства.

Известен обнаружитель-измеритель частоты сигнала, содержащий последовательно соединенные генератор тактовых импульсов, реверсивный счетчик, запоминающий блок, блок формирования знака и преобразования числа, блок сумматоров, квадратор и решающий блок, причем вход разрешения считывания запоминающего блока соединен с выходом блока формирования импульсов нуль-пересечений, а знаковьт выход счетчика соединен с управляюпшм входом блока формирования знака .и преобразования числа С 3 .

Аппаратурный объем указанного устройства определяется,главным образом, объемом запоминающего блока и блока накапливающих сумматоров. Запоминающий блок должен хранить отсчеты 2М опорных сигналов, рассчитанные для значений времени te(0,T/2) с шагом 4t 1/f,- ) т.е. матрицу из 2М«Р двоичных чисел, где М 2FT число частотных каналов устройства: 2F - ширина полосы анализируемых часто Р - число импульсов тактово частоты , уменьшающихся на половин интервала наблюдения длительностью Т

Наиболее близким по технической сущности к предложенному является цифровой обнаружитель-измеритель частоты, содержащий формирователь импульсов нуль-пересечений, вход которого является первым входом обнаружителя, постоянное, запоминающее устройство, первый сумматор и последовательно .соединенные квадратор и решающий блок, выход которого является выходом обнаружителя 4.

Аппаратурный объем этого устройства несколько меньше чем у предыдущего за счет уменьшения информационной емкости постоянного зпоминающего устройства (шифратора). Однако блок накапливающих сумматоров также содержит 2М накапливающих сумматоров Велико количество постоянных запоминающих устройств и квадраторов (по К Сбщим недостатком известных обнаружителей-измерителей частоты является низкий коэффициент использования вычислительной аппаратуры и как следствие недостаточно высокая чувствительность при фиксированном ее объеме. Действительно, постоянные запоминающие устройства и накопи тельные сумматоры осуществляют по од

ному рабочему циклу после формирования каждого импульса нyль-nepcceчeний а квадраторы - по одному рабочему циклу в конце интервала наблюдения, в то время как период следования подлежащих обработке нуль-пересечений для многих практически важных случаев, (например, в устройстве для автоподстройки частоты с прогнозированием ее значения ) может значительно превьш1ать длительность рабочих циклов узлов обнаружителей-измерителей.

Цель изобретения - повышение чувствительности.

указанная цель достигается тем, ч5что в устройстве для автоподстройки частоты, содержащем последовательно соединенные цифровой синтезатор частоты, смеситель, второй вход которого является сигнальным входом устройства, усилитель промежуточной частоты и цифровой обнаружитель-измеритель частоты, а также блок опорных частот, соединенный с вторым входом цифрового синтезатора частоты,выход цифрово5го обнаружителя-измерителя частоты через сумматор подключен к первому входу цифрового синтезатора частоты, а второй выход блока опорных частот подсоединен к второму входу обнару0жителя-измерителя частоты, второй вход сумматора является входом установки прогнозируемого значения частоты.

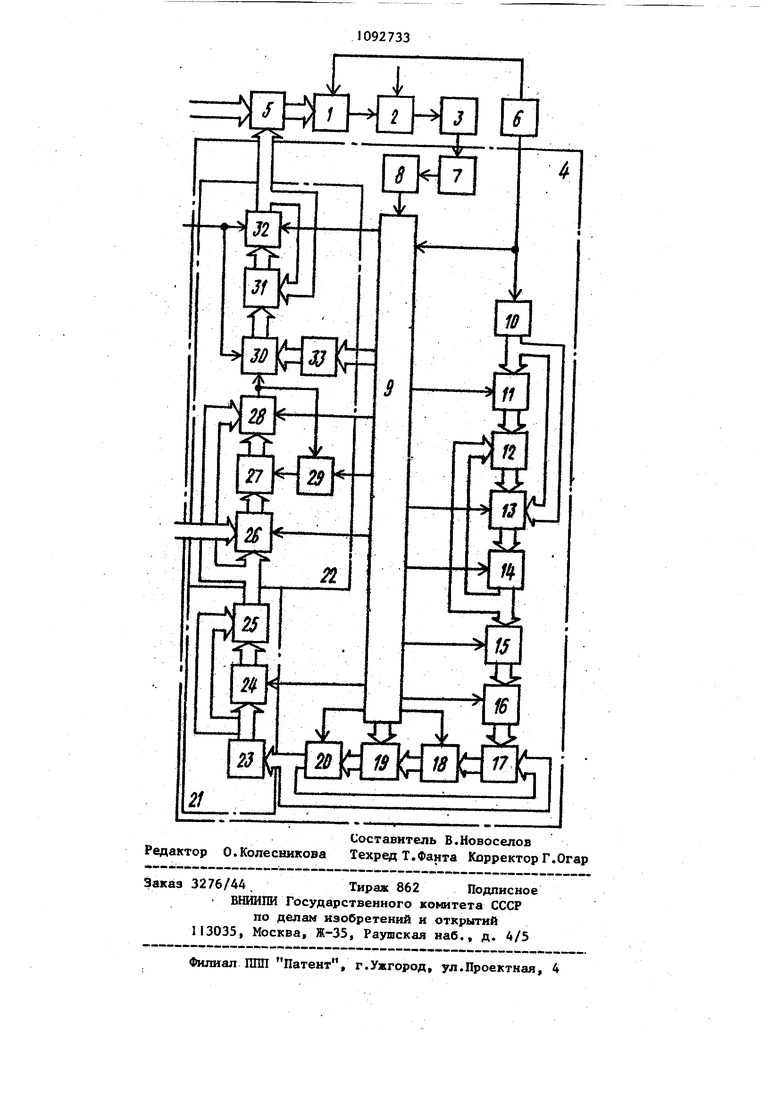

В цифровой обнаружитель-измери5 тель частоты, содержащий формирователь импульсов нуль-пересечений, вход которого является первым входом обнаружителя-измерителя, постоянное запоминанлцее устройство, первый сум0матор и последовательно соединенные квадратор и решающий блок, выход которого является выходом обнаружителя-измерителя, введены последовательно соединенные счетчик-делитель и синхронизатор, причем вход счетчика-делителя соединен с выходом формирователя импульсов нуль-пересечений, а второй вход синхронизатора соеди- . нен с вторым входом обнаружителяизмерителя, между вторым входом обнаружителя-измерителя и входом постоянного запоминающего устройства последовательно включены введенные счетчик, первый регистр, второй сумматор, коммутатор, вторые разрядные входы которого соединены с выходами соответствующих разрядов счетчика, и второй регистр, выходы разрядов которого дополнительно соедин ны с вторыми входами разрядов второ сумматора, выходы постоянного запоминающего устройства через третий регистр соединены с первым входом первого сумматора, между выходом первого сумматора и первым входом квадратора последовательно включены четвертый регистр, оперативное запоминаняцее устройство и пятый регистр, разрядные выходы которого соединены дополнительно с вторым входом первого сумматора, причем второй и третий входы решающего блока являются соответственно входами установки порога обнаружения и начальной установки обнаружителяизмерителя, а четвертый, пятый,шестой, седьмой и восьмой входы решающе го блока, стробирующие входы первого второго, третьего, четвертого и пятого регистров, управляющий вход коммутатора, вход установки режима и адресные входы оперативного запоми нающего устройства, управляющие вход постоянного запоминающего устройства и квадратора соединены с соответству ющими выходами синхронизатора. Решающий блок содержит последовательно соединенные коммутатор, первы регистр, блок сравнения, выход котор го через элемент ИЛИ соединен со стробирующим входом первого регистра второй регистр, сумматор и третий ре гистр, выходы которого являются выхо дами решакицего блока и соединены с вторыми входами сумматора, а также счетчик, выходы разрядов которого соединены с входами соответствующих разрядов второго регистра, причем вторые входы блока сравнения объединены с первыми входами коммутатора и являются первыми входами решающего блока, а вторые входы коммутатора, объединенные входы установки в ноль второго и третьего регистров, строби рующие входы третьего регистра и блока сравнения, входы счетчика, второй вход элемента ИЛИ и управляющий вход коммутатора являются соотве ственно .вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым входами решающего блока. В предложенном устройстве для автоподстройки частоты обнаружитель в отличие от прототипа включен непосредственно в кольцо автоподстройки частоты и кроме обнаружения выпол няет также и функции дискриминатора, т.е. измерителя разности фактического и прогнозируемого значения частоты сигнала, задаваемого в виде кода. Результат измерения разности частот непрерывно складывается с частотой целеуказания, а сумма используется для управления частотой цифрового синтезатора. Благодаря объединению в одном устройстве функции обнаружения и измерения частоты отсутствую ют потери времени на переход из режима обнаружения в режим слежения. Это, а также непрерывный ввод целеуказания, в том числе в режиме слеже ния, позволяет в значительной мере компенсировать изменение частоты сиг-нала и уменьшить полосу пропускания устройства автоподстройки частоты и цифровых фильтров обнаружителя, что приводит к увеличению чувствительности предлагаемого устройства по сравнению с прототипом. На чертеже представлена структур-t ная электрическая схема предложенных устройств для автоподстройки частоты и обнаружителя-измерителя частоты. Устройство для автоподстройки частоты содержит соединенные в кольцо цифровой синтезатор 1 частоты, смеситель 2, второй вход которого является сигнальным входом устройства, усилитель 3 промежуточной частоты, обнаружитель-измеритель частоты 4 и сумматор 5, второй вход которого является входом установки прогнозируемого значения частоты, а также блок опорных частот 6, первый и второй выходы которого соединены с вторыми входами цифрового синтезатора частоты и обнаружителя-измерителя частоты. Обнаружитель-измеритель частоты содержит последовательно соединенные формирователь 7 импульсов нульпересечений, вход которого является первым входом обнаружителя, -счетчик-делитель 8, синхронизатор 9, а также последовательно соединенные счетчик 10, вход которого является вторым входом обнаружителя, первый регистр 11, второй сумматор 12, коммутатор 13, второй регистр 14, постоянное запоминающее устройство 15, третий регистр 6, первый сумматор 17, четвертый регистр 18, оперативное запоминающее устройство 19, пятый регистр 20,квадратор 21 и решаюшдй

блок 22, причем квадратор содержит постоянное запоминакмдее устройство 23, регистр 2А и сумматор 25, а решакщий блок содержит между первым входом и выходом последовательно соединенные коммутатор 26, второй . вход которого является входом установки порога обнаружения, первый регистр 27, блок сравнения 28, выход которого дополнительно соединен череа элемент ИЛИ 29 со стробирующим . входом первого регистра, второй регистр 30, сумматор 31 и третий регистр 32, вход установки в ноль которого объединен с одноименным входом второго регистраи является входом начальной установки обнаружителя, а также счетчик 33.

Устройство -для автоподстройки частоты работает следующим образом.

Входной сигнал с несущей частотой f поступает на один вход смесителя 2, на второй вход которого подан гетеродинный сигнал с частотойf от цифрового синтезатора 1 частоты. Частота цифрового синтезатора 1 опре деляется частотой сигнала, поступающего с блока 6 опорных частот, и на этапе обнаружения входного сигнала кодом начальной установки частоты поступающим на вход управления цифрового синтезатора 1 частоты через сумматор 5. На другой вход сумматора 5 поступает с выхода обнаружителя- . измерителя частоты нулевой код, устанавливаемый, подачей импульса на вход начальной установки обнаружителя. .

Усилитель 3.промежуточной частоты выделяет из выходного сигнала смесителя гармоническую составляющую с разностной частотой ,ц } , причем «пце(-Ро + Р) , где о - номинальное значение промежуточной частоты, F - максимальная погрещность прогнозирования частоты входного сигнала.

Обнаружитель-измеритель 4 частоты эквивалентный параллельному соединению набора полосовых фильтров, полоса пропускания каждого из которых намного меньше, чем усилителя 3 промежуточной частоты, анализирует ш псодной сигнал последнего. Сравнивая выходной эффект фильтров с порогом обнаружения, установленным в виде кода на соответствукяцем входе и между собой, обнаружитель-измеритель принимает решение о наличии входного сигнала, а также дает оценку максимального правдоподобия f p значения промежуточной частоты i . Оценка погрешности прогнозирования частоты входного сигнала ij, -{Q , формируемая на выходе обнаружителя-измерителя в параллельном двоичном коде, складывается в первом сумматоре 5 с кодом прогнозируемого значения и изменяет частоту f р цифрового синтезатора 1 так, что (j. Таким образом осуществл яется обнаружение входного сигнала и слежение

5 за его частотой.

Обнаружитель-изпернтель частоты работает следующим образом.

Б момент пересечения сигналом промежуточной частоты нулевого уровня

0 с положительной производной формирог ватель 7 вырабатывает кратковременный импульс, поступающий на вход счетчика делителя 8, который осуществляет деление частоты следования импульсов

5 нуль-пересечений в целое число раз, определяемое отношением частоты полосе пропускания усилителя 3 проме.жуточной частоты. Прореженные импульсы нуль-пересечений .поступают на

0 первый вход синхронизатора 9, на второй вход которого подаются с второго выхода блока 6 опорных частот тактовые импульсы с частотой следования f-r Q + F , поступающие также на счетчик 10. В синхронизаторе 9 тактовые импульсы нуль-пересечений взаимно синхронизируются путем задержки последних на время, не превышающее шага квантования Д-t 1/... ..

Синхронизированный импульсы нуль-пересечений и другие выходные Импульсы синхронизатора 9 поступают в соответствующие моменты времени на входы узлов обнаружителя-измерителя, управ5ляя его работой.

Алгоритм обработки последовательности синхронизированных импульсов нуль-пересечений заключается, во-первых, в формировании на интервале наблюдения (О,Т) дискретного аналога

0 квадрата модуля комплексного корреляционного интеграла на дискретном множестве частот e( ) N

2

S

e

г i,M

(1)

(д -F| + (t - l)uf - опорные

частоты; М. 2Г/Л + ; Af « I/2Т - шаг дискретизации час тоты; N - количество синхронизо ванных импульсов нуль пересечений, поступающих в течение интерв ла наблюдения ОД ; tfl ( моменты поступленип синхронизированных иьшульсов нуль-пересе чений; , во-вторых, в нахождении частоты fnu при которой 2(гв J принимае наибольшее из превысивших порог обнаружения значение. Импульсы тактовой частоты f , поступающие на счетный вход счетчика 10, периодачески изменяют состояние его Р двоичных разрядов с периодом Тр Р 1/д . Определяемое состояниями разрядов счетчика JО число h 12.1 где п - число импульсов тактовой частоты, поступивших на вход счетчика за время .-t , связано с текущим значением фазы опорно го Сигнала sin 2 ITd-f t в соответствуЛ(ий момент времени соотношением ; 2лд 2Лп/2 2Л ; , Щ где 1 целое число. В момент времени t синхронизированный импульс нуль-пересечений разрешает запись в Р-разрядный первы регистр 11 состояния Р разрядов счет чика 10 - число п„ /2 --и через f, ;«. - и через коммутатор 13 в старшие разряды Рразрядного второго регистра 14 состо яния К младших разрядов счетчика 10 число гп„/2 , которое связано с :фазой 2 Jf(g-P) t опорного сигнала SM 2ff(о-РИ соотношением %-l n %/2 2Jrs. (3) где 5 - целое число, . l /fto-F). Выполнение соотношений (2 ) и (3) обеспечивается выбором соответствующих значений частот , ,. и разрядности Риг. Вслед за этим сигналом синхронизатора 9 переключается коммутатор 13 на пропускание выходного сигнала второго сумматора 12, а на вход стробирования второго регистра 14 подается от синхронизатора 9 серия из (м-О стробируюших импульсов. В результате многократного суммирования вторым сумматором 12 во втором 1 33JO регистре 14 последовательно фиксируются числа {tn п- Т- .. 7F-(lf} . , (41 где{х5 - дробная часть числа , связанные с фазой опорного сигнала соотношением 2f«n 2(V)n(- l ff«« , ,., где I - целое число. Послгдовательность М чисел (4 ) является адреса т, по которым из постоянного запоминающего устройства 15 поочередно считываются в третий регистр 16 и подаются на один вход сумматора 17 действительная cos2Я.ф и мнимая Sfn части функции ехр() , е:1;лГ . С выхода сумматора 17 через буферный четвертьй регистр 18 по соответствукндим 2М адресам оперативного, запоминающего устройства 19 записываются зультаты сложения n n./2 Vn. (У: взамен предыдущих сумм С f р,, и счиатнных из оперативного запоминакмцего устройства 19 в буферт . ный пятый регистр 20 и поданных на второй вход сумматора 17, причем 4,0 О, ( 1,М . Вычисления М чисел ( 4 | и соответствующих 2М сумм (6) заканчиваются до прихода следуюцего, ( импульса нуль-пересечений на синхронизатор 9, после которого весь цикл повторяется. Таким образом, практически сразу после прихода последнего на интервале наблюдения (ОД| N -го импульса нуль-пересечения в оперативном запоминающем устройстве записаны результаты накопления I - JL- :.N ,t,5,, , . После этого синхронизатор 9 переводит обнаружитель-измеритель частоты из режима накопления в режим поиска максимума модуля корреляционного интеграла: синхронизатор 9 записывает в счетчик 33 число и в регистр 27 через коммутатор 26 порога обнаружения, переключает коммутатор 26 на пропускание выходного сигнала сумматЬра 25 и считывает поочередно в регистр 20 резуп таты накопления Cg , е 1,м из оперативного запоминающего устрой ства 19 .Последние служат адресами,по которым из постоянного запоминающего устройства 23 считываются их квадраты, подаваемые на входы сумматора 25 непосредственно (sl) к через ре-«г гистр 24 (с| ) . Каждое из М форми руемьк на выходе сумматора 25 значение квадрата модуля корреляционного 2( ) s| j Cff интеграла сравнивается с содержимым регистра 2 в стробируемом блоке 28 сравнения. Если какое-либо значение Z(j) превосходит содержимое регистра 27, то стробирукяций импульс синхронизатора 9 проходит с входа иа кыход блока 23 сравнения и разрешает запись в регистр 27 через коммутатор 26 соответствующего значения () и в регистр 30 состояния счетчика Состояние счетчика 33 после кэж;дого такта сравнения увеличивается на 1, принимая, таким образом, ряд значений M-f . . . ---2- {е-(|--- , t,M , т.е от -F/4 при :-( до F/djE ПрмЬМ. Если входной сигнал устройства pfiK автоподЬтройки частоты отсутствует или его уровень ниже порогового, то ни одно из чисел 2(f t 1,М не превьшает порога обнаружения, на выходе блока 28 срав нения отсутствуют импульсы и регистр 30 сохраняет нулевое состояние При обнаружении сигнала в регистр 30 записано значение поправки ()/д.| в fl -f 1/л, соответствующее наибол пч о у .,, шему из М чисел ) г(ц) . . Ввод поправки в выходной регистр 32 осуществляется синхронизатором 9 после просмотра всех М чисел 2(fg)| длящегося столько времени, сколько один из N циклов вычислений сумм (61 т.е.. менее T/N «Т при . . Таким образом, обнаружитель-измери103 тель частоты эквивалентен параллельному соединению согласованных фильтров с полосой пропускания 2Д€ 1/Т каждого, перекрывающих диапазон 2F погрешности прогнозирования частоты входного сигнала, Отличительной особенностью предлагаемого обнаружителя-измерителя частоты является более эффективное по сравнению с известными устройствами использование функциональных узлов. Так, постоянное запоминающее устройся тво и первый сумматор осуществляют по 2М 1 рабочих циклов после каждого обрабатываемого импульса иульпересечения, аквадратор - М рабочих циклов в конце каждого интервала наблюдения. Благодаря этому, увеличивая объ.ем ( емкость ОЗУ 2М ), разрядность сумматоров и ОЗУ предлагаемого обнаружителя-измерителя до объема устройства-прототипа, можно увеличить время Т накопления сигнала в устройстве, а значит и его чувствительность. Чувствительность предлагаемого устройства для автоподстройки частоты ограничивается требованием превышенияуровнем сигнала уровня помехи в отличие от известного устройства не в полосе пропускания усилителя промежуточной частоты, которая не может быть меньше 2F, а в полосе 2Л ( и следовательно, при М 1 чувствительность пред«тагаемого устройства и надежность вхождения в синхронизм значительно выше известного. Поскольку N , то при М время обнаружения сигнала и перехода в режим слежения Т + T/N Т является практически минимально возможным при реализации требуемой чувствительности устройства/ Испытания, проведенные на опытных образцах предлагаемого устройства с параметрами:{, кГц, 5 кГц, М 128, Т 12,5 мс, 2Р дали следующие результаты.Чувствительность предлагаемого ус-тройства, характериэуемая отношением мощности полезного сигнала к мощности помехи, равна примерно I2+-I3 дБ в полосе 2д «iSO in при вероятности 0,9 обнаружения сигнала и перехода в режим слежения за время 12,5 мс. ,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для переноскии КАНТОВКи Тигля | 1972 |

|

SU835948A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-05-15—Публикация

1982-01-18—Подача