(54) СТАРТСТОПНЫЙ ЭЛЕКТРОННЫЙ ПРИЕМНИК

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухкратная стартстопно-синхронная система передачи дискретной информации | 1988 |

|

SU1570018A1 |

| Стартстопное передающее устройство | 1980 |

|

SU919141A1 |

| Стартстопный электронный регенератор | 1973 |

|

SU508957A1 |

| Устройство для формированияиСпыТАТЕльНОгО TEKCTA | 1979 |

|

SU803118A1 |

| Устройство для фазирования электронного стартстопного телеграфного приемника | 1987 |

|

SU1518904A1 |

| Устройство для передачи дискретной информации | 1975 |

|

SU588654A1 |

| Устройство для приема и регенерации дискретной информации | 1977 |

|

SU650232A1 |

| Устройство для фазирования электронного стартстопного регенератора | 1982 |

|

SU1073896A1 |

| ПРИБОР ДЛЯ ИЗМЕРЕНИЯ СТАРТСТОПНЫХ ТЕЛЕГРАФНЫХИСКАЖЕНИЙ | 1969 |

|

SU248748A1 |

| Устройство для защиты от ложного старта | 1980 |

|

SU907848A1 |

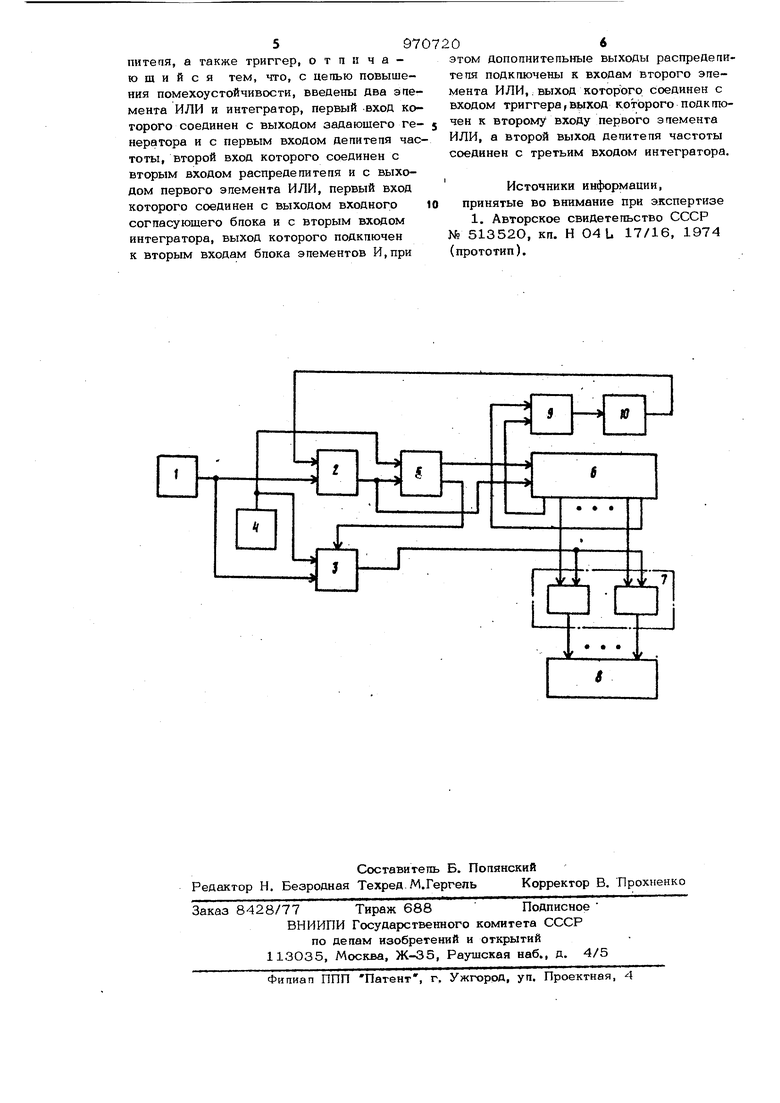

Изобретение относится к электросвязи. Известен стартстопный электронный приемник, содержащий входной согласующий блок, задающий генератор и последовательно соединенные делитель частоты и распределитель, выходы которого подключены к первым входам блока элементов И, выходы которого соединены со входами накопителя, а также триггерLlJ. Однако в известном приемнике недостаточная помехоустойчивость. Цепь изобретения - повышение помехо устойчивости. Указанная цепь дос-гагается тем, что в стартстопный электронный приемник, содержащий выходной согласующий блок, задающий генератор и последовательно соединенные делитель частоты и распре.делитепь, выходы которого подключены к первым входам блока элементов И, выходы которого соединены со входами накопителя, а также триггер, введены два эл мента ИЛИ и интегратор, первь1й вход ко торого соединен с выходом задающего генератора и с первым входом делителя частоты, второй вход которого соединен со вторым входом распределителя и с выходом первого элемента ИЛИ, первый вход которого соединен с выходом входного согласующего блока и со вторым входом интегратора, выход которого подключен ко вторым входам блока элементов И, при этом Дополнительные выходы распределителя подключены ко входам второго элемента ИЛИ, выход которого соединен со входом триггера, выход которого подключен ко второму входу первого элемента ИЛИ, а второй выход делителя частоты соединен с третьим входом интегратора. На чертеже изображена структурная электрическая схема предлагаемого устройства. Устройство содержит входной согласующий блок 1, элемент ИЛИ 2, интегратор 3, задающий генератор 4, делитель 5 частоты, распределитель 6, блок 7 элементов И, накопитель 8, эпемент ИЛИ &, триггер 10. Устройство работает следующим образом. При приеме стартового симвопа сигнап с выхода входного согпасуклцего блока 1 поступает через эпемент ИЛИ 2 на установочный вход делитепя 5 частоты, ка счетный Екод которого поступают импульсы опорной частоты с выхода задающего генератора 4. Стартовый символ устанавливает депитель 5 частоты в режим счета, и он начинает считать входные импульсы. Если длительность стартового сигнала будет соответствовать критерию обнаружения сигнала, то на первом выходе делителя частоты 5 появится импульс, который поступит на первый вход распределителя 6, Сигнал с выхода элемента ИЛИ 2 также определяет режим работы распределителя 6, как и делитепя 5 частоты. Если сигнал, соответствукщий стар товому символу, будет иметь длительност меньщую, чем 112., где Т - длительность элементарного символа, то на первом выходе делитепя 5 частоты импульс не появится, а снятие этого сигнала с ус тановочного входа делителя 5 частоты ус танавливает его и распределитель 6 в О. Устройство готово к,,приему следующего стартового символа. образом устройство осуществляет защиту от ложного старта (защиту от действия помехи, имеющей длительность, меньщую чем ). Если стартс 1вый сигнал имеет длительность больщую, чем , то первый импупьс, поступивщий с выхода делителя 5 частоты на вход распределителя 6, появится на первом выходе распределителя 6 и через элемент ИЛИ 9 он поступит на вход триггера 10. Триггер 10 срабатывает, сигнал с его выхода поступает на первый вход элемента ИЛИ 2 и Даль- ще на установочный вход делителя 5 частоты. Этот сигнал удерживает делитель 5 частоты в режиме счета, который переходит в циклический режим работы. Период следования импульсов с первого выхода делителя 5 частоты равсгн длительности Т. Эти импульсы сдвинуты относительно rpi&HHtt элементарных посылок на величину, которая равна длительности дискретного интегрирования стартового символа. Это -время t-i (О,5-О,7 )Т Импульс, соответствующий концу принима емого знака (соответствующий стоповой посылке принимаемой стартстопной комби нации), поступает с выхода распределителя 6 на второй вход элемента ИЛИ 9 и далее на вход триггера 10, который этим импульсом возвращается в исходное состояннё. Делитель 5 частоты и распредепитель 6 устанавливаются в нулевое состояние, и устройство готово к приему следующей кодовой комбинации. Во время приема кодовой комбинации на втором выходе делителя 5 частоты появляются импугаьсы, сдвинутые относительно передней границы элементарного с мвола на время , 0,9. . Эти импульсы поступают на третий вход интегратора 3, на первый вход которого поступает опорная частота с выхода задающего генератора 4, а на второй вход поступает принимаемая информация с входного согласующего блока 1, Интегратор 3 осуществляет дискретное интегрирование принимаемой информации, подсчитывая копичество импульсов с задающего генератора 4 во время приема посылок единичного уровня. Если подсчитанное количество импульсов соответствует длительности действия единичной элементарной посылки t 5 0,5Т, то на выходе интегратора 3 появляется единичный уровень сигнала. Поступающие на третий вход интегратора 3 импульсы со второго выхода распределителя 6 служат для обнуления счетчика интегратора 3 в конце приема элементарной посылки. С выхода интегратора 3 сигналы поступают на вторые входы блока 7 элементов И, на первые входы которых поступают стробирующие импульсы с выходов распределителя 6. Интегрированные значения символов принимаемой стартстопной комбинации записываются через блок 7 элементов И в накопитель 8. Таким образом, в предлагаемом устрюйстве осуществляется защита от ложного старта, т.е. защита от воздействия импульсной помехи или прерывания канала связи, время действия которых -fc а также дискретное интегрирование эле- ментарных символов принимаемой комбинации. Все это позволяет повысить помехоустойчивость приема. Формула изобретения Стартстопный электронный приемник, содержащий входной согласующий блок, задающий генератор и последовательно соединенные делитель частоты и распределитель, выходы которого подключены к первым входам блока элементов И, выходы которого соединены с входами накопитепя, а также триггер, о т i ч а ю ш и и с я тем, что, с цепью повышения помехоустойчивости, введены два эпемента ИЛИ и интегратор, первый вход которого соединен с выходом задающего генератора и с первым входом депитепя частоты, второй вход которого соединен с вторым входом распредепитепя и с выходом первого эпемента ИЛИ, первый вход которого соединен с выходом входного согласующего бпока и с вторым входом интегратора, выход которого подкпючен к вторым входам бпока эпементов И, при

этом допопнитепьные выходы распреДепитепя подкпючены к входам второго эпемента ИЛИ,. выход которого соединен с входом триггера, выход которого под к точен к второму входу первого эпемента ИЛИ, а Второй выход депитепя частоты соединен с третьим входом интегратора,

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-10-30—Публикация

1981-04-09—Подача