зьюает формирование на его выходе сиг-25 тановке первого регистра 33 сдвига в

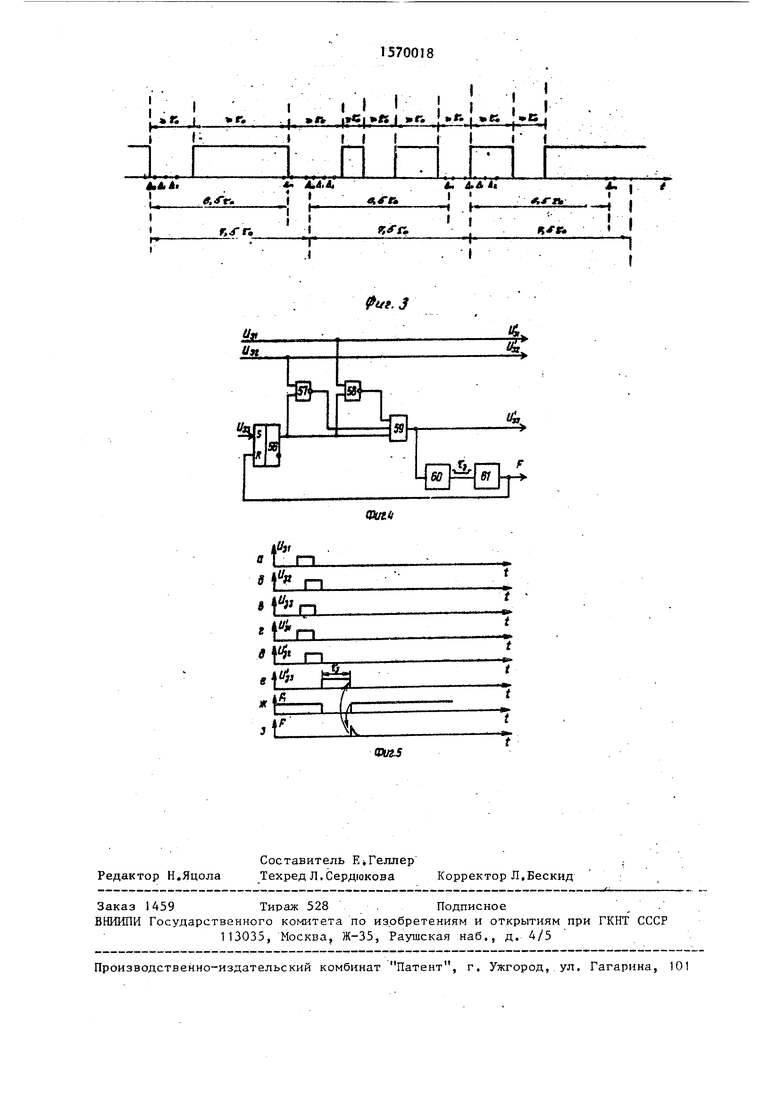

нала U -3 записи новой информации в накопитель-распределитель 4 через преобразователь 3 кода,При поступлении на тактовый вход регистра 5 сдвига импульса, соответствующего точке 7,5 00 (конец синхронного цикла), сигналом на выходе К регистра 5 сдвига этот регистр 5 устанавливается в исходное состояние и устанавливает по второму входу триггер 6 цикла, что означает начало нового синхронного цикла передачи.

Различие тактовых частот накопителя-распределителя 4 регистра 5 сдвига предусмотрено на случай, если имеет значение, при котором на интервале Т 7, укладывается нецелое число таких зон и В этом случае тактовая частота регистра 5 сдвиг f 1/Д для формирования сигнала на выходе К точно в точке 7,5 2 ,

О

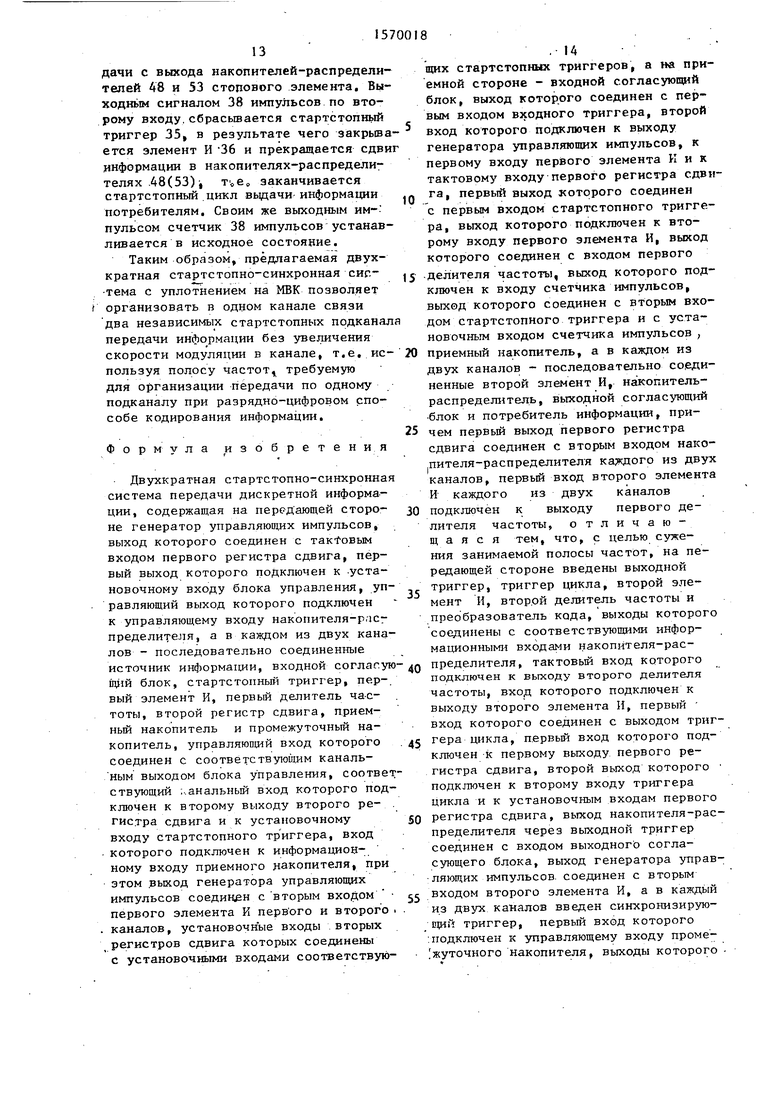

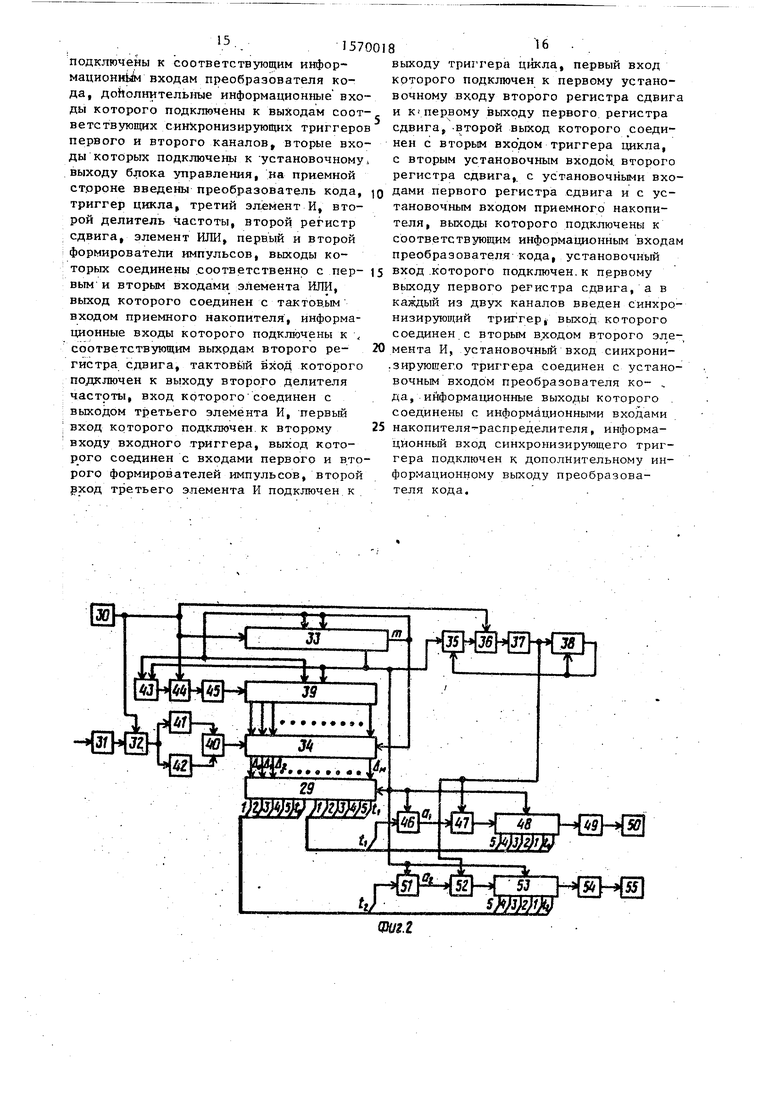

Информация с канала связи через входной согласующий блок 31, согласующий канал с системой по уровню, поступает на входной триггер 32, где осуществляется временная привязка фронтов принимаемой информации к ге- .нератору 30 управляющих импульсов. Вследствие переменного числа ЗМ на интервале цикла т все переходы, включая стартовый, могут происходить как из нуля в единицу, так и наоборот (фиг.З), Это означает, что приемная сторона должна извлекать инфорисходное состояние, что соответствует началу нового синхронного цикла, по второму входу устанавливается триггер 43 цикла и устанавливается в исходное состояние второй регистр 39 сдвига, С этого момента сигналом с выхода триггера 43 цикла разрешается прохождение импульсов от генератора 30 управляющих импульсов через элемент И 44 на делитель 45 частоты, с выхода которого на тактовый вход второго per гистра 39 сдвига поступают импульсы с частотой Причины различия тактовых частот первого 33 и второго 39 регистров сдвига те же, что и для третьего регистра 5 сдвига и накопителя-распределителя 4 передающей стороны. Количество выходов регистра 39 сдвига, подаваемых на приемный

накопитель 34, равно (М+1), Длительность поочередного нахождения сигнала на каждом из (М+1) выходе второго регистра 39 сдвига равна Д. Выходы второго регистра 39 сдвига заведены

на входы приемного накопителя 34, на тактовый вход которого поступают импульсы с элемента ИЛИ 40 с помощью которых производится поочеред

ная регистрация всех зон и .в приемном накопителе 34, При этом в ячейки, соответствующие зонам д , в которых был обнаружен переход, записьюа- ется единица. Таким образом, инфор- маци, записываемая в приемный нако11

12

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Система передачи дискретной информации | 1987 |

|

SU1518886A1 |

| Система передачи дискретной информации с исправлением ошибок | 1985 |

|

SU1283990A1 |

| Система передачи дискретной информации с решающей обратной связью | 1983 |

|

SU1111258A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| МНОГОКАНАЛЬНАЯ АППАРАТУРА ПЕРЕДАЧИ ДВОИЧНЫХСИГНАЛОВ | 1971 |

|

SU313302A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396722C1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

Изобретение относится к телеграфии. Цель изобретения - сужение занимаемой полосы частот при передаче одного и того же объема информации. Система содержит преобразователь 3 кода, источники 11 и 20 информации, синхронизирующие триггеры 18 и 27 и промежуточные накопители 19 и 28. Уплотнение подканалов происходит за счет преобразования преобразователем 3 кода двух комбинаций простого кода от независимых каналов в одну комбинацию многопозиционного временного кода (МВК) и передачи ее синхронным способом за время, не превышающее длительность стартстопного цикла подканалов и со скоростью B модуляции, равной скорости Bо источников 11 и 20 информации. В зависимости от состояния ячеек промежуточных накопителей 19 и 28 и триггеров 18 и 27 в синхронный канал может передаваться одна из 1089 комбинаций МВК, информация в которой заложена: в наличии/отсутствии стартового перехода в зоне регистрации

количестве переходов на интервале синхронного цикла

местах расположения переходов относительно начальной точки синхронного цикла. 5 ил.

питель 34 будет соответствовать информации, считываемой с накопителя-распределителя. 4 при передаче.

Через интервал времени 6,5f с момента начала .синхронного цикла приема сигналом с первого выхода перво- . го регистра 33 сдвига по первому вхо« ду сбрасывается триггер 43 цикла, вследствие чего прекращается сдвиг

информация (разряд t в нулевом Состоянии ), на выходе накопителя-распределителя 48(53) появляется стартовый переход.

Одновременно с записью информации в накопители-распределители 48 и 53 и синхронизирующие триггеры 46 и 51 ; устанавливается стартстопный триггер

информации во втором регистре 39 сдви- 35 что разрешает прохождение импулы га; обнуляется второй регистр 39 сдви- сов с генератора 30 управляющих им- пульсов через элемент К 36 на делитель 37 частоты, с выхода которого

га; разрешается передача информации

пульсов через элемент К 36 на делитель 37 частоты, с выхода которого

из приемного накопителя 34 через- преобразователь 29 кода в накопители-рас-,5 импульсы с частотой поступают пределители 48 и 53 и синхронизирую- на первые входы элементов И 47 и 52. щие триггеры 46 и 51 обоих подкана- Эти элементы И 47 и 52 будут Открыты лов; по первому входу устанавливается стартостопный триггер 35, что озна- чЈет начало стартостопного цикла пере- 20 щих им подканалов будут в нулевом со- дачи информации потребителям 50 и 55 стоянии (используются инверсные выходы синхронизирующих триггеров 46 и 51). Если элемент И 47(52) оказылишь в том случае, если синхронизирующие триггеры 46 и 51 соответствую35

информации.

А при поступлении на д-актовый вход первого регистра 33 сдвига импульса, соответствующего точке 7, (концу синхронного цикла) сигналом с выхода первого регистра 33 сдвига этот регистр 33 и второй регистр 39 сдвига устанавливаются в исходное состояние, обнуляются ячейки приемного накопи- аеля 34, а также устанавливается по второму входу триггер 43 цикла, что означает начало нового синхронного цикла приема.

Преобразователь 2° кода приема выполняет преобразование информации, fобратное преобразователю 3 кода передачи, т.е. из (М+1)-разрядной комбинации формирует две 6-разрядные (пять элементов МТК-2 плюс флаг) и предетав-дд ляет собой ППЗУ с (М+1)-разрядным форматом адреса и 12-разрядным форматом данных

Каждая из двух 6-разрядных групп выходов преобразователя 29 кода заве- д§ дена на информационные первые входы накопителя-распределителя 48(53 и вход синхронизирующего триггера 46(51) соответствующего канала, на вторые входы которых поступает сигнал с первого выхода первого регистра 33 сдвига (соответствующего точке 6,5). Флаговый разряд t каждого подканала с выхода преобразователя 29 кода помимо записи в синхронизирующий триггер 46(51) записывается и в выходную ячейку накопителя-распределителя 48(53) и в случае, если для данного подканала поступила новая

вается открытым, то тактовые импуль-1 25 сы частоты ,, поступают на тактовый вход накопителя-распределителя 48(53) соответствующего ему канала. Накопитель-распределитель 48(53) пред ставляет собой регистр сдвига на шест -0 ячеек с коммутатором для предварительной записи инверсным R-входам. Таким образом, если флаговый разряд канала принят нулевым, с выхода накопителя-распределителя 48(53) данного канала через выходной согласующий блок 49(54) к потребителю информации 50(55) поступает стартстопная комбинация со скоростью В противном случае на выходе данного канала поддерживается стоповая полярность. Выходной согласующий блок 49(54) служит для согласования системы с потребителем информации 50(55) по уровню.

На вход последней ячейки накопителя-распределителя 48(53) постоянно подан сигнал логической единицы, которая по мере сдвига информации заполняет все ячейки накопителя-распределителя 48(53) вследствие чего через 50 время 6 Ј с момента начала старт- стопного цикла накопитель-распределитель готов к приему новой информации.

Импульсы с делителя 37 частоты noes ступают также на вход счетчика 38 импульсов, который вырабатывает выходной сигнал при поступлении с делителя 37 частоты шестого импульса частоты f l/ 00, что соответствует началу выинформация (разряд t в нулевом Состоянии ), на выходе накопителя-распределителя 48(53) появляется стартовый переход.

Одновременно с записью информации в накопители-распределители 48 и 53 и синхронизирующие триггеры 46 и 51 ; устанавливается стартстопный триггер

35 что разрешает прохождение импулы сов с генератора 30 управляющих им-

пульсов через элемент К 36 на делитель 37 частоты, с выхода которого

импульсы с частотой поступаю на первые входы элементов И 47 и 52. Эти элементы И 47 и 52 будут Открыты щих им подканалов будут в нулевом со стоянии (используются инверсные выхо ды синхронизирующих триггеров 46 и 51). Если элемент И 47(52) оказыимпульсы с частотой поступают на первые входы элементов И 47 и 52. Эти элементы И 47 и 52 будут Открыты щих им подканалов будут в нулевом со- стоянии (используются инверсные выходы синхронизирующих триггеров 46 и 51). Если элемент И 47(52) оказылишь в том случае, если синхронизирующие триггеры 46 и 51 соответствую

вается открытым, то тактовые импуль-1 , сы частоты ,, поступают на тактовый вход накопителя-распределителя 48(53) соответствующего ему канала. Накопитель-распределитель 48(53) представляет собой регистр сдвига на шесть ячеек с коммутатором для предварительной записи инверсным R-входам. Таким образом, если флаговый разряд канала принят нулевым, с выхода накопителя-распределителя 48(53) данного канала через выходной согласующий блок 49(54) к потребителю информации 50(55) поступает стартстопная комбинация со скоростью В противном случае на выходе данного канала поддерживается стоповая полярность. Выходной согласующий блок 49(54) служит для согласования системы с потребителем информации 50(55) по уровню.

На вход последней ячейки накопителя-распределителя 48(53) постоянно подан сигнал логической единицы, которая по мере сдвига информации заполняет все ячейки накопителя-распределителя 48(53) вследствие чего через время 6 Ј с момента начала старт- стопного цикла накопитель-распределитель готов к приему новой информации.

Импульсы с делителя 37 частоты noступают также на вход счетчика 38 импульсов, который вырабатывает выходной сигнал при поступлении с делителя 37 частоты шестого импульса частоты f l/ 00, что соответствует началу выдачи с выхода накопителей-распределителей 48 и 53 стопового элемента. Выходным сигналом 38 импульсов по второму входу сбрасьюается стартстопный триггер 35, в результате чего закрыва- ется элемент И 36 и прекращается сдвиг информации в накопителях-распределителях 48(53), т0е„ заканчивается стартстопный цикл выдачи информации tft потребителям. Своим же выходным импульсом счетчик 38 импульсов устанавливается в исходное состояние.

Таким образом, предлагаемая двухкратная стартстопно-синхронная сиг- . 5 тема с уплотнением на МВК позволяет организовать в одном канале связи два независимых стартстопных подканала передачи информации без увеличения скорости модуляции в канале, т.е. ис- 20 пользуя полосу частот требуемую для организации передачи по одному подканалу при разрядно-цифровом способе кодирования информации.

25 Формула изобретения

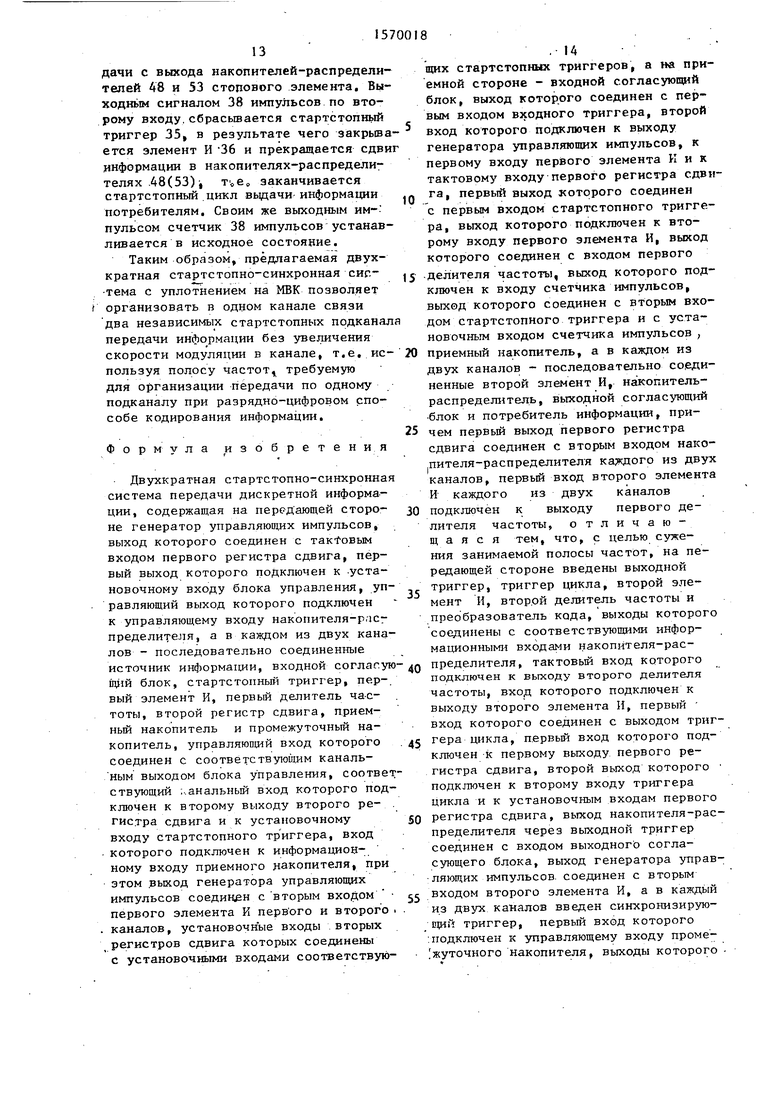

Двухкратная стартстопно-синхронная система передачи дискретной информации, содержащая на передающей сторо- 30 не генератор управляющих импульсов, выход которого соединен с тактовым входом первого регистра сдвига, первый выход которого подключен к установочному входу блока управления, управляющий выход которого подключен к управляющему входу накопителя-г ic- пределителя, а в каждом из двух каналов - последовательно соединенные источник информации, входной согласую- д щий блок, стартстопный триггер, первый элемент И, первый делитель частоты, второй регистр сдвига, приемный накопитель и промежуточный накопитель, управляющий вход которого 45 соединен с соответствующим канальным выходом блока управления, соответствующий анальный вход которого подключен к второму выходу второго регистра сдвига и к установочному 50 входу стартстопного триггера, вход которого подключен к информационному входу приемного накопителя, при этом выход генератора управляющих импульсов соединен с вторым входом первого элемента К первого и второго . каналов, установочные входы вторых регистров сдвига которых соединены с установочными входами соответствую35

ft

5 0

5

0 д 5

5

щих стартстопных триггеров, а на приемной стороне - входной согласующий блок, выход которого соединен с первым входом входного триггера, второй вход которого подключен к выходу генератора управляющих импульсов, к первому входу первого элемента Кик тактовому входу первого регистра сдвига, первый выход которого соединен с первым входом стартстопного триггера, выход которого подключен к второму входу первого элемента И, выход которого соединен с входом первого делителя частоты, выход которого подключен к входу счетчика импульсов, выход которого соединен с вторым входом стартстопного триггера и с установочным входом счетчика импульсов приемный накопитель, а в каждом из двух каналов - последовательно соединенные второй элемент И, накопитель- распределитель, выходной согласующий блок и потребитель информации, причем первый выход первого регистра сдвига соединен с вторым входом накопителя-распределителя каждого из двух каналов, первый вход второго элемента И каждого из двух каналов подключен к выходу первого делителя частоты, отличающаяся тем, что, с целью сужения занимаемой полосы частот, на передающей стороне введены выходной триггер, триггер цикла, второй эпе- мент И, второй делитель частоты и преобразователь кода, выходы которого соединены с соответствующими информационными входами накопителя-распределителя, тактовый вход которого подключен к выходу второго делителя частоты, вход которого подключен к выходу второго элемента И, первый вход которого соединен с выходом триггера цикла, первьй вход которо о подключен к первому выходу первого регистра сдвига, второй выход которого подключен к второму входу триггера цикла и к установочным входам первого регистра сдвига, выход накопителя-распределителя через выходной триггер соединен с входом выходного согласующего блока, выход генератора управляющих импульсов соединен с вторым входом второго элемента И, а в каждый из двух каналов введен синхронизирующий триггер, первый вход которого подключен к управляющему входу промежуточного накопителя, выходы которого

подключены к соответствующим инфор- мационййм входам преобразователя кода, дополнительные информационные входы которого подключены к выходам соответствующих синхронизирующих триггеров первого и второго каналовt вторые входы которых подключены к установочному выходу блока управления, на приемной стороне введены преобразователь кода, триггер цикла, третий элемент И, второй делитель частоты, второй регистр

сдвига, элемент ИЛИ, первый и второй формирователи импульсов, выходы которых соединены соответственно с пер- вым и вторым входами элемента ИЛИ, выход которого соединен с тактовым входом приемного накопителя, информационные входы которого подключены к ., соответствующим выходам второго регистра сдвига, тактовый вход которого подключен к выходу второго делителя частоты, вход которого соединен с выходом третьего элемента И, первый вход которого подключен к второму входу входного триггера, выход которого соединен с входами первого и второго формирователей импульсов, второй вход третьего эпемента И подключен к

33

JJ

ЈЈ

39

J4

еВЕЬ

29

ШШЖШР.

5

выходу триггера цикла, первый вход которого подключен к первому установочному входу второго регистра сдвига и К первому выходу первого регистра сдвига, второй выход которого соеди- нен с вторым входом триггера цикла, с вторым установочным входом второго регистра сдвига, с установочными входами первого регистра сдвига и с установочным входом приемного накопителя, выходы которого подключены к соответствующим информационным входам преобразователя кода, установочный вход которого подключен к первому выходу первого регистра сдвига, а в каждый из двух каналов введен синхронизирующий триггер, выход которого соединен с вторым входом второго эле0 мента И, установочный вход синхрони- .зируюшего триггера соединен с установочным входом преобразователя ко- , да, информационные выходы которого соединены с информационными входами накопителя-распределителя, информационный вход синхронизирующего триггера подключен к дополнительному информационному выходу преобразователя кода.

5

WMM

U

fat.j

JL

| Шляпоберский В.И | |||

| Элементы дискретных систем связи | |||

| - М.: МО СССР, 1962, с | |||

| ПЕЧНОЙ ЖЕЛЕЗНЫЙ РУКАВ (ТРУБА) | 1920 |

|

SU199A1 |

Авторы

Даты

1990-06-07—Публикация

1988-08-18—Подача