(54) МНОГОУРОВНЕВЫЙ СУММАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор дельта-модулятора | 1986 |

|

SU1352655A1 |

| Согласующее устройство | 1986 |

|

SU1348995A1 |

| Согласующее устройство | 1986 |

|

SU1316081A1 |

| Четырехуровневый одноразрядный сумматор | 1982 |

|

SU1095174A1 |

| Согласующее устройство | 1985 |

|

SU1262719A1 |

| Элемент инжекционной логики со стабилизацией тока питания | 1983 |

|

SU1088128A1 |

| Компандер дельта-модулятора | 1983 |

|

SU1200423A1 |

| МНОГОЗНАЧНЫЙ СУММАТОР ПО МОДУЛЮ k | 2014 |

|

RU2546082C1 |

| Инжекционный сумматор | 1988 |

|

SU1539992A1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ "СУММАТОР ПО МОДУЛЮ ТРИ" | 2020 |

|

RU2725165C1 |

,.,.; .V1 -: .

Изобретение от всювтся к мякрсюлект роввке, а вменно к внтегральвым схемам на мвогоуррвцевых элементах с внясс ш отым кщтанвем, v может наЯггй првме вение при соэдаспя БИС.

Извеогвы ковструкшкв егеотурб1 с вых сумматоров ва мнагоколлейторвых ИТП влемевтах fll.

Недостатками сумматора являются вкэквб помехоустойчивость, быст родействие, большая погрешность в высокие требоваввя к величвве ковффишюви .та усипевия травэистора.

Наиболее блвзквм к предлагаемому ;являетса мвогоуровневый сумматор, состоящий из нескольких вкодвых токовых зеркал с двумя выходами каждое, выхоовогр TtjKOBoro зеркала, порогового элемевтв с выходами и источника то-, ка, подключенвого к первому выходу порогового элемевта, первые выходы входиых токошх аеркал соедивешл с

входом выходного токового зеркала, выход которого подключен к первой Euxotbной шнне, вторые выходы входных токовых зеркал соединены с входом порогове го элемента, второй выход которого подключен к второй выходной шнне Г21.

Недостатками известного многоуровневого сумматора являются низкие помехоустойч1шость, быстродействие и большая погрешность,. обухэтовленные тем, что

10 выходное токовое зеркало работает в большом динамическом диапазоне токов, что ограничивает использование максимальной :величины едт1ичного уровня то15ка.

Цель изобретения - увеличение помехоустойчивости, стродействия и умеш шение погрешности многоуровневого сум матора.

20

Поставленная цель достигается тем, что многоуровневый сумматор, состоящей из нескольких входных токовых зеркал с выходами каждое, выходного токо3S74вого зеркала, порогового элементе с двуи ;мя выходами в всточшша тсжа, поднл10 ченного к первому выходу порогового элемента, выходы ш:одкых токовых зеркал соедивеня с входом выходного токового , крторого подключен к первой выходной шине, вто- рые выходы входных токовых зеркал соединены с входом порогового эдемента,

второй выход которого подключен к 10пели 27 ток величиной в 4 единипы. На

рой выходной шине, дополнительно срдер-выходе суммы 5 вытекает ток на 4

жит транзистор p-fi-p типа 1C обшей ба-единицы меньщф, чем сумма входных

ЗОЙ, эмиттер которого соединен с первымтоков Х,,У и X

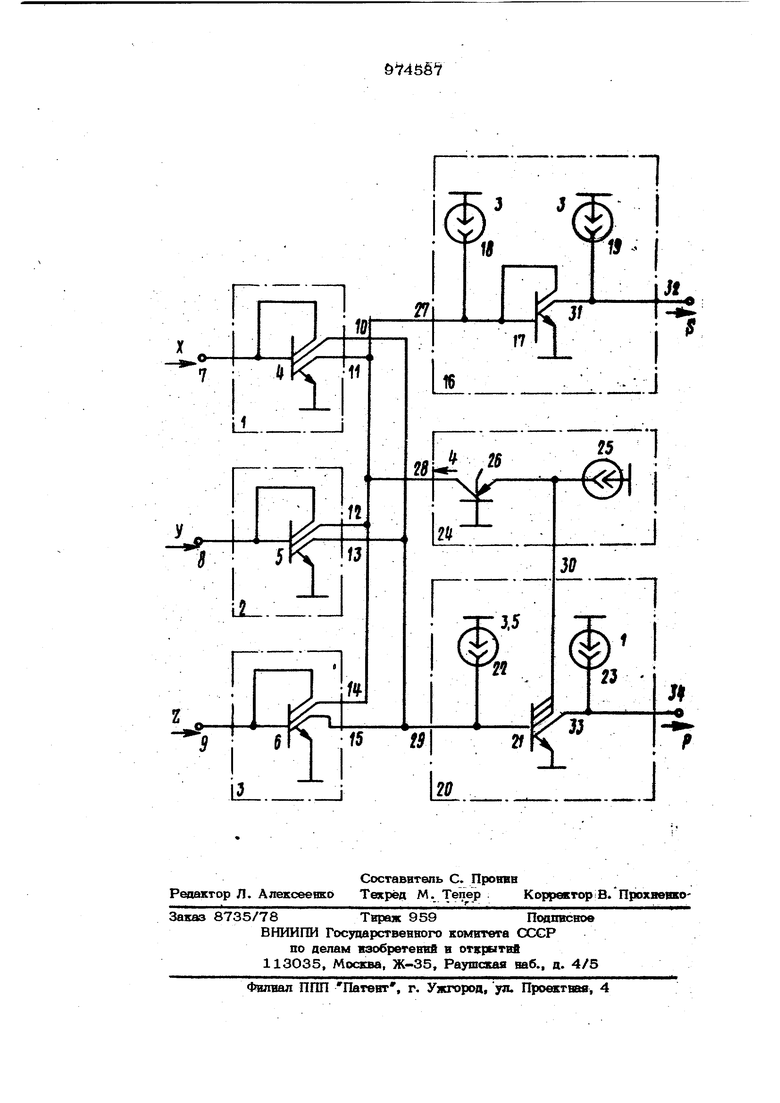

выходом порогового элемента, а коялек- тор с входом выходного токового зер- 15 ,. На чертеже показана принципиальная схема четырехуровневого инжекционного сумматора. Сумматор содержит входные токовые зеркала 1,2 и 3 на И Л транзисторах )4,5 и 6 с входами 7,8 и 9 и выходами Ю и 11, 12 и 13 и 14 и 15 соответс енко выходное токовое зеркало 16 на И Л транзисторе 17 и с источниками 18 и 19 тока в базовой и коллекторной цепях соответственно, пороговый элемент 20на двухколлекторнс транзистор 21с источниками 22 и 23 тока в базовой и второй коллекторной цепях соот. ветственно, источник 24 тока, состоятций из источника 25 постоянного тока и трав зистора 26 с общей базой. В1Ё 1Хсщы 11, 12, и 14 входных токовых зеркал соедийены с входом 27 выходного токового зеркала и с коллектором 28 транзистора 26. Выходы 1О,13 и 15 входщ 1х токовых зеркал соеди шны с входом 29 траваистора 21. Первый коллектор ЗО транзистора 21 соединен с эмвсгтером тра&зистора 26 и источником 25 тока. Коллектор 31 травзистора 17 соединен с первой выходной шиной 32. Второй коллектор 33 травзистора 21 соединен с второй выходной шиной 34. Работа сумматора состоит в следу« шем. На входы iT, 8 и 9 затекают четырехуровневые свгиалы тока X, У и Z . Из входов 27 и 29 вытекает ток, величиш которого {ювна сумме входных токов. Еслв сумма входвых тгасов меньше 3,5, транзистор 21 открлт, травзкстор 26

Предлагаемый многоуровневый сумма4закрыт, выхаявое тсжрвое зеркало 16 передает на выход $ значение суммы входных тсжов Х,У а 2 . Если же сумма входных токов превы- шает значение 3,5, транзистор 21 закрывается, на выходе переноса Р поя&ляется сигнал переноса в виде единичного тока. Источник 24 тока создает .во входной тор позволяет увеличить значение ед ничного уровня тока в 2-2,3 раза и во столько же раз увеличить помехоустойивость и быстродействие сумматора и/или уменьшить вносимую сумматором огрешность на 20-60%. Формула изобретения Многоуровневый сумматор, состоящий Из несколькщс входных токовых зеркал с двумя выходами каждое, выходного то. кового Зеркала, порогового эл« 1ента с двумя заходами и источника тока, подключенного к первому выходу порогового элемента, первые выходы входных токовых зеркал соединены с входом выходного токового зеркала, выход которого подключен к первой выходной шине., вто|л 1е выходы входных токовых зеркал соеди- . йешл с входом порогового элемента, второй вьгход подключен к второй выходной шине, отличающий с я тем, что, с целью увеличения помехоустойчивости, йлстродействия и повышения точности, он дополнительно содержит транзистор p-fi-p типа с общей базой, эмиттер которэго соединен с пер1эым выходом порогового элемента, а коллекторс входом выходного токового зеркала. Источники информации, принятые во внимание при экспертизе 1.Вайиенко Л. В. и др. Элементарная ячейка параллельного мвогозначвого умножителя тщаГ.- -Микроэлектрс HBse, 198О,т. 9, вып. 5, рис. 5. 2.Патент США № 4140920, ЕЛ. И ОЭ К 19/08, 1979.

Авторы

Даты

1982-11-15—Публикация

1981-05-26—Подача