Изобретение относится к импульсной технике и предназначено для использования в многоуровневых арифметических устройствах с инжекционным питанием.

Целью изобретения является расширение функциональных возможностей путем одновременного сложения пяти операндов.

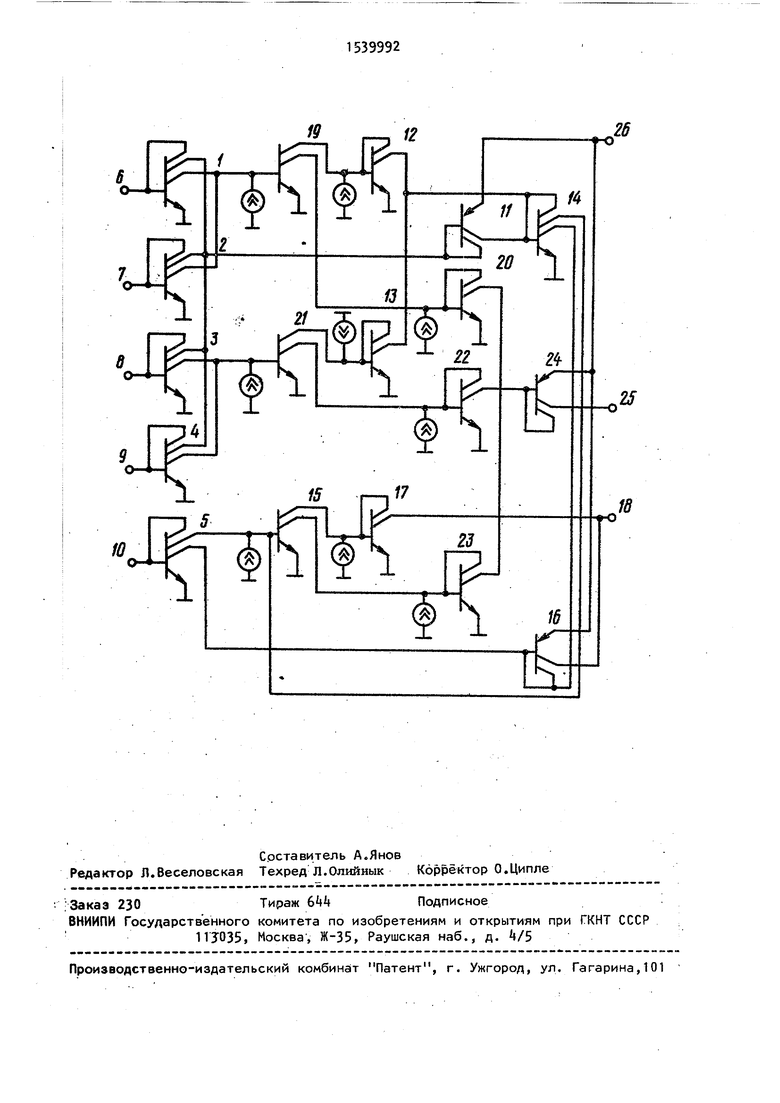

На чертеже приведена электрическая функциональная схема инжекционного сумматора.

Инжекционный сумматор содержит пять входных п-р-п-транзисторов 1 - 5 базы которых соединены с входными шинами 6-10 соответственно, а пер- , вые коллекторы входных п-р-п-транзисторов 1 - 4 - с базой первого р-п-р- транзистора 11, коллектор которого

соединен с коллекторами первого 12 и третьего 13 n-p-n-транзисторов и с базой четвертого п-р-п-транзистора 1, первый коллектор которого соединен с первым коллектором входного п-р-п-транзистора 5 и с базой десятого п-р-п-транзистора 15, а второй - с вторым коллектором входного п-р-п- транзистора 5 и с базой третьего р-п-р-транзистора 16, коллектор которого соединен с коллектором пятого п-р-п-транзистора 17 и с выходной шиной 18 младшего разряда, вторые коллекторы входных п-р-п-транзисторов 1 и 2 соединены с базой второго п-р-п- транзистора 19, первый коллектор которого соединен с базой первого п-р-п-транзистора 12, а второй - с

сл со & со

CD

to

базой седьмого n-p-n-транзистора 20, вторые коллекторы входных п-р-п-тран- зисторов 3 и 4 соединены с базой п-р-п-транзистора 21, первый коллектор которого соединен с базой девятого п-р-п-транзистора 13 а второй - с базой восьмого п-р-п-транзистора 22, первый коллектор десятого п-р-п- транзистора 15 соединен с базой пятого п-р-п-транзистора 17 а второй - с базой шестого п-р-п-транзистора 23, коллекторы п-р-п-транзисторов 20 22 и 23 соединены с базой второго р-п-р- транзистора 2k, коллектор которого соединен с выходной шиной старшего разряда Z5, эмиттеры р-п-р-транзисто- ров 11, 16 и 24 соединены с шиной 26 питания. В базы п-р-п-транзисторов 12,13,15,17,19 -23 задаются токи инжек торов равные четырем, четырем, трем с половиной, четырем, трем с половиной, одному, трем с половиной, одному и одному уровням тока соответственно.

Различные уровни тока, задаваемые инжектором, обеспечиваются соотношением площадей коллектора и эмиттера инжекционного р-п-р-транзистора. Транзистор, включенный по схеме токового отражения, представляет собой многоколлекторную транзисторную структуру, в которой соотношением площадей выходного коллектора и коллектора обратной связи обеспечивается коэффициент передачи транзисторной структуры, равный единице, т.е. входной ток равен выходному.

Инжекционный сумматор работает следующим образом.

Операнды A,B,C,D и Е в виде уровней тока подаются на входные шины 6 - 10. На соединенных первых коллекторах п-р-п-транзисторов 1 - 4 происходит суммирование величин токов операндов А,В,С и D, поступивших на зходные шины 6,7,8 и 9. Эта сумма через р-п-р-транзистор 11, включенный по схеме токового отражения, задается в базу п-р-п-транзистора 14. Если сумма операндов, поступивших на входные шины 6 и 7i равна S, А+ВЈгЗ а, где 10 - единичный уровень тока, то п-р-п-транзистор 19 открыт и шунтирует базы п-р-п-транзисторов 12 и 20. Аналогично, если сумма операндов, поступивших на входные шины 8 и 9, г. C+D43I0 то открыт п-р-п- транзистор 21 и шунтирует базы п-р-п- транзисторов 13 и 22. Если сумма

10

15

20

25

30

35

40

45

50

55

входных операндов, поступивших на входные шины 6 и 7, 21,410, п-р-п- транзистор 19 закрыт и от базы п-р-п- транзистора 14 п-р-п-транзистором 12 отводится ток, равный 4i0. При этом в базу п-р-п-транзистора 20 инжектором задается ток FJ i , а его коллектором такой же по величине ток отводится из базы р-п-р-транзистора 24. Если сумма входных операндов, поступивших на входные шины 8 и 9, ЈЈ C+T)2-4lo, то п-р-п-транзистор 21 закрыт и от базы п-р-п-транзистора 14 п-р-п-транзистором 13 отводится ток, равный 4i0. При этом в базу п-р-п- транзистора 23 инжектором задается ток Р2 10, а его коллектором такой же по величине ток отводится из базы р-п-р-транзистора 24. Таким образом, на базе п-р-п-транзистора 14 формируется значение младшего разряда суммы входных операндов A,B,C,D по модулю 4, поступивших на входные шины 6,7, 8 и 9,Ј3 §:,+., или Ј3(Ј,-4i0)+ + (SЈ-4i0), а на Ьазе р-п-р-транзистора 24 - старший разряд этой суммы Р+Р. Транзистором 14 ток, эквивалентный значению младшего разряда этой суммы, отводится из базы р-п-р- транзистора 16 и из базы п-р-п-транзистора 15. Из баз этих транзисторов также отводится п-р-п-транзистором 5 ток, равный значению входного операнда Е, подаваемого на входную шину 10. Если сумма этих величин Ј,, то она, просуммированная на соединенных вторых коллекторах п-р-п-транзисторов 5 и 14, через р-п-р-транзистор

16(токовый отражатель) без изменений подается в выходную шину 18 младшего разряда. При этом п-р-п-транзистор 15 открыт и шунтирует базы п-р-п-транзисторов 17 и 23. Если сумма этих величин -fE ki0, то п-р-п-транзистор 15 закрыт и из выходной шины 18 младшего разряда п-р-п-транзистором

17отводится ток, равный 4i , Ј.4

Ј+Ј-4i0. В базу п-р-п-транзистора 23 при этом инжектором задается ток, равный , и такой же ток отводится его коллектором из базы р-п-р- транзистора 24.

Таким образом, в выходной шине 25 формируется выходной ток старшего разряда +Рг +Р3 , а в выходной шине 18 - выходной ток младшего разряда Ј .(A+B+l D-t-E) mod 4.

Формула изобретения Инжекционный сумматор, содержащий три входных n-p-n-транзистора, первый n-p-n-транзистор и первый п-р-п-тран- зистор, включенные по схеме то- кового отражения, и второй п-р-п- Транзистор, включенный по схеме порогового детектора, причем первые коллекторы трех входных п-р-п-транзисто- ров соединены с базой первого р-п-р- транзистора, вторые коллекторы первого и второго входных п-р-п-транзисто- ров соединены с базой второго п-р-п- транзистора, первый коллектор которого соединен с базой первого п-р-п- транзистора, в базы первого и второго n-p-n-транзисторов задается ток инжектора, равный четырем и трем с половиной уровням- тока соответственно,эмиттер p-n-p-транзистора соединен с шиной питания, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены четвертый и пятый входные п-р-п-тран- зисторы, третий, четвертый, пятый7 шестой, седьмой, восьмой п-р-п-тран- зисторы, включенные по схеме токового отражения, девятый и десятый п-р-п- транзисторы, включенные по схеме порогового детектора, причем первый коллектор четвертого входного п-р-п- транзистора соединен с базой первого р-п- р-транзистора, вторые коллекторы третьего и четвертого входных п-р-п- транзисторов - с базой девятого п-р-п транзистора, первый коллектор которо го соединен с базой третьего п-р-п- транзистора, коллектор которого соединен с коллекторами первого п-р-п- и первого p-n-р- и базой четвертого n-p-n-транзисторов, первый коллектор которого соединен с первым коллектором пятого входного п-р-п-транзистора и базой десятого п-р-п-транзистора,

первый и второй коллекторы которого соединены с базами пятого и шестого n-p-n-транзисторов соответственно, вторые коллекторы второго и девятого n-p-n-транзисторов соединены соответственно с базами седьмого и восьмого n-p-n-транзисторов, коллекторы которых соединены с коллектором шестого n-p-n-транзистора и с базой второго p-n-p-транзистора, коллектор которого

0 соединен с выходной шиной старшего разряда, второй коллектор четвертого n-p-n-транзистора соединен с вторым коллектором пятого входного п-р-п- транзистора и с базой третьего р-п-р5 транзистора, коллектор которого соединен с коллектором пятого п-р-п- транзистора и с выходной шиной младшего разряда, при этом в базы третьего, пятого, шестого, седьмого,

о восьмого, девятого и десятого п-р-п- транзисторов задается ток инжектора,, равный четырем, четырем, одному, одному, одному, трем с половиной и трем с половиной уровням тока соответственно, эмиттеры второго и третьего p-n-p-транзисторов соединены с шиной питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Инжекционный сумматор-вычитатель | 1987 |

|

SU1471305A1 |

| Двухразрядный двоичный умножитель инжекционного типа | 1986 |

|

SU1335984A1 |

| Двухразрядный двоичный умножитель инжекционного типа | 1983 |

|

SU1150626A1 |

| Схема контроля на четность И @ Л-типа | 1988 |

|

SU1525906A1 |

| Полный троичный сумматор | 1979 |

|

SU826342A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1335982A1 |

| Управляющий регистр для буферного запоминающего устройства | 1987 |

|

SU1499405A1 |

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

| Цифроаналоговый преобразователь | 1986 |

|

SU1361719A1 |

| Четырехзначный умножитель элементов поля Галуа GF(2 @ ) | 1990 |

|

SU1737443A1 |

Изобретение относится к импульсной технике и может быть использовано в многоуровневых арифметических устройствах с инжекционным питанием. Цель изобретения - расширение функциональных возможностей инжекционного сумматора. Инжекционный сумматор содержит пять входных N-P-N-транзисторов, семь N-P-N- и три P-N-P-транзистора, включенных по схеме токового отражения, и три N-P-N-транзистора, включенные по схеме порогового детектора. Введение двух входных транзисторов, шести N-P-N- и двух P-N-P-транзисторов, включенных по схеме токового отражения, и двух N-P-N-транзисторов, включенных по схеме порогового детектора, позволяет обеспечить одновременное сложение пяти операндов. 1 ил.

| Полный одноразрядный сумматор инжекционного типа | 1980 |

|

SU892730A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Tich | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| IEEE | |||

| - Jornal of Solid-State Circuits, 1977, Sc | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| ( ИНЖЕКЦИОННЫЙ СУММАТОР | |||

Авторы

Даты

1990-01-30—Публикация

1988-06-24—Подача