(S) ЯЧЕЙКА АСИНХРОННОГО РАСПРЕДЕЛИТЕЛЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка асинхронного распределителя | 1980 |

|

SU924899A1 |

| Асинхронный распределитель | 1981 |

|

SU1018245A1 |

| Асинхронный распределитель | 1981 |

|

SU997261A1 |

| Асинхронный распределитель | 1982 |

|

SU1026304A1 |

| Кольцевой асинхронный распределитель | 1985 |

|

SU1322452A1 |

| Асинхронный распределитель | 1982 |

|

SU1064461A1 |

| Кольцевой асинхронный распределитель | 1989 |

|

SU1629978A2 |

| Ячейка асинхронного распределителя | 1976 |

|

SU718940A1 |

| Асинхронный распределитель | 1989 |

|

SU1622935A1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1992 |

|

RU2030094C1 |

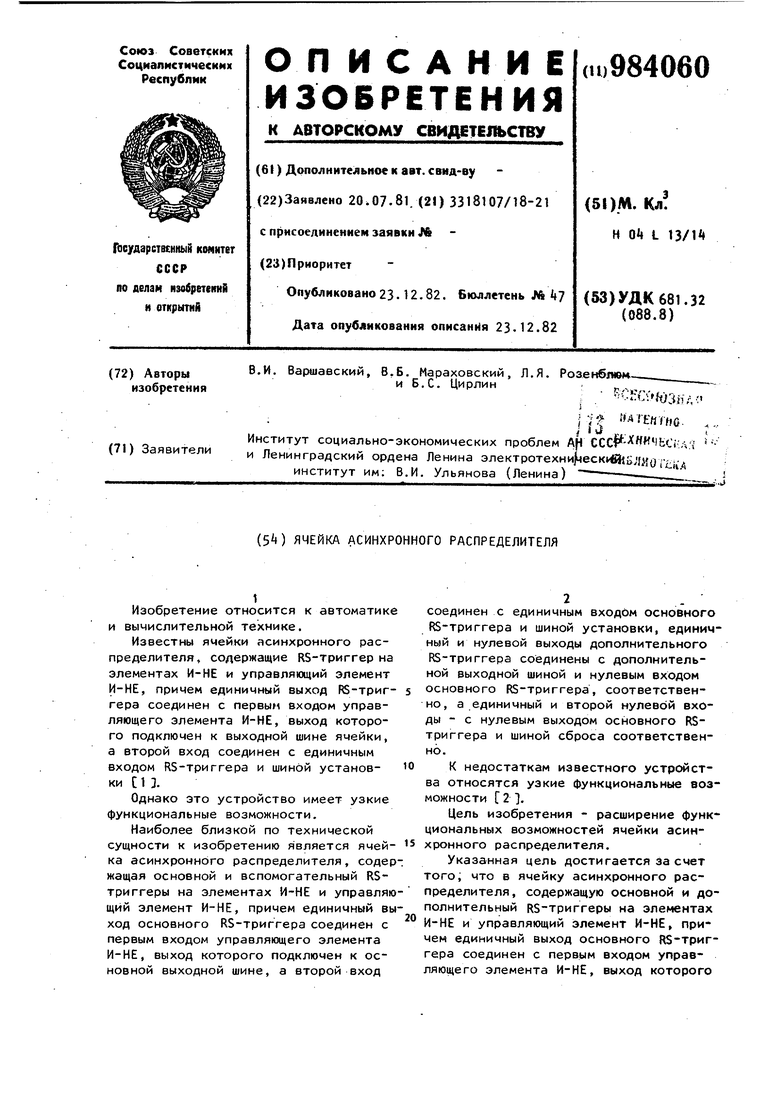

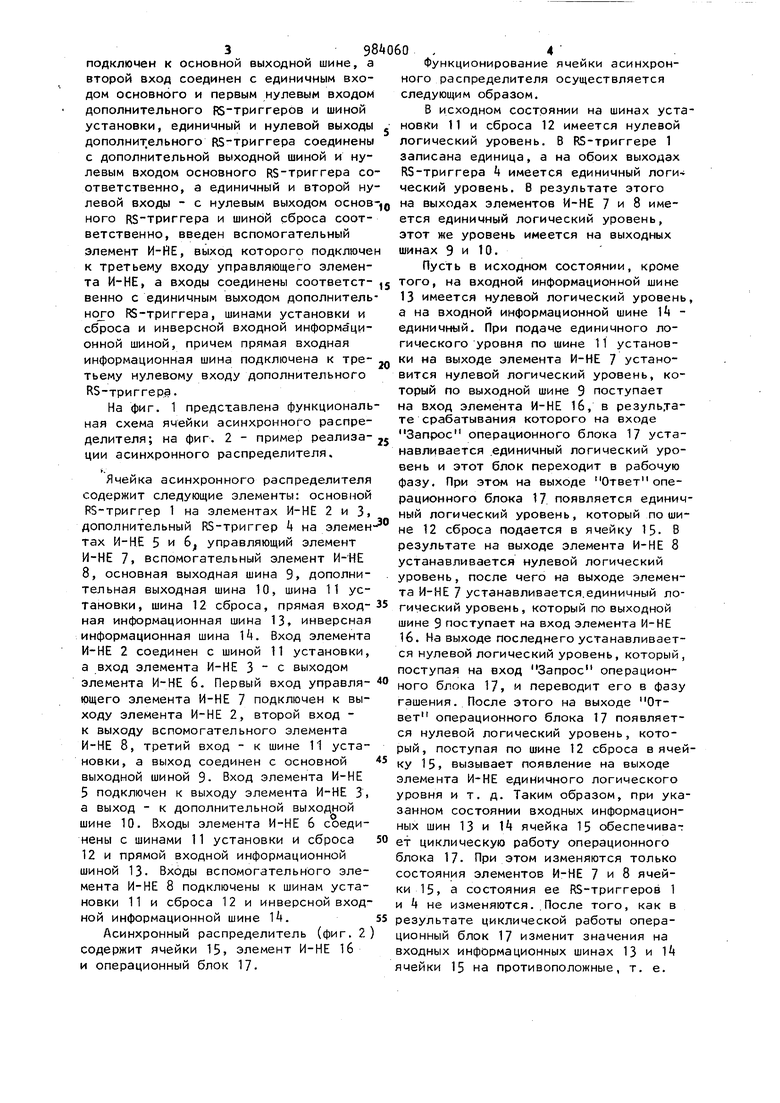

1 Изобретение относится к автоматике и вычислительной технике. Известны ячейки асинхронного распределителя, содержащие RS-триггер на элементах И-НЕ и управляющий элемент И-НЕ, причем единичный выход Р5-три1- гера соединен с первым входом управляющего элемента И-НЕ, выход которого подключен к выходной шине ячейки, а второй вход соединен с единичным входом RS-триггера и шиной установки С 1 . Однако это устройство имеет узкие функциональные возможности. Наиболее близкой по технической сущности к изобретению является ячейка асинхронного распределителя, содер жащая основной и вспомогательный RSтриггеры на элементах И-НЕ и управляю щий элемент И-НЕ, причем единичный вы ход основного RS-триггера соединен с первым входом управляющего элемента И-НЕ, выход которого подключен к основной выходной шине, а второй вход соединен с единичным входом основного RS-триггера и шиной установки, единич ный и нулевой выходы дополнительного RS-триггера соединены с дополнительной выходной шиной и нулевым входом основного RS-триггера, соответственно, а единичный и второй нулевой входы - с нулевым выходом основного RSтриггера и шиной сброса соответственно. К недостаткам известного устройства относятся узкие функциональные возможности 2 1. Цель изобретения - расширение функциональных возможностей ячейки асинхронного распределителя. Указанная цель достигается за счет того, что в ячейку асинхронного распределителя, содержащую основной и дополнительный RS-триггеры на элементах И-НЕ и управляющий элемент И-НЕ, причем единичный выход основного RS-триггера соединен с первым входом управляющего элемента И-НЕ, выход которого 3984 подключен к основной выходной шине, а второй вход соединен с единичным входом основного и первым нулевым входом дополнительного Р5-триггеров и шиной установки, единичный и нулевой выходы дополнит,ельного RS-триггера соединены с дополнительной выходной шиной и нулевым входом основного RS-триггера соответственно, а единичный и второй нулевой входы - с нулевым выходом основ ного RS-триггера и шиной сброса соответственно, введен вспомогательный элемент И-НЕ, выход которого подключе к третьему входу управляющего элемента И-НЕ, а входы соединены соответственно с единичным выходом дополнитель ного RS-триггера, шинами установки и сброса и инверсной входной информационной шиной, причем прямая входная информационная шина подключена к третьему нулевому входу дополнительного RS-триггера. На фиг. 1 представлена функциональ ная схема ячейки асинхронного распределителя; на фиг. 2 - пример реализации асинхронного распределителя. Ячейка асинхронного распределителя содержит следующие элементы: основной RS-триггер 1 на элементах И-НЕ 2 и 3, дополнительный RS-триггер 4 на элемен тах И-НЕ 5 и 6 управляющий элемент И-НЕ 7. вспомогательный элемент И-НЕ 8, основная выходная шина 9, дополнительная выходная шина 10, шина 11 установки, шина 12 сброса, прямая входная информационная шина 13, инверсная информационная шина 14. Вход элемента И-НЕ 2 соединен с шиной 11 установки, а вход элемента И-НЕ 3-е выходом элемента И-НЕ 6. Первый вход управляющего элемента И-НЕ 7 подключен к выходу элемента И-НЕ 2, второй вход к выходу вспомогательного элемента И-НЕ 8, третий вход - к шине 11 установки, а выход соединен с основной выходной шиной 9- Вход элемента И-НЕ 5 подключен к выходу элемента И-НЕ 3, а выход - к дополнительной выходной Входы элемента И-НЕ 6 соедишине 10. нены с шинами 11 установки и сброса 12 и прямой входной информационной шиной 13. Входы вспомогательного элемента И-НЕ 8 подключены к шинам установки 11 и сброса 12 и инверсной входной информационной шине 14. Асинхронный распределитель (фиг. 2) содержит ячейки 15, элемент И-НЕ 1б и операционный блок 17. 0 Функционирование ячейки асинхронного распределителя осуществляется следующим образом. В исходном сострянии на шинах установки 11 и сброса 12 имеется нулевой логический уровень. В RS-триггере 1 записана единица, а на обоих выходах RS-триггера k имеется единичный логический уровень, В результате этого на выходах элементов И-НЕ 7 и 8 имеется единичный логический уровень, этот же уровень имеется на выходных шинах 9 и 10. Пусть в исходном состоянии, кроме того, на входной информационной шине 13 имеется нулевой логический уровень, а на входной информационной шине k единичный. При подаче единичного логического уровня по шине 11 установки на выходе элемента И-НЕ 7 установится нулевой логический уровень, который по выходной шине 9 поступает на вход элемента И-НЕ 16, в результате срабатывания которого на входе Запрос операционного блока 17 устанавливается единичный логический уровень и этот блок переходит в рабочую фазу. При этом на выходе Ответ операционного блока 17 появляется единичный логический уровень, который по шине 12 сброса подается в ячейку 15- В результате на выходе элемента И-НЕ 8 устанавливается нулевой логический уровень, после чего на выходе элемента И-НЕ 7 устанавливается.единичный логический уровень, который по выходной шине 9 поступает на вход элемента И-НЕ 16. На выходе последнего устанавливается нулевой логический уровень, который, поступая на вход Запрос операцион блока 17, и переводит его в фазу гашения. После этого на выходе Ответ операционного блока 17 появляется нулевой логический уровень, который, поступая по шине 12 сброса в ячейку 15, вызывает появление на выходе элемента И-НЕ единичного логического уровня и т. д. Таким образом, при указанном состоянии входных информационных шин 13 и 14 ячейка 15 обеспечивав ет циклическую работу операционного блока 17. При этом изменяются только состояния элементов И-НЕ 7 и 8 ячейки 15, а состояния ее RS-триггеров 1 и 4 не изменяются..После того, как в результате циклической работы операционный блок 17 изменит значения на входных информационных шинах 13 и 14 ячейки 15 на противоположные, т. е. навходной информационной шине 13 установится единичный логический уровень, а на входной информационной шине 14 - нулевой (при этом изменении допустимо появление в транзитном соетоянии нулевого уровня на обеих входных информационных шинах 13 и It и недопустимо появление на них единичного логического уровня ), на выходе элемента 8 И-НЕ установится единичный логический уровень и этот элемент не будет больше влиять на работу ячейки 15. При этом поступление единичного логического уровня по шине 12 сброса переведет RS-триггер Ц в единичное состояние, после чего RS-триггер 1 установится в нулевое состояние. В результате на выходе элемента И-НЕ 7 установится единичный логический уровень, что, как уже было показано, neреводит операционный блок 17 в фазу гашения. При этом нулевой логический уровень поступает по шине 12 сброса в ячейку 15, что переводит RS-триггер в нулевое состояние и на выходной шине 10 установится нулевой логический уровень. Подачей нулевого логичес кого уровня по шине 11 установки ячей ка 15 переводится в исходное состояние. Таким образом, введение вспомогательного элемента И-НЕ позволило расширить функциональные возможности предлагаемой ячейки асинхронного распределителя по сравнению с известной ячейкой, так как при реализации графсхем алгоритмов, имеющих повторные операторы, входящие в цикл, отпадает необходимость дублирования соответствующих операционных блоков. Формула изобретения Ячейка асинхронного распределителя, содержащая основной и дополнительный RS-триггеры на элементах И-НЕ и управляющий элемент И-КЕ, причем единичный выход основного RS-триггера соединен с первым входом управляющего элемента И-НЕ, выход которого подключен к основной выходной шине, а второй вход соединен с единичным входом основного и первым нулевым входом дополнительного RS-триггеров и шиной установки, единичный и нулевой выходы дополнительного RS-триггера соединены с дополнительной выходной шиной и нулевым входом основного RS-триггера соответственно, а единичный и второй нулевой входы с нулевым выходом основного RS-триггера и шиной сброса соответственно, о тл и ч а ю щ а я с я тем, что, с целью расширения функциональных возможностей, введен вспомогательный элемент И-НЕ, выход которого подкгиочен к третьему входу управляющего элемента И-НЕ, а входа соединены соответственно с единичным выходом дополнительного RS-триггера, шинами установки и сброса и инверсной входной информационной шиной, причем прямая входная информационная шина подключена к третьему нулевому входу дополнительного Я -триггера. Источники информации, . принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 7189tO, кл. Н 01 L П/Й, 28.02.78, 2.Авторское свидетельство СССР по заявке Г 2997 7б, кл. Н 0 L 13/1, 21.10.80 (прототип).

Фиг. 2

Авторы

Даты

1982-12-23—Публикация

1981-07-20—Подача