(5) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ Изобретение относится к электрон ным измерителям времени и может быть использовано для управления вторич ными электронными часами, использующими временные посылки кодов. Известен устройство для формирова ния временных кодов, содержащее временной задатчик, преобразователь параллельного кода в последовательный, делитель частоты, ряд сметных ступеней, логические элементы И и ИЛИ и вторичные часы tl . Недостатком устройства является значительное время коррекции информации, записанной в счетных ступенях Наиболее близким по технической сущности к предлагаемому является .устройство для формирования временны кодов, содержащее временной задатчик преобразователь параллельного кода в последовательный, управляемый делитель частоты, ряд счетных ступеней логические схемы И и ИЛИ счетчика регистр сдвига, логические схемы И ВРЕМЕННЫХ КОДОВ регистра, блок управления, элемент задержки, логическую схему ИЛИ-НЕ и . вторичные часы, причем, первый выход временного задатчика соединен с синхронизирующим входом преобразователя параллегльного кода в последовательный и входом управляемого делителя частоты, выход каждого из логических элементов И счетчика соединен с первым входом логической схемы ИЛИ счетчика, второй вход которой соединен с выходом логической схемы И регистра, а выход каждой из логических схем ИЛИ счетчика соединен с входом своей счетной ступени, выходы которых соединены с входами преобразователя параллельного кода в последовательный, а его выход соединен со входом вторичных часов t2 . Недостатком этого устройства является отсутствие возможности одновременной автоматической и ручной коррекции .

Цель изобретения - расширение функциональных возможностей устройства.

Поставленная цель дас7игается тем, что в устройство для формирования временных кодов, содержащее временной задатчик, преобразователь паралледкного кода в по-следовательный управляе мый делитель частоты, ряд счетных ступеней, логические схемы И и ИЛИ счетчика, регистр сдвига, логические схемы И регистра, блок управления, элемент задержки, логическую схему ИЛИ-НЕ и вторичные часы, причем выход временного задатчика соединен с синхронизирующим входом преоб)азователя параллельного кода в последовательный и входом управляемого делителя частоты, выход каждого из логических элементов И счетчика соединен с первым входом логи« еской. схемы ИЛИ счетчика, второй вход которой соединен с выходом логической cxe(i И регистра, а выход каждой из логических схем ИЛИ счетчика соединен с входом своей счетной ступени, выходы которых соединены с входами преобразователя параллельного кода в последовательный, а его выход соединен с входом вторичных часов, введены программновременное устройство, управляемый генератор, счетчик-шифратор,- ряд счетных ступеней памяти, мультиплексор, первая и вторая логические схемы ИЛИ, при этом первый выход управляемого делителя частоты соединен через первый вход первой логической схемы ИЛИ со всеми первыми входами логических Схем И регистра, а второй выход управляемого делителя частоты соединен с первым входом первой логиJ ecкoй схемы И сметчика первой ступени, вторые входы логических схем И регистра соединены с соответствующими выходами регистра сдвига и входами логической схемы ИЛИ-НЕ, выход которой соединен с вторыми входами логических схем И счетчика, выход блока управления через первый вход второй логической схемы ИЛИ соединен с входом регистра сдвига и входом элемента задержки, выход которого соединен с третьими входами логических схем И регистра, первый выход программно-временного устройства соединен с входом управляемого генератора, выход которого соединен с входом счетчика-Е1 ифратора, первый выход которого соединен с управляющим входом

управляемого делителя частоты, второй - с вторым входом, второй логической схемы ИЛИ, а третий с входами мультиплексора, сигнальные входы которого соединены с первыми выходами счетных ступеней памяти, вторые выходы которых соединены с вторыми входами преобразователя параллельного кода в последовательный, а управляемые входы счетных ступеней памяти соединены с дополнительными выходами программно-временного устройства, выход мультиплексора соединен с вторым входом первой логической схемы ИЛИ, второй выход программно-временного устройства соединен с входом блока управления.

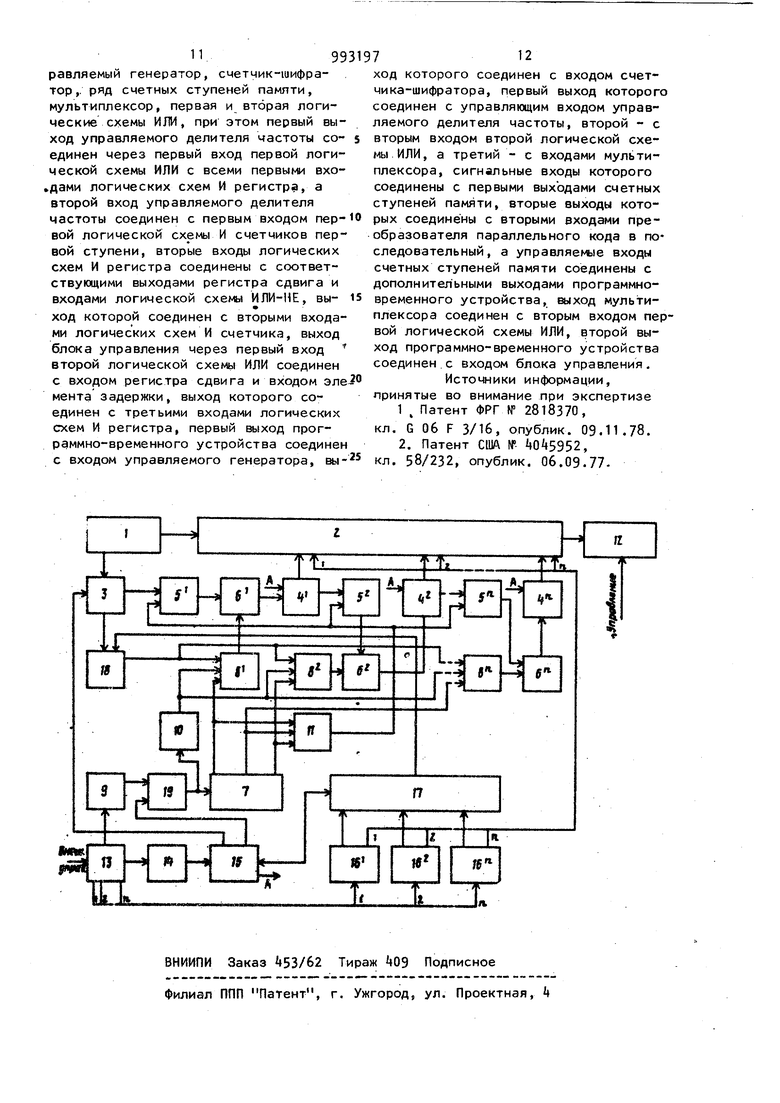

На чертеже приведена блок-схема устройства

Устройство для формирования временных кодов с комбинированной коррекцией содержит временной задатчик преобразователь 2 параллельного кода в последовательный, ряд счетных ступеней ,2,... ,4, управляемый делитель 3 частоты, логические схемы И и ИЛИ ,...,6

счетчика, регистр 7 сдвига, логические схемы И 8,8 %... ,8 регистра, блок 9 управления, элемент 10 задержки, логическую схему ИЛИ-НЕ 11, вториные чдсы 32J программно-временное устройство 13, управляемый генератор 1, счетчик-шифратор 15, ряд сметных ступеней памяти 16,162,..., 16 J мультиплексор 17, первую и вторую логические схемы ИЛИ 18 и 19, причем первый выход временного задатчика 1 соединен с синхронизирующим входом преобразователя параллельного кода в последовательный 2 и входом управляемого делителя 3 частоты, выход каждой из логических элементов И счетчика . . ,5 соединен с первым входом логической схемы ИЛИ б,б2,... ,6 счетчика, второй вход которой соединен с выходом логической схемы И 8,8,,.. ,8 регистра, а выход каждой из логических схем ИЛИ счетчика 6,6 ,..,,6 соединен с входом своей счетной ступени {( ,42,.,, , выходы которых соединены с входами преобразователя параллельного кода в последовательный 2 , а его выход соединен с входом вторичных часов 12, первый выход управляемого делителя 3 мастоты соединен через первый вход первой логичес5 .кой схемы ИШ 18 со всеми первь. вх дами логических схем И регистра 8 , б,... ,8, а второй выход управляе мого делителя 3 частоты соединен с первым входом первой логической схемы И счетчика 5 первой ступени, вторые входа логических схем И.регистра 8,8,.. .8 соединены с соответст вукхдими выходами регистра 7 сдвига и входами логической схемы ИЛИ-НЕМ , выход которой соединен с вторыми вхо дами логических схем И счетчика 5, 5,...5, выход блока 9 управления через первый вход второй логической схемы ИЛИ Т9 соединен с входом регис ра 7 сдвига и входом элемента 10 задержки, первый выход программно-временного устройства 13 соединен, с вхо дом управляемого генератора 1, выхо которого соединен с входом счетчикашифратора 15, первый выход которого соединен с управляющим входом управл емого делителя 3 частоты, второй - с вторым входом второй логической схеraj ИЛИ 19. а третий - с входами типлексора 17, сигнальные входа iKOToporo соединены с первыми выходами сметных ступеней памяти 16, ,... ,16, вторые выходы которых соединены с вторыми входами преобразователя параллельного кода впоследовательный 2, а управляемые входы сметных ступеней памяти IS, 16,.,. ,16 соединены с дополнительными олходами программно-временного устройства 13, выход мультиплексора 17 соединен с вторым входом первой логической схемы ИЛИ 18, второй выход программно-временного устройства 13 соединен с входом блока 9 управления Устройство работает следующим образом. В обычном состоянии, при включении устройства импульсы йапряжения, снимаемые с первого выхода временного задатчика 1, поступает на синхронизирующий вход преобразователя параллельного кода в последовательный 2. Так как счетные ступени А t,..., могут быть при включении принудительно обнулены, то в первый .момент с выхода преобразователя парал лельного кода в последовательный 2 снимается последовательный код нулей , поступающий на вход вторичн«х часов 12. С второго выхода временно.го задатчика 1 снимаются импульсы напряжения, частота повторения которых 976 кратна частоте импульсов, снимаемых с его первого выхода, чем и достигается синхрониза1 я работы преобразователя параллельного кода в последовательный 2 со всем устройством. С первого выхода управляемого делителя 3 частоты снимаются импульсы напряжения, частота повторения которых характеризует выбранную единицу отсчета, например секунду, а с второго выхода снимаются импульсы напряжения, частота вовторения которых характеризует масштаб времени коррекции информации, Так как в режиме отсчета текущего времени регистр 7 сдвига обнулен, то с выхода логической схемы ИЛИ-НЕ 11 снимается напряжение ( логическая единица), поступающее на вторые входы логических схем И . счетчиков, при этом на выходах логических схем И регистра 8,8,... ,8 напряжение отсутствует (логический ноль). Благодаря этому импульсы напряже ния, снимаемые с первого выхода управляемого делителя 3 частоты через логические схемы И 5 и ИЛИ б сметчика, поступают на вход первой счетной ступени 4. Выходные импульсы первой счетной ступени t через последовательно соединённые логические схемы И 5 и ИЛИ 6 поступают на вход второй счетной ступени счетчика и т.д. вплоть до последней счетной ступени 4. С информационных выходов всех счетных ступеней ,,... . код времени поступает на преобразователь параллельного кода в последовательный 2, позволяющий упростить канал передачи информации к вторичным часам 12. В режиме коррекции кода текущего времени возможно занесение информаЦии по двум каналам, первый из которых используется непосредственно one ратором (ручное управление с ожиданием сигнала точного времени), а вто-« рой используется при коррекции по сигналам точного времени извне. По первому каналу коррекция информации осуществляется следующиг образом. С выхода блока 9 управления по коанде оператора снимается напряжение, лительность которого пропорциональ-а числу, которое необходимо занести 9 8 старшую счетную ступень 4, передним фронтом этого напряжения через вторую логическую схему ИЛИ 19 осуществляется управление регистром 7 сдвига, который переключается на одну ступень. В результате этого переключения на выходе логической схемы ИЛИ-НЕ 11 образуется логический ноль (напряжение отсутствует/, который поступает на логические схемы И счет« 1ка S.S,... , последние за1фываются, благодаря ЭТОМУ информация о текущем времени ни в одну из счетных ступеней j,,... ,4 не поступает. По истечении некоторого времени, определяемого длительностью задержки элементом 10 задержки, на третьи входы логических схем И 8,8, .„.,8 регистра поступает напряжение, в результате чего импульсы напряжения, снимаемые с выхода первой логической схемы ИЛИ 18 через логические схемы И регистра 8 и ИЛИ 6 счетчика поступают на вход самой старшей счет ной ступени 4. На другие счетные ступени 6 ,.«., 6 импульсы напряжения поступать не будут, так как на вторых входах логи ческих схем И 8 ,„.., регистра от сутствует разрешающее напряжение, сн маемое с очередного выхода регистра 7 сдвига. Скорость занесения информации определяется в данном случае частотой импульсов, снимаег х с второго выхоДсг управляемого делителя 3 частоты. Так как длительность импульса напряжения, снимаемого с выхода блока 9 управления, пропорциональна заносимому числу импульсов, снимаемых с временного задатчика 1 и заносимых в счетную ступень 4, то в момент окончания импульса выходное напряже ние блока 10 задержки времени тоже становится равным нулю. Число, которое было занесено в пе вую счетную ступень счетчика, может быть проконтролировано на вторичных часах 12. При поступлении второго импульса напряжения на вход регистра 7 сдвига и элемента 10 задержки на втором выходе регистра 7 сдвига появляется напряжение, на первом же его.выходе оно становится равным нулю: 10 задержки в данном случае устраняет влияние фронтов напряжения при пере78 . ключении регистра сдвига на счетные ступени i и . Длительность импульса, снимаемого с выхода блока 9 управления, пропорциональна второму числу, заносимому в очередную счетную ступень . По истечении, некоторого времени, определяемому элементом 10 задержки, на третьи входы логических схем М 8 8 ,...,8 поступает напряжение, в результате чего импульсы напряжения, снимаемые с выхода управляемого делителя 3 частоты через первую логическую схему ИЛИ 18, поступают на первый вход логической схемы И регистра и с выхода последней импульсь напряжения через логическую схему ИЛИ поступают на вход счетной ступени i На другие счетные ступени импульсы напряжения поступать не будут, так как на всех вторых входах логических схем И регистра отсутствует разрешающее напряжение, снимаемое с очередного выхода регистра 7 сдвига. Для занесения информации в последующие счетные ступени с выхода блока 9 управления снимается очередной импульс напряжения и весь цикл занесения информации повторяется. После занесения числа в первую счетную ступень регистр 7 сдвига обнуляется и устройство формирует временной код в обычном режиме. При использовании второго канала коррекции, предварительно с помощью программно-временного устройства 13 в каждую из счетных ступеней памяти IS, 16,... ,16 заносится определенное число, которое необходимо занести в счетные ступени it,,..., 4. При поступлении внешнего командного импульса коррекции на вход программно-временного устройства 13 последнее блокирует блок 9 управления и запускает на время коррекции управляемый генератор . Импульсы напряжения высокой частоты, снимаемые с выхода управляемого генератора 1, поступают на вход счетчикашифратора 15, который первоначально , на все время коррекции закрывает (блокирует ) yпpaвляe fcIЙ делитель 3 частоты напряжением, снимаемым с его первого выхода, затем коротким импульсом напряжения, снимаемым с выхода А обнуляет все счетные ступени 4, ,... ,i по их обнуляющим входам А. Следующим импульсом напряжения, снимаемз1м с третьего выхода счетчика-шифратора, через вторую логическую схему ИЛИ регистр 7 сдвига сдвигается на одну ступень, поэтому на выходе логической схемы ИЛИ-НЕ 11 образуется уровень логического нуля, логические схемы И 5,5,...i5 закрываются и передача импульсов из любой счетной ступени 4, ,.,. , в другую не происходит. Затем с четвертого выхода счетчика-шифратора 15 снимается код напряжений, поступающий на управляющий вход мультиплексора 17. которыйп|эеобразует код числа, записанного в последней счетной ступени памяти 16, в количество импульсов, соответствующее этому коду. Импульсы напряжения, снимаемые с выхода мультиплексора 17, через первую логическую схему ИЛИ 18 посту па ITT на все первые входы логические схем И 8,8,...,8 регистра, а так как все разрешающие напряжения присутствуют только на логической схеме И 8 регистра, на третий вход которой разрешающее напряжение поступило с выхода элемента 10 задержки после сдвига регистра 7 сдвига, то импульсная последовательность , характеризующая заносимое число через логические схемы И 8 и ИЛИ 6 регистра, поступает в старшую счетную ступень Ц , По окончании занесения информацм1 в самую старшую ступень k с тр етьегс выхода счетчика-шифратора 15 снимается очередной импульс напряжения, который через вторую логическую схему ИЛИ 19 поступает на вход элемен та 10 задержки и вход регистра 7 сд га, :Последний переключается и с его второго выхода снимается разрвиающее напряжение, поступающее на второй вход логического элемента И 8 Veгистра, на его третьем входе разршгающее напряжение появится через некоторое время, определяемое элементом 10 выдержки, с четвертого выхода счетчика-шифратора 15 снимается код напряжений, поступающий на угравляющий вход мультиплексора 17, ас еговыхода преобразованный код напряжений поступает на вход первой логичес.кой схемы ИЛИ 18, с выхода которой через логические схемы И ИЛИ 6 регистра, поступает на вход последующей счетной ступени ..После замесения информации в счетную ступень с третьего выхода счетчика-шифратора снимается очередной импульс напряже997 10 ния, который управляет регистром 7 сдвига. Далее весь процесс занесения повторяется. По окончании коррекции в самой младшей ступени k регистр 7 сдвига обнуляется, управляемой делитель 3 частоты и блок 9 управления разблокируется, на выходе логической схемы ИЛИ-НЕ 11 образуется логическая единица и устройство работает в обычном режиме. Следует отметить, что частота управляемого генератора достаточно высока по сравнению с выходными импульсами управляемого делителя частоты, поэтому коррекция информации в счетных ступенях осуществляется весьма быстро и не влияет на точность показаний. Информация, записанная в ступенях памяти Тб,16,... ,16 может быть отображена на вторичных часах 12 по отдельной команде, что представляет собой удобство при работе с изделием. Формула изобретения Устройство для формирования временных кодов, содержащее временной задатчик, преобразователь параллельного кода -в последовательный, управляемый делитель частотьц ряд счетных ступеней, логические схемы И и ИЛИ счетчика, регистр сдвига, логические cxe(t И регистра, блок управления, элемент задержки, логическую схему ИЛИ-НЕ, вторичные часы, причем первый выход временного задатчика соединен с синхронизирующим входом преобрайователя параллельного кода в последовательный и входом управляемого делителя частоты, выход каждого из логических элементов И счетчика соединен с первым входом логической схемы ИЛИ счетчика, второй вход которой соединен с выходом логической схемы И регистра, а выход каждой из логических схем. ИЛИ счетчика соединен с входом своей счетной ступени, выходы которых соединены с входами преобразователя параллельного кода в последовательный, а его выход соединен с входом вторичных часов, о тличающееся тем, что, с целью расширения функциональных возможностей устройства, в него введены программно-временное устройство, управляемый генератор, счетчик-шифратор ,. ряд счетных ступеней памяти, мультиплексор, первая и вторая логические схемы ИЛИ, при этом первый выход управляемого делителя частоты соединен через первый вход первой логической схемы ИЛИ с всеми первыми логических схем И регистра, а второй вход управляемого делителя частоты соединен с первым входом первой логической схемы И счетчиков первой ступени, вторые входы логических схем И регистра соединены с соответствующими выходами регистра сдвига и входами логической схемы ИЛИ-НЕ, выход которой соединен с вторыми входами логических схем И счетчика, выход блока управления через первый вход второй логической схемы ИЛИ соединен с входом регистра сдвига и входом эле мента задержки, выход которого соединен с третьими входами логических схем И регистра, первый выход программно-временного устройства соединен с входом управляемого генератора, выход которого соединен с входом счетчика-шифратора, первый выход которого соединен с управляющим входом управляемого делителя частоты, второй - с вторым входом второй логической схемы ИЛИ, а третий - с входами мультиплексора, сигнальные входы которого соединены с первыми выходами счетных ступеней памяти, вторые выходы которых соединены с вторыми входами праобразователя параллельного кода в по следовательныи, а управляемые входы счетных ступеней памяти соединены с дополнительными выходами программновременного устройства, выход мультиплексора соединен с вторым входом первой логической схемы ИЛИ, второй выход программно-временного устройства соединен.с входом блока управления. Источники информации, принятые во внимание при экспертизе 1 , Патент ФРГ№ 2818370, кл. G Об F 3/16, опублик. 09.11.78. 2. Патент США № kQkS352, кл. 58/232, опублик. 06,09.77

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля времениРАбОТы МАшиН | 1979 |

|

SU813484A1 |

| Устройство для контроля времени работы машин | 1981 |

|

SU949672A2 |

| Устройство для обработки и передачи информации учета товарной нефти | 1987 |

|

SU1413645A1 |

| Устройство для контроля времени работы машин | 1980 |

|

SU934516A1 |

| Устройство для динамической коррекции информации в электронных часах | 1987 |

|

SU1437828A1 |

| Устройство для контроля времени работы оборудования | 1990 |

|

SU1815664A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| Устройство для регистрации аналогового процесса | 1989 |

|

SU1774379A1 |

| Устройство для ввода информации | 1982 |

|

SU1062683A1 |

Авторы

Даты

1983-01-30—Публикация

1980-03-28—Подача