Изобретение относится к вычислительной технике и может быть применено в системах, в которых один блок памяти одновременно используется несколькими процессорами.

Известны устройства, которые, принимая от процессоров сигналы запроса шины, выдают сигнал разрешения захвата шины процессору, имеющему высший приоритет. Если процессором, выставившим запрос, не получено разрешение или получено разрешение, но шина не свободна, то этот процессор должен находиться в состоянии ожидания. Это реализуется либо за счет использования специального входа готовности внешнего устройства, либо за счет задержки тактовых импульсов процессора. Однако существуют процессоры не имеют входа готовности внешнего устройства и используют встроенный генератор тактовых импульсов, что не позволяет применять эти способы для включения такого процессора в мультипроцессорную систему. Использование прерывания для повторения обращения к шине в случае ее занятости или чисто программного анализа сигналов, характеризующих состояние шины, приводит к значительным потерям времени при обращении к шине, что является общим недостатком всех перечисленных устройств.

Наиболее близким по технической сущности к заявляемому является устройство для сопряжения процессоров с общим блоком памяти, выбранное в качестве прототипа, которое содержит два триггера и два элемента И, причем синхровход первого триггера подключен к входу запроса первого процессора, единичный выход первого триггера соединен с информационным входом второго триггера и подключен к входу блокировки первого процессора, первый вход элемента И соединен с первым входом второго элемента И и подключен к синхровыходу второго процессора, второй вход первого элемента И подключен к выходу блокировки второго процессора, выход второго элемента И подключен к синхровходу первого процессора и общего блока памяти, при этом информационный вход первого триггера подключен к шине единичного потенциала устройства, выход первого элемента И соединен с синхровходом второго триггера. Это устройство позволяет второму процессору с минимальной задержкой обращаться к шине, при этом первый процессор получает доступ к шине, если второй процессор к ней не обращается.

Однако данное устройство не обеспечивает работу процессоров и общего блока памяти через шину И 41, так как требует расположения обоих процессоров и мультиплексора на одной плате. Кроме того, невозможно увеличение числа процессоров в системе.

Целью изобретения является расширение области применения.

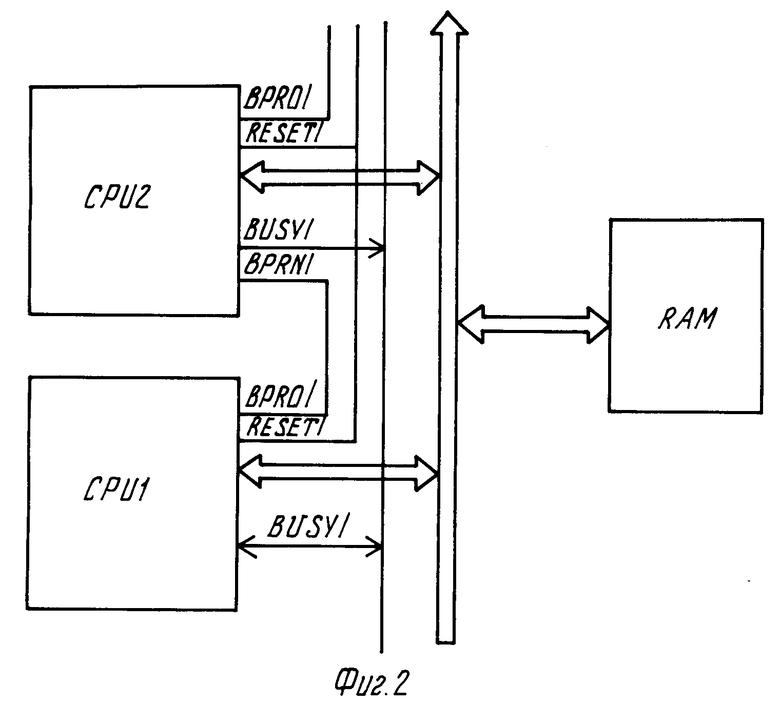

Указанная цель достигается тем, что в процессор, имеющий высший приоритет, вводится схема формирования сигналов запрета обращений других процессоров к шине. Предложенное устройство для сопряжения процессоров с общим блоком памяти содержит буферы 6 шин данных, адреса, управления, два RS-триггера 2, 4, элемент НЕ 1, резистор 7, конденсатор 8, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9, два элемента И-НЕ 12, элемент ИЛИ 10, элемент ИЛИ-НЕ 11, элемент НЕ 5 с открытым коллектором, элемент И 13, причем первые входы элементов И-НЕ 3, 12 и первый вход элемента ИЛИ соединены с входом запроса интерфейса, второй вход первого элемента И-НЕ соединен с выходом элемента НЕ с открытым коллектором, вторым входом элемента ИЛИ-НЕ и входом занятости интерфейса, выход первого элемента И-НЕ соединен с входом сброса первого RS-триггера, вход установки первого RS-триггера соединен с прямым выходом второго RS-триггера и выходом запрета, прямой выход первого RS-триггера соединен с вторым входом элемента ИЛИ и входами разрешения работы буферов шин данных, адреса, управления, инверсный выход первого RS-триггера соединен с первым входом элемента ИЛИ-НЕ и входом элемента НЕ с открытым коллектором, выход элемента ИЛИ-НЕ соединен с вторым входом второго элемента И-НЕ, выход второго элемента И-НЕ соединен с входом запроса прерывания, вход элемента НЕ соединен с входом установки запрета и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход элемента НЕ соединен с первым выходом резистора, второй выход резистора соединен с первым выходом конденсатора и вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй выход конденсатора соединен с общим проводом, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом установки второго RS-триггера, вход сброса второго RS-триггера соединен с выходом элемента И, первый вход элемента И соединен с входом начального сброса, второй вход элемента И соединен с выходом элемента ИЛИ.

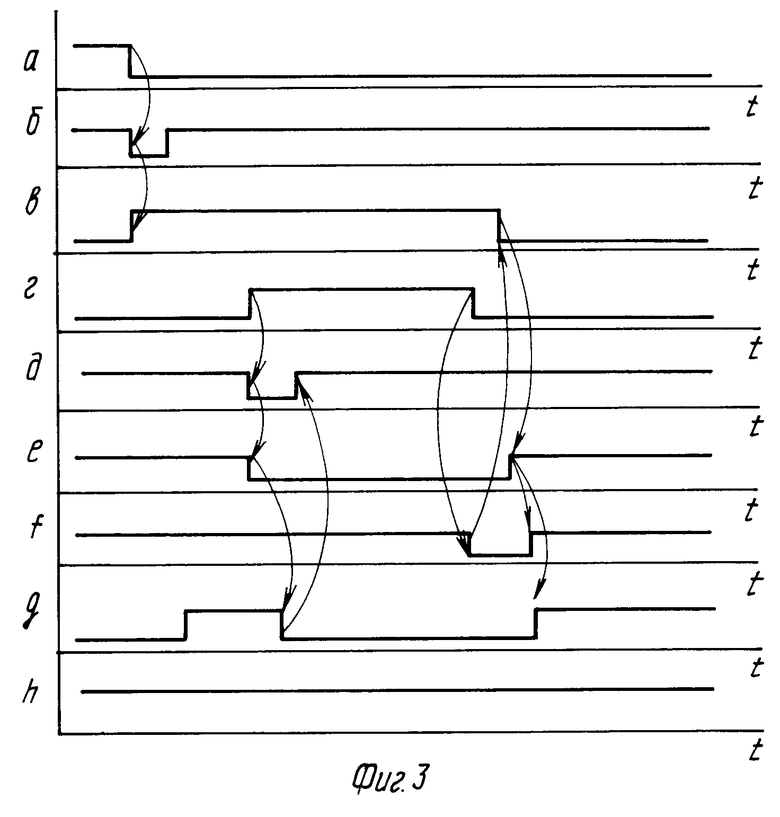

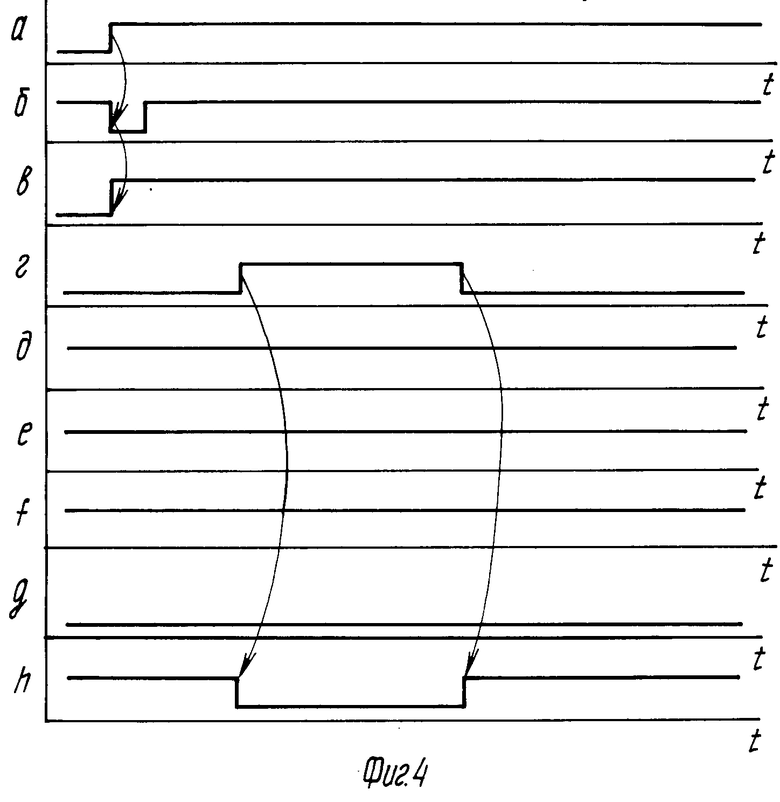

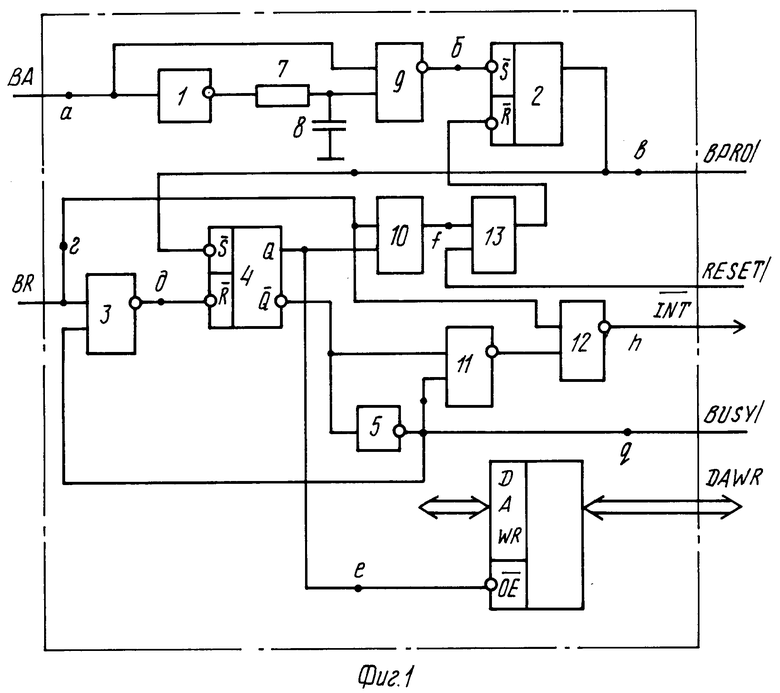

На фиг. 1 изображена принципиальная схема устройства, где ВА-сигнал установки запрета выходов других процессоров на интерфейс. BR-запрос интерфейса, BPRO-сигнал запрета обращений других процессоров на интерфейс ("лог. 1" - запрет), BUSY-сигнал занятости интерфейса ("лог. 0" - интерфейс занят), DAWR-шины данных, адреса и управления интерфейса, PESET - сигнал начального сброса; на фиг. 2 - схема подключения процессора CPU 1 с описываемым устройством к интерфейсу И-41; на фиг. 3 - временные диаграммы работы устройства при своевременном освобождении интерфейса; на фиг. 4 - временные диаграммы работы устройства при длительной занятости интерфейса.

Устройство работает следующим образом. Оно устанавливается в процессор, имеющий высший приоритет на интерфейсе. При начальном сбросе системы, когда сигнал начального сброса PESET принимает состояние "лог. 0", на входе сброса триггера 2 возникает состояние "лог. 0" и он сбрасывается. На входе установки триггера 4 возникает состояние "лог. 0", а на входе сброса триггера 4 присутствует "лог. 1", так как сигнал запроса интерфейса BR имеет состояние "лог. 0". Таким образом на прямом выходе триггера 4 устанавливается "лог. 1". После снятия установки сигнала PESET в "лог. 1" на входе сброса триггера 2 появляется "лог. 1" и устройство готово к работе. Перед обращением на интерфейс процессор инвертирует сигнал ВА. Взводится триггер 2 и выставляется BPRO-сигнал запрета обращений на интерфейс другим процессорам. Через один цикл, необходимый для завершения операций на интерфейсе процессором, занимающим его, выставляется запрос BR. Сбрасывается триггер 4, открывается буфер 6, связывающий локальные шины процессора с интерфейсными шинами данных, адреса и управления. Если перед этим сигнал BUSY был в состоянии "лог. 1" (шина свободна), то сигнал прерывания INT не возникает. При выходе на интерфейс сигнал BUSY сбрасывается в 0 через инвертор с открытым выходом 5. После завершения операции на интерфейсе снимается запрос BR, на выходе элемента ИЛИ 10 появляется "лог. 0", сбрасывается триггер 2, снимается запрет BРRO, устанавливается триггер 4, закрывается буфер 6, снимается сигнал BUSY. Если к моменту сброса триггера 4 при выходе на интерфейс, сигнал BUSY будет установлен в 0 другим процессором, не освободившим к этому моменту интерфейс, триггер 4 не будет сброшен через элемент И-НЕ 3 и возникнет сигнал прерывания INT. Выход на интерфейс в этом цикле не осуществляется и происходит переход на подпрограмму обработки прерывания. За счет заблаговременного предупреждения других процессоров через сигнал BPRO о занятии процессором CPUI интерфейса такая ситуация практически исключается. Она возникает только, если другой процессор по каким-либо причинам займет интерфейс более чем на один цикл. Таким образом процессор CPUI осуществляет выход на интерфейс без циклов ожидания, не задерживая своей работы. (56) Авторское свидетельство СССР N 1319039, кл. G 06 F 13/00, 1987.

Авторское свидетельство СССР N 1241246, кл. G 06 F 13/00, 1986.

Изобретение относится к вычислительной технике и может быть использовано в системах, в которых один блок памяти одновременно используется несколькими процессорами. Целью изобретения является расширение области применения. Для этого в устройство введены второй триггер, второй элемент НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, резистор, конденсатор, элемент И. Устройство содержит также блок буферов шин интерфейса, триггер, два элемента И - НЕ, элемент ИЛИ, элемент ИЛИ - НЕ, элемент НЕ. 4 ил.

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРОВ С ОБЩИМ БЛОКОМ ПАМЯТИ, содержащее блок буферов шин интерфейса, первый триггер, два элемента И - НЕ, элемент ИЛИ, элемент ИЛИ - НЕ, первый элемент НЕ, причем первые входы первого и второго элементов И - НЕ и первый вход элемента ИЛИ соединены с входом запроса интерфейса устройства, второй вход первого элемента И - НЕ соединен с выходом первого элемента НЕ, первые входом элемента ИЛИ - НЕ и входом занятости интерфейса устройства, выход первого элемента И - НЕ соединен с входом сброса первого триггера, прямой выход которого соединен с вторым входом элемента ИЛИ и входом разрешения работы блока буферов шин интерфейса, инверсный выход первого триггера соединен с вторым входом элемента ИЛИ - НЕ и входом первого элемента НЕ, выход элемента ИЛИ - НЕ соединен с вторым входом второго элемента И - НЕ, выход которого соединен с выходом запроса прерывания устройства, отличающееся тем, что в устройство введены второй триггер, второй элемент НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, резистор, конденсатор, элемент И, причем вход второго элемента НЕ соединен с входом запрета выхода других процессоров на интерфейс устройства и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго элемента НЕ соединен с первым выводом резистора, второй вывод резистора соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым выводом конденсатора, второй вывод конденсатора соединен с шиной нулевого потенциала устройства, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом установки второго триггера, вход сброса второго триггера соединен с выходом элемента И, прямой выход второго триггера соединен с входом установки первого триггера и с выходом запрета обращений других процессоров на интерфейс устройства, первый вход элемента И соединен с выходом элемента ИЛИ, второй вход элемента И соединен с входом начального сброса устройства.

Авторы

Даты

1994-01-30—Публикация

1991-07-05—Подача