Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении специализированных, в том числе и систолических устройств, предназначенных для выполнения операций над матрицами.

Известно устройство для перемножения матриц [1] , содержащее умножитель, сумматор и три регистра. Недостатком этого устройства является то, что оно выполняет перемножение двух матриц.

Наиболее близким к предлагаемому по технической сущности является устройство для перемножения матриц [2] , содержащее n*n вычислительных модулей (ВМ). Недостатком прототипа являются большие аппаратурные затраты.

Целью изобретения является сокращение аппаратурных затрат.

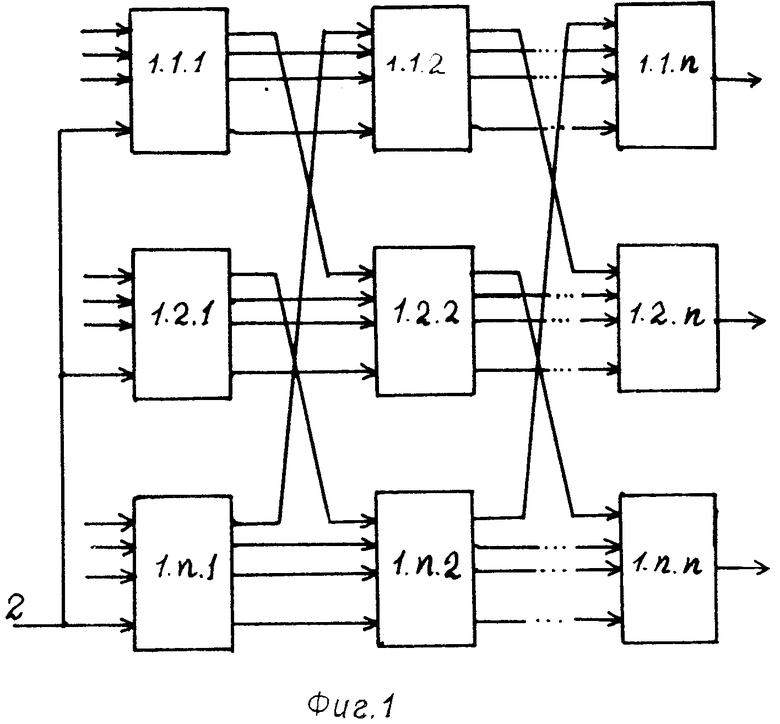

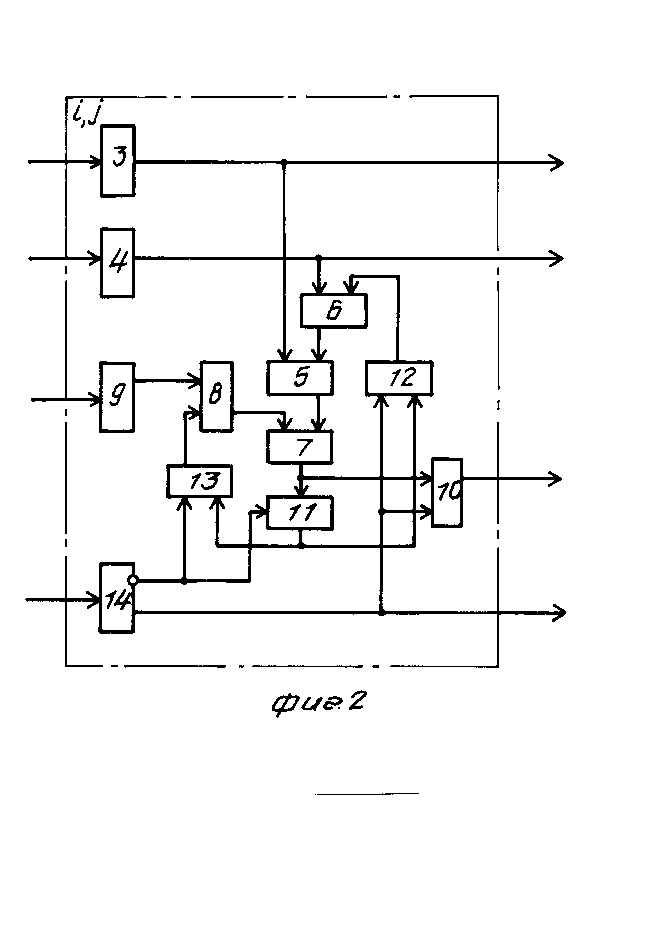

На фиг. 1 представлена структурная схема устройства для перемножения матриц; на фиг. 2 - структурная схема i-го ВМ.

Устройство для перемножения матриц (фиг. 1) содержит n*n ВМ 1.1.1-1. n. n (n - разрядность обрабатываемых матриц), причем первый, второй и третий информационные входы (i, 1)-го ВМ соединены соответственно с i-м информационным входом первой, второй и третьей групп устройства (i = 1, . . . , n), тактовый вход 2 которого соединен с входом записи (i, 1)-го ВМ, второй и третий выходы каждого (i, j-го ВМ соединены соответственно с вторым и третьим информационными входами (i, j+1)-го ВМ модуля (i = 1, . . . , n+1), третий выход (i, n)-го ВМ соединен с i-м выходом устройства, первый выход (i, j)-го ВМ, кроме (n, j)-х ВМ, соединен с первым информационным входом (i+1, j+1)-го ВМ, первый выход (n, j)-го ВМ соединен с первым информационным входом (1, j+1)-го ВМ, четвертый выход (i, j)-го ВМ - с входом записи (i, j+1)-го ВМ.

ВМ 1, i, j (фиг. 2) содержит четыре регистра, умножитель, сумматор, триггер, три элемента И и два элемента ИЛИ. Вход первого регистра 3 подключен к первому информационному входу ВМ, второй информационный вход которого подключен к входу второго регистра 4. Выход первого регистра 3 подключен к первому входу умножителя 5 и первому информационному выходу i-го ВМ, второй выход которого подключен к выходу второго регистра 4 и первому входу первого элемента ИЛИ 6. Выход последнего подключен к второму входу умножителя 5, выход которого подключен к первому входу сумматора 7. Второй вход сумматора подключен к выходу второго элемента ИЛИ 8, первый вход которого подключен к выходу третьего регистра 9. Вход регистра 9 подключен к третьему информационному входу ВМ, третий выход которого подключен к выходу первого элемента И 10. Информационный вход элемента И 10 подключен к выходу сумматора 7 и входу четвертого регистра 11, выход которого подключен к информационным входам второго 12 и третьего 13 элементов И. Выход второго элемента И 12 подключен к второму входу первого элемента ИЛИ 6, выход третьего элемента И 13 подключен к второму входу второго элемента ИЛИ 8. Вход разрешения записи подключен к входу триггера 14, инверсный выход которого подключен к управляющему входу третьего элемента И 13 и входу разрешения записи регистра 11, а прямой выход подключен к управляющим входам первого 10 и второго 12 элементов И и к выходу разрешения записи i-го ВМ.

Устройство предназначено для перемножения матриц А*B*C= F (А, В и С - матрицы размерности n*n) и может быть реализовано на следующих формулах

dij=  aik·bkj ;

aik·bkj ;

fis dij·cjs , где aik, bkj и сjs - элементы матриц А, В и С; dij - элементы промежуточной матрицы; fis - элементы конечной матрицы F.

dij·cjs , где aik, bkj и сjs - элементы матриц А, В и С; dij - элементы промежуточной матрицы; fis - элементы конечной матрицы F.

Рассмотрим работу устройства. Положим n = 3. Условимся, что прием информации во все регистры осуществляется по переднему фронту синхроимпульса, т. е. в начале такта. Считаем, что перед началом вычислений все регистры установлены в нулевое состояние. Импульс пуска поступает на тактовый вход 2 устройства. На первые входы первым ВМ 1.1.1-1. n. 1 поступают элементы bkj матрицы В по столбцам, а элементы сjsматрицы С по строкам, на вторые входы - элементы аik матрицы А по строкам, на третьи входы подается логический "0", т. е. С, В - первые входы, 0, А - вторые входы, 0, 0 - третьи входы:

Результирующая матрица получена следующим образом:

f11 = d11C11 + d13C31 + d12C21;

f21 = d22C21 + d21C11 + d23C31;

f31 = d33C31 + d32C21 + d31C11;

f12 = d11C12 + d13C32 + d12C22;

f22 = d22C22 + d21C12 + d23C32;

f32 = d32C32 + d32C22 + d31C12;

f13 = d11C13 + d13C33 + d12C23;

f23 = d22C23 + d21C13 + d23C33;

f33 = d33C33 + d32C23 + d31C13.

Нулевой такт В ВМ 1.1.1 на первый и второй входы поступают соответственно элементы b11 и a11, они записываются в регистры 3.1.1 и 4.1.1. В ВМ 1.2.1 в регистр 3.2.1 записывается b13, а в регистр 4,2,1-a21. В ВМ 1.3.1 в регистр 3.3.1 записывается b13, а в регистр 4.3.1-a31.

Первый такт. В ВМ 1.1.1 на входы умножителя 5.1.1 поступают элементы a11 и b11 умножаются и произведение (a11b11) поступает в сумматор 7.1.1, суммируется с нулем и результат записывается в регистр 11.1.1. В резистор 3.1.1 записывается b21, а в регистр 4.1.1-a12. В регистр 3.1.2 записывается b13, а в регистр 4.1.2-a11. В ВМ 1.2.1 с выхода умножителя 5.2.1 выдается произведение, в сумматоре 7.2.1 суммируется с нулем и результат записывается в регистр 11.2.1. В регистр 3.2.1 записывается элемент b22, а в регистр 4.2.1-a22. В регистр 3.2 2 записывается элемент a21, а в регистр 4.2.2-b21. В ВМ 1.3.1 c выхода умножителя 5.3.1 выдается произведение а31b13, которое, пройдя сумматор 7.3.1, записывается в регистр 11.3.1. В регистр 3.3.1 записывается элемент b23, а регистр 4.3.1-a32. В регистр 3.3.2 записывается элемент b21 а в регистр 4.3.2-a31.

Второй такт. В ВМ 1.1.1 с выхода умножителя 5.1.1 выдается произведение а12b21, которое поступает в сумматор 7.1.1. Сюда же с выхода регистра 11.1.1 через элемент И 13.1.1 и второй вход элемента ИЛИ 8.1.1 на второй вход поступает произведение а11b11 и с выхода сумматора 7.1.1 выдается сумма произведений а11b11+а12b21, которая записывается в регистр 11.1.1. В регистр 3.1.1 записывается элемент b31, а в регистр 4.1.1 - элемент a13. В ВМ 1.1.2 с выхода умножителя 5.1.2 выдается произведение а11b13, которое пройдя сумматор 7.1.2, записывается в регистр 11.1.2. В регистр 3.1.2 записывается элемент b23, а в регистр 4.1.2-a12. В регистр 3.1.3 записывается элемент b12, а в регистр 4.1.3 - элемент a11. В ВМ 1.2.1 с выхода умножителя 5.2.1 выдается произведение а22b22, которое поступает в сумматор 7.2.1, где суммируется с поступающим туда через элементы И 13 и ИЛИ 8 произведением а21b12. С выхода сумматора 7.2.1 выдается сумма а21b12 + а22b22, которая записывается в регистр 11.2.1. В регистр 3.2.1 записывается элемент b32, а в регистр 4.2.1 - элемент a23. В ВМ 1.2.2 с выхода умножителя 5.2.2 выдается произведение, которое, пройдя через сумматор 7.2.2, записывается в регистр 11.2.2. В регистры 3.2.2 и 4.2.2 соответственно записываются элементы b21 и a22. В регистры 3.2.3 и 4.2.3 соответственно записываются элементы а21 и b13. В ВМ 1.3.1 с выхода умножителя 5.3.1 выдается произведение а32b32, которое подается в сумматор 7.3.1. С его выхода выдается сумма а31b13 + а32b23, которая записывается в регистр 11.3.1. В регистры 3.3.1 и 4.3.1 соответственно записываются элементы b33 и а33. В ВМ 1.3.2 с выхода умножителя 5.3.2 выдается произведение а31b12, которое, пройдя сумматор 7.3.2, записывается в регистр 11.3.2. В регистры 3.3.2 и 4.3.2 соответственно записываются элементы b22 и a32. В регистры 3.3.3 и 4.3.3 соответственно записываются элементы b11 и a31.

Третий такт. В ВМ 1.1.1 с выхода умножителя 5.1.1 выдается произведение а13b31 которое поступает в сумматор 7.1.1. С его выхода выдается сумма а11b11+а12b21+а13b31= = d11, которая записывается в регистр 11.1.1. На первый вход ВМ поступает элемент c11, который записывается в регистр 3.1.1. В ВМ 1.1.2 с выхода умножителя 7.1.2 выдается произведение а12b23, которое поступает в сумматор 7.1.2. С его выхода выдается сумма а11b13+а12b23, которая записывается в регистр 11.1.2. В регистры 3.1.2 и 4.1.2 соответственно записываются элементы b33 и а13. В ВМ 1.1.3 с выхода умножителя 5.1.3 выдается произведение а11b12, которое, пройдя сумматор 7.1.3, записывается в регистр 11.1.3. В регистры 3.1.3 и 4.1.3 соответственно записываются элементы b22 и a12. В ВМ 1.2.1 с выхода умножителя 5.2.1 выдается произведение а23b32, она поступает в сумматор 7.2.1, с выхода которого выдается сумма а21b21+а22b22+а23b32 = d32, она записывается в регистр 11.2.1. В ВМ 1.2.2 с выхода умножителя 5.2.2 выдается произведение а22b21, оно поступает в сумматор 7.2.2, с выхода которого выдается сумма а22b21+а22b21, она записывается в регистр 11.2.2. В регистры 3.2.2 и 4.2.2 соответственно записываются элементы b31 и а23. В ВМ 1.2.3 с выхода умножителя 5.2.3 выдается произведение а21b13, которое пройдя сумматор 7.2.3, записывается в регистр 11.2.3. В регистры 3.2.3 и 4.2.3 соответственно записываются элементы b23 и a22. В ВМ 1.3.1 с выхода умножителя 5.3.1 выдается произведение а33b33, оно поступает в сумматор 7.3.1, с выхода которого выдается сумма а31b13+а32b23+а33b33= d33, она записывается в регистр 11.3.1. В регистр 3.3.1 записывается элемент с31. В ВМ 1.3.2 с выхода умножителя 5.3.2 выдается произведение а32b22, оно поступает в сумматор 7.3.2, с выхода которого выдается сумма а21b12+а32b22, она записывается в регистр 11.3.2. В регистры 3.3.2 и 4.3.2 соответственно записываются элементы b32 и a33. В ВМ 1.3.3 с выхода умножителя 5.3.3 выдается произведение а31b11, которое, пройдя сумматор 7.3.3, записывается в регистр 11.3.3. В регистры 3.3.3 и 4.3.3 соответственно записываются элементы b21 и a32.

Четвертый такт. В ВМ 1.1.1 с выхода умножителя 5.1.1 выдается произведение d11c11, которое поступает в сумматор 7.1.1, суммируется с нулем и, пройдя элемент И 10.1.1, записывается в регистр 9.1.2. В регистр 3.1.1 записывается c12. В ВМ 1.1.2 с выхода умножителя 5.1.2 выдается произведение а13b33, оно поступает в сумматор 7.1.2, с выхода которого выдается сумма а11b13+а12b23+а13b33= d13, она записывается в регистр 11.1.2, а в регистр 3.1.2 записывается с31. В ВМ 1.1.3 с выхода умножителя 5.1.3 выдается произведение а12иb22, оно поступает в сумматор 7.1.3, с выхода которого выдается сумма а11b12+а12b22, она записывается в регистр 11.1.3. В регистры 3.1.3 и 4.1.3 соответственно записываются элементы b32 и a13. В ВМ 1.2.1 с выхода умножителя 5.2.2 выдается произведение d22c21, которое пройдя сумматор 7.2.1, записывается в регистр 9.2.2. В регистр 3.2.1 записывается элемент с22. В ВМ 1.2.2 с выхода умножителя 5.2.2 выдается произведение а23b31, оно поступает в сумматор 7.2.2, с выхода которого выдается сумма а21b21+a22b21+a23b31= d21, она записывается в регистр 11.2.2. В регистр 3.2.2 записывается элемент с11. В ВМ 1.2.3 с выхода умножителя 5.2.3 выдается произведение а22b23, оно поступает в сумматор 7.2.3, с выхода которого выдается сумма а21b13+a22b23, она записывается в регистр 11.2.3. В регистры 3.2.3 и 4.2.3 записываются элементы b33 и a23. В ВМ 1.3.1 с выхода умножителя 5.3.1 выдается произведение d22c31, которое записывается в регистр 9.3.2. В регистр 3.3.1 записывается элемент с32. В ВМ 1.3.2 с выхода умножителя 5.3.2 выдается произведение а33b32, оно поступает в сумматор 7.3.2, с выхода которого выдается сумма а31b12 + +а32b32 + а33b32 = d32, оно записывается в регистр 11.3.2. В регистр 3.3.2 записывается элемент с21. В ВМ 1.3.3 с выхода умножителя 5.3.3 выдается произведение а32, b31, оно поступает в сумматор 7.3.3, с выхода которого выдается сумма a31b11+a32b21, и она записывается в регистр 11.3.3. В регистры 3.3.3 и 4.3.3 записываются соответственно элементы b31 и а33.

Пятый такт. В ВМ 1.1.1 с выхода умножителя 5.1.1. выдается произведение d11c12, которое, пройдя сумматор 7.1.1, записывается в регистр 9.1.2. В регистр 3.1.1 записывается элемент с13. В ВМ 1.1.2 с выхода умножителя 5.1.2 выдается произведение d13c31, оно поступает в сумматор 7.1.2, с выхода которого выдается сумма d11c11 + +d13c31, она записывается в регистр 9.1.3. В регистр 3.1.2 записывается элемент с32. В ВМ 1.1.3 с выхода умножителя 5.1.3 выдается произведение a13b32, оно поступает в сумматор 7.1.3, с выхода которого выдается сумма a11b12 + a12b22 + a13b32 = d12, она записывается в регистр 11.1.3. В регистр 3.1.3 записывается элемент с21. В ВМ 1.2.1 в регистр 3.2.1 записывается элемент с23. С выхода умножителя 5.2.1 выдается произведение d22c22, которое пройдя сумматор 7.2.1 и элемент И 10.2.1, записывается в регистр 9.2.2. В ВМ 1.2.2 с выхода умножителя 5.2.2 выдается произведение d21c11, оно поступает в сумматор 7.2.2, с выхода которого выдается сумма d22c21 + d21c11, она записывается в регистр 9.2.3. В регистр 3.2.2 записывается элемент с12. В ВМ 1.2.3 с выхода умножителя 5.2.3 выдается произведение a23b33, оно поступает в сумматор 7.2.3, с выхода которого выдается сумма a21b13 + a22b23 + a23b33 = d20, она записывается в регистр 11.2.3. В регистр 3.2.3 записывается с31. В ВМ 1.3.1 в регистр 3.3.1 записывается элемент с33. С выхода умножителя 5.3.1 выдается произведение d33c32, которое, пройдя сумматор 7.3.1, записывается в регистр 9.3.2. В ВМ 1.3.2 с выхода умножителя 5.3.2 выдается произведение d32c21, оно поступает в сумматор 7.3.2, с выхода которого выдается сумма d32c33 + d32c22, она записывается в регистр 9.3.3. В регистр 3.3.2 записывается элемент с22. В ВМ 1.3.3 с выхода умножителя 5.3.3 выдается произведение a33b31, оно поступает в сумматор 7.3.3, с выхода которого выдается сумма a31b11 + a32b21 + a31b31 = d31, она записывается в регистр 11.3.3. В регистр 3.3.3 записывается элемент с11.

Шестой такт. Во входные регистры 3.1.1 и 4.1.1 ВМ 1.1.1 поступают элементы новых матриц АI *ВI . С выхода умножителя 5.1.1 выдается произведение d11c13, которое, пройдя сумматор 7.1.1, записывается в регистр 9.1.2. В ВМ 1.1.2 с выхода умножителя 5.1.2 выдается произведение d13c32, оно поступает в сумматор 7.1.2, с выхода которого выдается сумма d11c12 + d13c32, она записывается в регистр 9.1.3. В регистр 3.1.2 записывается элемент с33. В ВМ 1.1.3 с выхода умножителя 5.1.3 выдается произведение d12c21, оно поступает в сумматор 7.1.3, с выхода которого выдается сумма d11c11 + d13c31 + d12c21 = f11, которая, пройдя элемент И 10.1.3, поступает на выход устройства. В регистр 3.1.3 записывается элемент с22. Во входные регистры 3.2.1 и 4.2.1 ВМ 1.2.1 поступают элементы новых матриц. С выхода умножителя 5.2.1 выдается произведение d22c23, которое, пройдя сумматор 7.2.1, записывается в регистр 9.2.2. В ВМ 1.2.2 с выхода умножителя 5.2.2 выдается произведение d21c12, оно поступает в сумматор 7.2.2, с выхода которого выдается сумма d22c22 + d12c12, она записывается в регистр 9.2.3. В регистр 3.2.3 записывается элемент с13. В ВМ 1.2.3 с выхода умножителя 5.2.3 выдается произведение d23c31, оно поступает в сумматор 7.2.3, с выхода которого выдается сумма d22c21 + d21c11 + d23c31 = f21, она поступает на выход устройства. В регистр 3.2.3 записывается элемент с32. В ВМ 1.3.1 во входные регистры 3.3.1 и 4.3.1 поступают элементы новых матриц. С выхода умножителя 5.3.1 выдается произведение d33c33, которое, пройдя сумматор 7.3.1, записывается в регистр 9.3.2. В ВМ 1.3.2 с выхода умножителя 5.3.2 выдается произведение d32c22, оно поступает в сумматор 7.3.2, с выхода которого выдается сумма d32c21 + d32c22, она через элемент И 10.3.2 записывается в регистр 9.3.3. В регистр 3.3.2 записывается элемент с23. В ВМ 1.3.3 с выхода умножителя 5.3.3 выдается произведение d31c11, оно поступает в сумматор 7.3.3, с выхода которого выдается сумма d33c31 + d32c21 + d31c11 = f31, которая поступает на выход устройства. В регистр 3.3.3 записывается элемент с12.

Седьмой такт. В ВМ 1.1.2 с выхода умножителя 5.1.2 выдается произведение d13c33, оно поступает в сумматор 7.1.2, с выхода которого выдается сумма d11c13 + +d13c33, она записывается в регистр 9.1.3. В ВМ 1.1.3 с выхода умножителя 5.1.3 выдается произведение d12c22, оно поступает в сумматор 7.1.3, с выхода которого выдается сумма d11c12 + d13c32 + d12c22 = f12, она поступает на выход устройства. В регистр 3.1.3 записывается элемент с23. В ВМ 1.2.2 с выхода умножителя 5.2.2 выдается произведение d21c13, оно поступает в сумматор 7.2.2, с выхода которого выдается сумма d22c23 + +d21c13, она, пройдя элемент И 10.2.2, записывается в регистр 9.2.3. В ВМ 1.2.3 с выхода умножителя 5.2.3 выдается произведение d23c32, оно поступает в сумматор 7.2.3, с выхода которого выдается сумма d22c22 + d21c12 + d23c32 = f22, она поступает на выход устройства . В регистр 3.2.3 записывается элемент с33. В ВМ 1.3.2 с выхода умножителя 5.3.2 выдается произведение d32c23, оно поступает в сумматор 7.3.2, с выхода которого выдается сумма d33c33 + d32c23, она записывается в регистр 9.3.3. В ВМ 1.3.3 с выхода умножителя 5.3.3 выдается произведение d31c12, оно поступает в сумматор 7.3.3, с выхода которого выдается сумма d32c21 + d32c22 + d31c12 = f32, она поступает на выход устройства. В регистр 3.3.3 записывается элемент с13.

Восьмой такт. С выхода умножителя 5.1.3 выдается произведение d12c23, оно поступает в сумматор 7.1.3, с выхода которого выдается сумма d11c13 + d13c33 + d12c23 = f13, она пройдя элемент И 10.1.3, выдается на выход устройства. С выхода умножителя 5.2.3 выдается произведение, оно поступает в сумматор 7.2.3, с выхода которого выдается сумма d22c23 + d21c13 + d23c33 = f23, она, пройдя элемент И 10.2.3, поступает на выход устройства. С выхода умножителя 5.3.3 выдается произведение d31c13, оно поступает в сумматор 7.3.3, с выхода которого выдается сумма d33c33 + d32c23 + d31c13 = f33, она пройдя элемент 10.3.3, поступает на выход устройства.

На этом работа устройства по вычислению матрицы F = A˙B˙C заканчивается. Таким образом, заявляемое устройство выгодно отличается от прототипа, поскольку при той же производительности в заявляемом устройстве на n˙n регистров и триггеров меньше. (56) 1. Авторское свидетельство СССР N 1363248, кл. G 06 F 15/347, 1986.

2. Авторское свидетельство СССР N 1552200, кл. G 06 F 15/347, 1988.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения матриц | 1991 |

|

SU1835548A1 |

| Устройство для перемножения матриц | 1989 |

|

SU1839262A1 |

| Устройство для умножения матриц | 1991 |

|

SU1801224A3 |

| Устройство для треугольного разложения ленточных матриц | 1988 |

|

SU1587540A1 |

| Устройство для выполнения операций над матрицами | 1990 |

|

SU1741153A1 |

| Устройство для операций над матрицами | 1988 |

|

SU1575205A1 |

| Устройство для операций над матрицами | 1990 |

|

SU1802363A1 |

| Устройство для матричных операций | 1989 |

|

SU1777154A1 |

| Устройство для перемножения матриц | 1989 |

|

SU1705836A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении специализированных, в том числе и систолических устройств, предназначенных для выполнения операций над матрицами. Целью изобретения является сокращение аппаратурных затрат. Устройство для перемножения матриц содержит n n вычислительных модулей (n - разрядность обрабатываемых матриц), причем каждый вычислительный модуль содержит регистры 3, 4, 9 и 11, умножитель 5, элементы ИЛИ 6 и 8, сумматор 7, элементы И 10, 12 и 13 и триггер 14. 2 ил.

УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ МАТРИЦ, содержащее n · n вычислительных модулей (n - разрядность обрабатываемых матриц), причем первый, второй и третий информационные входы (i, 1)-го вычислительного модуля соединены соответственно с i-м информационным входом первой, второй и третьей групп устройства (i = 1, . . . , n), тактовый вход которого соединен с входом записи (i, 1)-го вычислительного модуля, второй и третий выходы каждого (i, j)-го вычислительного модуля соединены соответственно с вторым и третьим информационными входами (i, j + 1)-го вычислительного модуля (j = 1, . . . , n - 1), третий выход (i, n)-го вычислительного модуля соединен с i-м выходом устройства, при этом каждый вычислительный модуль содержит четыре регистра, умножитель, сумматор, триггер, три элемента И и два элемента ИЛИ, причем первый информационный вход вычислительного модуля соединен с информационным входом первого регистра, выход которого соединен с первым выходом вычислительного модуля и первым входом умножителя, второй вход которого соединен с выходом первого элемента ИЛИ, первый вход которого соединен с выходом второго регистра и вторым выходом вычислительного модуля, второй информационный вход которого соединен с информационным входом второго регистра, а третий информационный вход - с информационным входом третьего регистра, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с первым входом сумматора, второй вход которого соединен с выходом умножителя, а выход сумматора - с информационным входом четвертого регистра и первым входом первого элемента И, выход которого соединен с третьим выходом вычислительного модуля, а второй вход первого элемента И - с прямым выходом триггера и первым входом второго элемента И, второй вход которого соединен с выходом четвертого регистра, а выход второго элемента И - с вторым входом первого элемента ИЛИ, входы синхронизации всех регистров объединены и соединены с входом записи вычислительного модуля, отличающееся тем, что, с целью сокращения аппаратурных затрат, первый выход (i, j)-го вычислительного модуля, кроме (n, j)-х вычислительных модулей, соединен с первым информационным входом (i + 1, j + 1)-го вычислительного модуля, первый выход (n, j)-го вычислительного модуля - с первым информационным входом (1, j + 1)-го вычислительного модуля, четвертый выход (i, j)-го вычислительного модуля - с входом записи (i, j + 1)-го вычислительного модуля, а в каждом из вычислительных модулей вход записи соединен с входом триггера, прямой выход которого соединен с четвертым выходом вычислительного модуля, а инверсный выход - с первым входом третьего элемента И и с входом разрешения записи четвертого регистра, второй вход которого соединен с выходом четвертого регистра, а выход третьего элемента И - с вторым входом второго элемента ИЛИ.

Авторы

Даты

1994-01-30—Публикация

1990-10-19—Подача