Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении специализированных устройств, предназначенных для решения систем линейных уравнений.

Цель изобретения - расширение функциональных возможностей путем выполнения операций умножения матриц, вычисления определителя и элементов присоединенной матрицы.

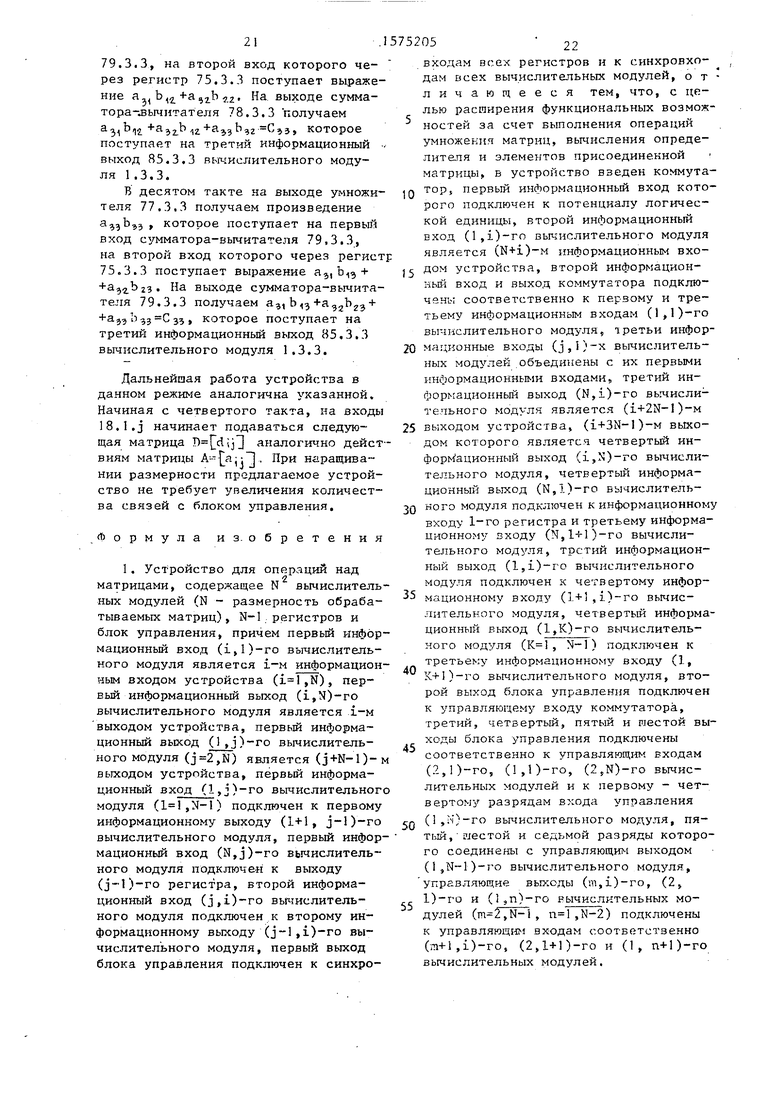

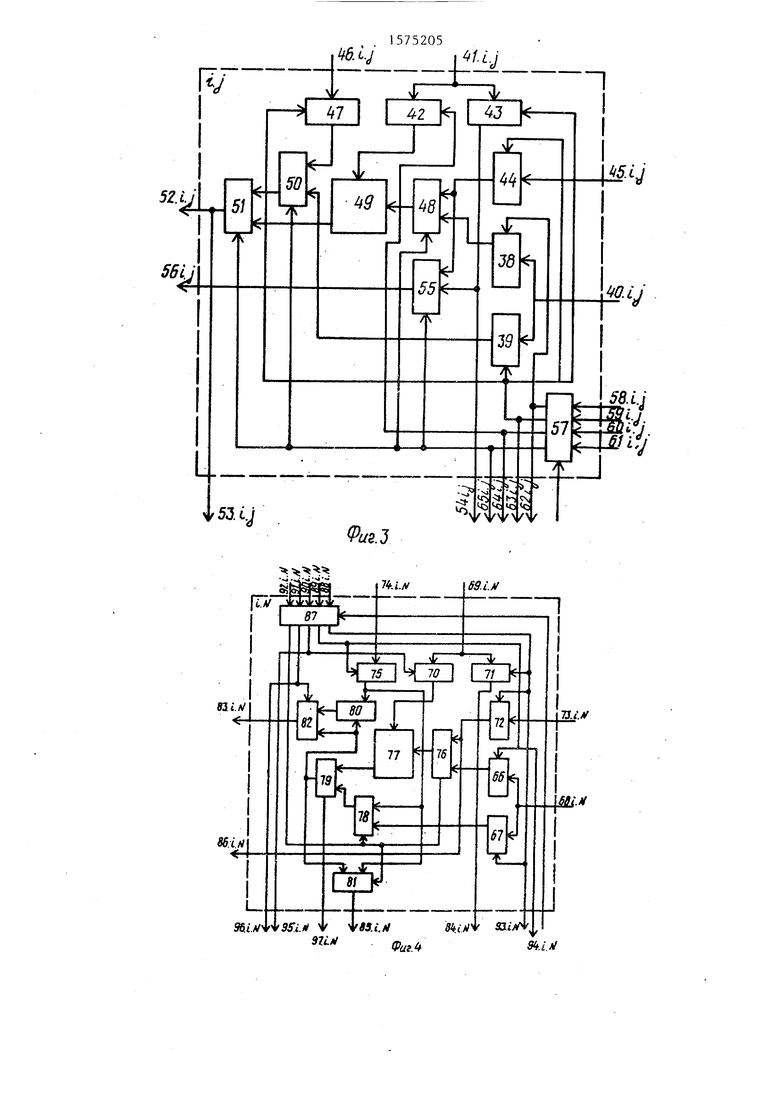

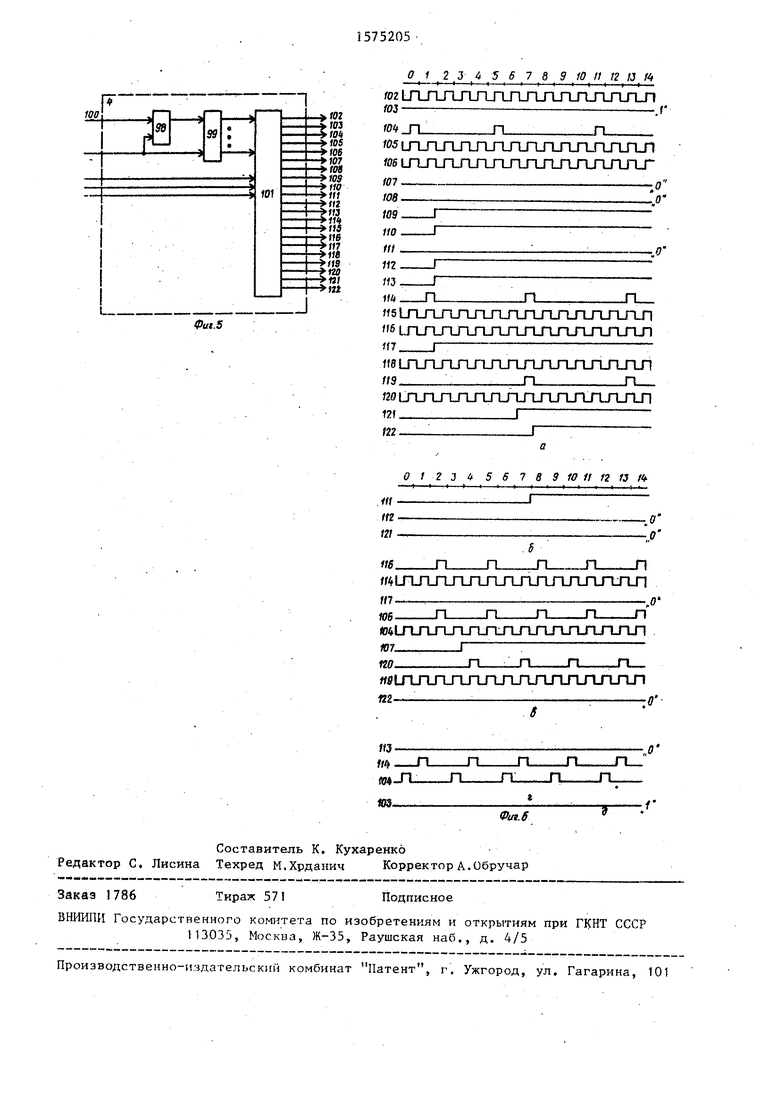

На фиг. 1 представлена структурная схема предлагаемого устройства для операций над матрицами; на фиг,2 - схема (lti)-ro вычислительного модуля; на фиг, 3 - схема (j, К)-го вычислительного модуля; на фиг. 4 - схема )-ro вычислитель- ного модуля ( ,K-I; ,N; N - размерность обрабатываемых матриц) ; на фиг,5 - блок управления, один из вариантов построения; на фиг,6 - диаграммы состояний выходов -блока управления в режимах решения систем линейных уравнений и обращения матриц (а), вычисления элементов присоединенной матрицы (б), перемножения матриц (в), LU-разложения матриц (г), вычисления определителя и элементов присоединенной матрицы (д).

СП

-vi

СД

ю

о

СП

Устройство для операций над матрицами (фиг.1) содержит матрицу (N - размерность обрабатываемых матриц) вычислительных модулей 1 , комму- татор 2, N-1 регистров 3, блок 4 управления. (1,1)-й (,N) вычислительны модуль содержит первый 5 и второй 6 регистры, первый 7 и второй 8 информационные входы, третий 9, четвертые 10 и пятый 11 регистры, третий информационный вход 12, первый коммутатор 13, делитепь 14, второй 15 и третий 16 коммутаторы, первый 17 и второй 18 информационные выходы9 умножитель 19, четвертый коммутатор 20, третий 21 и четвертый 22 информационные входы, семиразрядный регистр 23 управления, первый 24, второй 25, третий 26, четвертый 27, пятый 28, шестой 29, седь- мой 30 входные и первый 31, второй 32, третий 33, четвертый 34, пятый 35, шестой 36, седьмой 37 выходные разряды регистра управления, образующие управляющие вход и выход вычислитель- ного модуля, (j,К)-й вычислительный модуль (фиг. 3) (, , N-1) содержит первый 38 и второй 39 регистры, первый 40 и второй 41 информационные входы, третий 42, четвертый 43 и пятый 44 регистры, третий 45 и четвертый 46 информационные входы, шестой регистр 47, первый коммутатор 48, умножитель 49, второй коммутатор 50, сумматор-вычитатель 51, первый 52, третий 53, второй 55 и четвертый 56 информационные выходы, четырехразрядный регистр 57 управления, первый 58, второй 59, третий 60, четвертый Ы разряды управляющего входа, пер- вый 62, второй 63, третий 64 и четвертый 65 разряды управляющего выхода.

(j,N)-u (,N) вычислительный модуль (фиг.4) содержит первый 66 и второй 67 регистры, первый 68 и второй 69 информационные входы, третий 70, четвертый 71, пятый 72 регистры, третий 73 и четвертый 74 информационные входы, шестой регистр 75, первый коммутатор 76, первый умножитель 77, второй коммутатор 78, сумматор-вычи-. татель 79, второй умножитель 80, третий 81 и четвертый 82 коммутаторы, первый 83, второй 84, третий 85 и четвертый 86 информационные выходы, регистр 87 управления, первый 88, второй 89, третий 90, четвертый 91,

0 5 0

5

пятый 92 разряды управляющего входа, первый 93, второй 94, третий 95, четвертый 96 и пятый 97 разряды управляющего выхода.

Блок управления (фиг,5) содержит элемент И 98, счетчик 99, синхровход 100, ПЗУ микрокоманд 101, первый 102, второй 103, третий 104-110,-четвертый 111-113, пятый 114-117 и шестой 118-122 выходы. Синхровходами всех вычислительных модулей (не обозначены) являются входы разрешения записи регистров управления.

Устройство для операций над матрицами предназчено для решения систем N линейных уравнений методом Гаус- са-Жордана, умножения матриц размерности NxNj выполнения LU-разложения, вычисления обратной матрицы, определителя и присоединенной матрицы. При решении систем линейных уравнений, при вычислении обратной матрицы и элементов присоединенной матрицы выполняется обработка расширенной матрицы, размерности , которая представляет собой исходную матрицу размерности , к которой справа дописана матрица размерности N(M-N). Вычисление определителя и LU-разложение основаны на преобразовании исходной матрицы в треугольную.

При вычислении системы линейных уравнений к исходной матрице () справа дописывается S столбцов свободных членов (в этом случае ) и после того, как исходная матрица преобразована в единичную, на месте столбцов свободных членов получаем семейство решений данной системы уравнений. Число S при данной организации вычислений может быть любым натуральным. Вычисления производятся по следующим формулам:

0

,(

а Г: , ,2N;

5

(к-0

Kj КК

i,, К+2,.,.,N.

«W /л(. .-) a i ам a J а;к

«Ч -ч

При вычислении обратной матрицы к исходной матрице справа дописывается единичная матрица размерности (в этом случае ) и после того, как исходная матрица преобразована в единичную, на месте приписанной справа единичной получаем обрат5-1575205

ную. Вычисления выполняются по тем т.е. вычисляется обратная матрица и же формулам, что и решение систем параллельно определитель (det), a линейных уравнений.затем выдаваемые элементы обратной

При LU-разложении матриц выполня- матрицы умножаются на det. ется разложение данной квадратной матрицы А размерности N на две треугольные: нижнюю левую L и верхнюю правую U, такие что , причем на главной диагонали одной из треугольных матриц состоят единицы. Преобразование матрицы выполняется по алго-

При умножении матриц элеме ты матрицы-произведения вычисляются по формуле

10

CJJ

П а;кЬк{ .

ритму исключения Гаусса, в процессе которого получаются элементы {

- У ЧГ Ч .- . .

,2N; j,, K+2,...,N,

UKJ-Ј /aЈ° . 1;;-аГ

Рассмотрим работу устройства при вычислении обратной матрицы размерностью .

15

I

Условимся, что информация в реги стры принимается в начале такта по заднему Аронту синхроимпульса и опр делитель исходной матрицы не равен ну

„ лю. Итак исходная матрица 20

,2,...,N, i,, K+1,...,N.

Режим вычисления определителя отличается от режима LU-разложения тем, 25 что в процессе преобразования матрицы перемножаются элементы а, т.е.

А

lai

1я

чг

1гг

1ъг

4%

г

1зз

допигаем к ней справа единичную матрицу

атрицы умножаются на det.

При умножении матриц элементы матрицы-произведения вычисляются по формуле

матрицы умножаются на de

10

CJJ

П а;кЬк{ .

матрицы умножаются на det.

Рассмотрим работу устройства при вычислении обратной матрицы размерностью .

I

Условимся, что информация в регистры принимается в начале такта по заднему Аронту синхроимпульса и определитель исходной матрицы не равен нулю. Итак исходная матрица

чг

4%

А

lai

1гг

г

1я

1ъг

1зз

допигаем к ней справа единичную матрицу

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для матричных операций | 1989 |

|

SU1777154A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Устройство для разложения теплицевых симметричных матриц | 1990 |

|

SU1755295A2 |

| Устройство для перемножения матриц | 1989 |

|

SU1705836A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1981 |

|

SU1020833A1 |

| Устройство для вычисления скользящего спектра | 1988 |

|

SU1527642A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1989 |

|

SU1631556A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении специализированных матричных вычислителей. Целью изобретения является расширение функциональных возможностей устройства за счет выполнения умножения матриц, вычисления определителя и элементов присоединенной матрицы. Устройство содержит матрицу N х N вычислительных модулей, где N - размерность обрабатываемых матриц, коммутатор, блок управления и N-1 регистров. Работа устройства основана на преобразовании исходной либо расширенной матрицы в единичную методом Гаусса-Жордана (в режиме обращения матриц и решения систем линейных уравнений) или в треугольную по алгоритму исключения Гаусса (в режиме LV-разложения матриц). К особенностям работы устройства следует отнести систолическую организацию процесса вычислений и возможность простого наращивания размерности вычислительной среды. 3 з.п.ф-лы, 6 ил.

N

.01

det-.П «. -

Вычисление элементов присоединенной матрицы является объединением режимов вычисления обратной матрицы и определителя, так как A det--A 1 ,

Элементы матрицы С поступают на входы вычислительных модулей построчно со сдвигом на один такт, т.е. первая строка поступает на первый вход .с вычислительного модуля 1.1.1, начищим сигналам 11, поступающим с шестого и седьмого разрядов регистра управления 23.1.1, через коммутатор 16.1.1 поступает на первый 17.1. выход, а через коммутатор 15.1.1 по нуная с первого такта; вторая строка левому сигналу, поступающему с чет- поступает на первый вход вычисли- вертого разряда регистра управления тельного модуля 1.2.1, начиная с вто- 23.1.1, поступает на второй информа- рого такта; третья - на вход вычисли- 5Q ционный выход вычислительного модуля тельного модуля 1 .3 -, 1 , начиная с третьего такта. В первом такте элемент ,

принимается в регистр 5.1.1.

(°)

регистр 38.2.1 через коммутатор 48.2.1. Но единичному сигналу элемент (о)

Во втором такте элемент С Ј принима- 55 с(°) поступает На первый вход умно- ется в регистр 6.1.1, на выход- делиi

жителя А9.2.I.

теля li.1.1 получаем частное С /

(О)(,)

/С„ 11,2 12 которое по управляю30 В -

и получим расширенную матрицу С, над которой выполняется преобразование

щим сигналам 11, поступающим с шестого и седьмого разрядов регистра управления 23.1.1, через коммутатор 16.1.1 поступает на первый 17.1. выход, а через коммутатор 15.1.1 по нулевому сигналу, поступающему с чет- вертого разряда регистра управления 23.1.1, поступает на второй информа- ционный выход вычислительного модуля

(°)

регистр 38.2.1 через коммутатор 48.2.1. Но единичному сигналу элемент (о)

с(°) поступает На первый вход умно-

(°)

i

с(°) поступает На первый вход умно-

жителя А9.2.I.

В третьем такте элемент С поступает в регистр 6.I.I. На выходе

делителя 14.1.1 получаем частное

С,з С °( И1Э С15 , которое по управляющим сигналам II через коммутатор 16.1.1 поступает на первый выход 17.1.1 л через коммутатор 15,1.1 по нулевому сигналу поступает на второй информационный выход вычислительного модуля 18.1.1. Элемент

(°) Сгг принимается в регистр 39.2.I,

(0)

а в регистр 42.2.1 принимается С12 /

/См . На выходе умножителя 49.2.1

(о) .(о) (о) получаем произведение С 1г /С м С 41 ,

которое поступает на вход сумматора,М

С iv С

, в регистр 39.2,1 - элемент

С ,j . В регистр 42.2,1 принимается (о) „(о)

и

С 2 на выходе умножителя 49.2.1

„(о) . (о) (о) получаем произведение С14 /С „ С ,

которое поступает на второй вход сумматора-вычитателя 51,2,1, на пер- п вый вход которого поступает элемент

(о) С г4 . На выходе сумматора-вычитателя

С24 В регистр 42.3.1 принимается 15 (о) (о)

С 15 /С „ , в регистр 39.3.1 - элемент

,00

Сээ , на выходе умножителя 49.3.1 повычитателя 51.2.1 его выходе по- лучаем произведение С™ С , лучаем выражение С 12 Сг2 -С,г /С„ 20 на выходе сумматора вычитателя 51.3.1«Я -1

LI

,СО „№)

д°)

,t°)

В четвертом такте элемент принимается в регистр 6.1.1. На первом 17.1.1 и на втором 18.1.1 информационных выходах вычислительного моду(0) , (о)

ля 1.1.1 получаем частное С14 /С С 4 . В регистр 42.2,1 поступает

с /сн в Регистр 39.2.1 - элеi0мент С 2з , На выходе умножителя

, (о) (о)

/С j С 21 , которое поступает на

второй вход сумматора-вычитателя 51.2.1, на первый вход которого по(0)

ступает элемент С2Э . На выходе сумматора-вычитателя 51.2.1 получаем

чаем частное С л /C2j -гъ

Элемент

-С., С -С„ /CV С1 -1„. В ре- гистр 6.1.2 принимается элемент 25 С 23 вычислительного модуля 1.1..2,

на первом 17.1.2 и втором 18.1.2 информационных выходах которого полу- М ,„«

23

30 с а4 принимается в регистр 38.2.2,

(О а элемент С,4 --в регистр 2.1.

В шестом такте Су$ принимается в

регистр 6.1.1 вычислительного лоду- 35 ля 1.1.1, на первом 17.1.1 и втором 18.1.1 информационных выходах которого получаем частное С 1б /С н С 6 . На выходе умножителя 49.2.I получаем произведение С15 /С 1( С 1г которое

регистр 6.1.1 вычислительного лоду- 35 ля 1.1.1, на первом 17.1.1 и втором 18.1.1 информационных выходах которого получаем частное С 1б /С н С 6 . На выходе умножителя 49.2.I получаем произведение С15 /С 1( С 1г которое

с« С13 с« C2i с,23 в Регистр поступает на второй вход сумматора42.3.1 поступает С J , в регистр (вычитателя 51.2.1, на первый вход ко(0) торого поступает элемент С2 На вы39.3.1 - элемент С , навыходе ум- д§ ходе сумматора-вычитателя 51.2.1 поножителя 49.3.1 получаем произведение лучаем выражение с С2° -С /С,,

W /„(°) ) ... (о). „ п ,

С .На выходе умножителя 49.3.1

получаем произведение С /С,, С31 ,

г /С ,, С з, , на выходе сумматоравычитателя .51 .3.1 получаем С ,2 (о)

31 132

()

CW -г(о /г(0) V эг - г ь «

(1)

92

Элемент

50

которое поступает на второй вход сумСЈ -1И поступает в регистр 5.1.2.матора-вычитателя 51.3.1, на первый

В пятом такте элемент C jпринимает-ВХ°Д которого поступает сЈ . На выся в регистр 6.1.1 вычислительного 55xo«e сумматора-вычитателя 51.3.1 прмодуля 1.1.1 На первом 17.1.1 и вто-лучаем С 1 С -С С( . На ром 18.1.1 информационных выходах ко-1

(о) (0) первом 17.1.2 и втором 18,1.2 инфорторого получаем частное С 15 /С „ -мационных выходах вычислительного

8

,М

С iv С

, в регистр 39.2,1 - элемент

С ,j . В регистр 42.2,1 принимается (о) „(о)

и

С 2 на выходе умножителя 49.2.1

„(о) . (о) (о) получаем произведение С14 /С „ С ,

которое поступает на второй вход сумматора-вычитателя 51,2,1, на пер- п вый вход которого поступает элемент

(о) С г4 . На выходе сумматора-вычитателя

С24 В регистр 42.3.1 принимается 15 (о) (о)

С 15 /С „ , в регистр 39.3.1 - элемент

,00

Сээ , на выходе умножителя 49.3.1 по,СО „№)

д°)

,t°)

чаем частное С л /C2j -гъ

Элемент

-С., С -С„ /CV С1 -1„. В ре- гистр 6.1.2 принимается элемент 5 С 23 вычислительного модуля 1.1..2,

на первом 17.1.2 и втором 18.1.2 информационных выходах которого полу- М ,„«

23

0 с а4 принимается в регистр 38.2.2,

(О а элемент С,4 --в регистр 2.1.

В шестом такте Су$ принимается в

регистр 6.1.1 вычислительного лоду- 5 ля 1.1.1, на первом 17.1.1 и втором 18.1.1 информационных выходах которого получаем частное С 1б /С н С 6 . На выходе умножителя 49.2.I получаем произведение С15 /С 1( С 1г которое

модуля 1.1.2 получаем частное С

24

/ лительного модуля 1.1.2 получаем чл- (0

стное С /С

()

, U)

гг сгб На вых°Де сумма тора-вычитателя 51.2.2 получаем

/С21 С 24 На выходе сумматора-яычи(г) (i) тателя 51.2.2 получаем С„ С 3 -С 23 /С2г. С% Элемент С 12 принимается в регистр 38.3.2, а элемент сумматора-вычитателя 5.3.2 получаем (О. .„(г) „(О „(О ,„Ы „(О

г(1) -ги) -гы /гы и 5 Ь35 ь zs гг

(О С ЭЈ . На выходе

л

- в регистр 2.1,

10

выражение Сн С-г /с ог ciz

В седьмом такте на выходе умножителя 49.2.1 получаем произведение „ (о) .„(о) (о) ь (6 /с 11 с 21 которое поступает на

второй вход сумматора-вычитателя 51.2.1, на первый вход которого по(о) ступает элемент С26 . На выходе сумматора-вычителя 51.2.1 получаем выра(о) (о) жение С 26 , на выхо10

которое поступает на первый информационный выход 52.3.2. На выходе делителя 14.1.3 получаем частное С3 /

, tt) (э)

15 /Сэз з4 которое поступает на первый 17.1.3 и второй 18.1.3 информационные выходы вычислительного модуWля 1.1.3. Элемент С,э принимается

20

С

(о) и

де умножителя 49.3.1 получаем произ„(ol ,„(о) (с) ведение С(5 кот°Рое по

ступает на второй вход сумматора-вычитателя 51.3.1, на первый вход кото(rt рого поступает С Ъ5 . На выходе сумчатора-вычитателя 51.3.1 получаем

С2 -С(5-с2/С(. С .Наперво

получаем частное /С С . На выходе сумматора-вычитателя 51.2.2 получаем С и -С И /С й- С0)

25

в регистр 66.2.3 вычислительного моd) дуля 1.2.3, элемент С15 - в регистр

В девятом такте на выходе сумматора вычитателя 51.3.2 получаем выраже.М

35

ние с;с с;с -с;с /с

,ч

Z5

(1)

гг.

0

, (2)

35 С35 сг . с--я. которое поступает на первый информационный 30 выход 52.2.2. На выходе сумматора- вычитателя 51.3.2 получаем выражение

cS . которое поступает на первый информационный выход 52.3.2 вычислительного модуля

35

() Элемент С , принимается в регистр

.а)

(г) (z) (г) (г) чаем выражение С14 -С /С v С чг,

В восьмом такте на выходе умножило) (о) (о) теля 49,3.1 получаем СЭГ 16 /С ,

которое поступает на второй вход сумматора-вычитателя 51.3.1, на пер(о вый аход которого поступает С5, . На

выходе сумматора-вычитателя получаем выражение СЈ -C(,° /eft ,

55 ние С26 /С22 кот°Р°е поступает

которое поступает на первый информационный выход вычислительного модуля на первый информационный выход 52.3.2

вычислительного модуля 1.3.2. На выходе делителя 14.1.3 получаем част1.3.1. На первом 17.1.2 и втором 18.1.2 информационных выходах вычис

-1575205 10

/ лительного модуля 1.1.2 получаем чл- (0

стное С /С

()

, U)

гг сгб На вых°Де сумчима тора-вычитателя 51.2.2 получаем

сумматора-вычитателя 5.3.2 получаем „(г) „(О „(О ,„Ы „(О

г(1) -ги) -гы /гы и 5 Ь35 ь zs гг

(О С ЭЈ . На выходе

сумматора-вычитателя 5.3.2 получаем „(г) „(О „(О ,„Ы „(О

выражение Сн С-г /с ог ciz

которое поступает на первый информационный выход 52.3.2. На выходе делителя 14.1.3 получаем частное С3 /

, tt) (э)

/Сэз з4 которое поступает на первый 17.1.3 и второй 18.1.3 информационные выходы вычислительного модуWля 1.1.3. Элемент С,э принимается

в регистр 66.2.3 вычислительного моd) дуля 1.2.3, элемент С15 - в регистр

В девятом такте на выходе сумматора вычитателя 51.3.2 получаем выраже.М

35

ние с;с с;с -с;с /с

,ч

Z5

(1)

гг.

0

, (2)

35 С35 сг . с--я. которое поступает на первый информационный 0 выход 52.2.2. На выходе сумматора- вычитателя 51.3.2 получаем выражение

cS . которое поступает на первый информационный выход 52.3.2 вычислительного модуля

5

которое поступает на первьй информа

«)

ционный выход 83.2.3. Элемент С2з

принимается в регистр 66.3.3, элемент

(О()

- в регистр 2.1, элемент Ci4

в регистр 2.2,

В десятом такте на выходе сумматора-вычитателя 51.3.2 получаем выраже55 ние С26 /С22 кот°Р°е поступает

на первый информационный выход 52.3.2

1

„(z) . U) (з)

ное С j6 /C 33 c 36 которое поступает на первый 17.1.3 и второй 18.1.3 информационные выходы вычислительно модуля 1,1.3. Ча выходе сумматора-в чителя 79.2.3 получаем выражение rW „W , „fe „(

lj

н -СМ/СЭЭ- С12 С,4 , которое

поступает на первый информационный выход 83.2.3. На выходе сумматора-вы читателя 79.3,3 r/олучаем выражение

() (г) , (г) (а)

11 С vi с зз С г3 которое поступает на первый информационный выход 83.3.3 вычислительного модуля 1.3.3.

(V Элемент С ,5 принимается в регистр

В одиннадцатом такте на выходе сумматора-вычитателя 79.2,3 получаем

выражение С -С С% -С% ,

которое поступает на первый информационный выход 83.2.3 вычислительного модуля 1.2.3. На выходе сумматора- вычнтателя 79.3.3 получаем выражение

,W

,to

,(г) „(2)

С -С ,5 /С„- С23 , которое поступает на первьй информационный выход 83.3.3 вычислительного модуля 1,3.3

(2)

Элемент С

26

принимается в ре-

гистр 2.2,

В двенадцатом такте на выходе сумматора вычитателя 79.3.3 получаем

г) (г) , (г) (г) (5) выражение С 26 -С Э6 /С35 Сгз С 2$

На этом вычисление обратной матрицы заканчивается. Начиная с восьмого такта на первых информационных выходах вычислительных модулей 1.1. Т, 1.2.3 и 1,3.3 появляются элементы обратной матрицы

На выходах устройства получаются элементы обратной матрицы по строкам т.е. на выходе вычислительного модуля 1.1.3 появляются элементы третьей строки, на выходе вычислительного модуля 1.2.3 - первой, на выходе вычислительного модуля 1.3.3 - второй строки.

Для общего случая N выходов распределение строк следующее: 1-я

12

5

0

5

0

5 строка результата выдается с + вы- хода (для ,2,...,N-1), а N-я строка - с. первого выхода.

Сразу же после ввода первой строки исходной матрицы, т.е. в данном примере с седьмого такта, можно начинать вводить следующую исходную матрицу D.

При решении систем линейных уравнений в качестве элементов матрицы В подаются свободные члены заданной системы уравнений. Тогда на выходе получаем семейство решений этой сясг

темы уравнений. Столбец С , J является решением системы при столбце

свободных членов bjt J , столбец

Г () )

С ;5 J - решением при столбце свободных членов b;2J и т.д.

Рассмотрим работу устройства при LU-разложении матриц размерности .

В гервом такте элемент принимается в регистр 5.1.1 вычислительного модуля 1.1.1. Во втором так(о) те элемент а принимается в регистр

лучаем частное а /а 11,2 , которое по сигналу 11 через коммутатор 16,1.1 и нулевому сигналу через коммутатор 15.1.1 поступает соответственно на первый 17.1.1 и второй 18.1.1 информационные выходы вычислительного модуля 1.1.1. Элемент 1

21

-г

принимается в регистр 38.2.1.

В третьем такте элемент а °3 принимается в регистр 6.1.1, на выходе делителя 14.1.1 получаем частное

(« , (о) тт W а О аи о кот°Р°е поступает на

перлый 17,1.1 и второй 18.1.1 информационные выходы вычислительного модуля 1,1,1. Элемент а

(о)

принимается

0

5

в регистр 39.2.1 и через коммутатор 50.1.S подается на первый вход сумматора 51,1.1. В регистр 42.2.1 при(0) , (о)

нимается а ,2 /а , на выходе умножителя 49.2.1 получаем произведение

to /Q(°

к.

/av а

(0)

21 , которое поступает на

второй вход сумматора-вычитателя 51.2.If на выходе которрго получаем

выражение a g -a1 1 /a(J a(o)

которое поступает на первый информационный выход 52.2.1 вычислительного

модуля 1.2.1. Элемент а 1Э, принимается в регистр 38.3.1.

В четвертом такте элемент

принимается в регистр 39.2.1, а в

/ о о 1(° / (о)

регистр 4/ ./. I,принимается а„ /а ,

На выходе умножителя 49.2.1 получаем

(о , (о) (о) произведение а /а а 21 , которое

поступает на второй вход сумматора- вычитателя 51.2.1, на выходе которого получаем выражение а

О) )

X а

°) „«)

23

О

/а

(о)

2i а 23 к°торое поступает на первый информационный выход 52.2.1 вычислительного модуля 1.2.1. Элемент

/о) аъг принимается в регистр 39.3.1,

а в регистр 40.3.1 принимается а ,„ /

.()

/а . На выходе умножителя 49.3.1

(о) , (о) (в) получаем произведение а 12 /a i а }|) ,

которое поступает на второй вход .сумматора-вычитателя 51.3,1, на выходе которого получаем выражение (о) (о)

а(; -а« -а /а

гг

ъг

12

31

, которое поступает на первый информационный выход 52.3.1 вычислительного модуля

В пятом такте элемент а

(°)

33 принимается в регистр 39.3.1, а в регистр

(о) , fo) & /а .

(о) н

которое поступает на второй вход суммато- ра-вычитателя 51.3.1, на выходе которого получаем выражение а(° -а /

- (о) (о) (I) /а. а31 3,, которое поступает на

первый информационный выход 52.3.1 вычислительного модуля .3.1 Элемент

а2 принимается в регистр 6.1.2. На выходе делителя 14.1.2 получаем часта

(О , (О

(г)

ез

/я п VV /ааг -и 25

кото.ое поступа

ет на первый 17.1.2 и второй 18.1.2 ( информационные выходы вычислительного

модуля 1.1.2. Элемент аъг 1,а принимается в регистр 38.2.2.

В пестом такте элемент а ъЪ принимается в регистр 39.2.2, а в регистр 10 42.2.2 принимается а , /аг . На выходе умножителя 49.2.2 получаем проЫ , (О (О

изведение а гз /а гг- а Л2 , которое поступает на второй вход сумматора-вы- 15 читателя 51.2.2, на выходе которого

(г) (1) (А) . получаем выражение а33 а,3 -агъ /

(О „W ,ь

/а

nej

ля I.2.2.

22 -зг которое поступает на 20 первый выход вычислительного модуБ седьмом такте элемент а -э5

принимается в регистр 5.1.3 и через коммутатор 16.1.3 поступает на первый информационный выход I7.I.3 вычислительного модуля I.I.3. Начиная с четвертого такта, можно подавать элементы следующей матрицы, обработка которой выполняется аналогично.

В режиме вычисления определителя работа устройства выполняется аналогично режиму LU-разложения матриц. Отличие заключается в том, что при

вычислении определителя, в четвертом такте в регистр 11.1.2 с четвертого информационного выхода 22.1.1 вычислительного модуля I . I . l принимается

(о) , (о) а 1( det , которое поступает на

второй вход умножителя 19.1.2, на первый вход которого через коммутатор

13 из регистра 5.1.2 поступает а

0)

гг

На выходе умножителя 19.1.2 получаем

(-0 о1 , (л)

произведение а 2г . det det , ко- i

торор поступает ча первый информационный выход 17.1.2 вычислительного модуля 1.1.2. В седьмом такте в регистр 11.1.3 с четвертого информационного выхода 22.1.2 вычислительного модуля 1.1.2 принимается det(l , который поступает на второй вход умножителя

(О

элемент а ъъ . На выходе умножителя

15 19.1.3 получаем произведение а с det

U)

«

det , которое по нулевому сигналу через коммутатор 20.1,3 поступает на четвертый информационный выход 22.1.3 вычислительного модуля 1.1.3.

В режиме вычисления элементов присоединенной матрицы работа устройства выполняется аналогично режиму вычисления обратной матрицы. Отличие заключается в том, что при вычислении элементов присоединенной матрицы в четвертом такте в вычислительном модуле 1.1.2 элемент,С у по управляющему сигналу 00, поступающему с четвертого и пятого разрядов регистра управления 23.1.2, через коммутатор 13.1.2 поступает на первый вход умножителя 19.1,2, где умножается на det(0 поступающий на второй вход , умножителя 19.1.2. С входного регистра 11.1.2 и на выходе умножителя 19,1.2 получаем det который по нулевому сигналу через коммутатор

() Элемент С ъъ по управляющим сигналам

00 через коммутатор 13.1.3 поступает на первый вход умножителя 19.1.3, где умножается на det и получаем det г который поступает на третий

через коммутатор 82„3.3 по нулевому

15/520516

сигналу, поступающему с четвертого выхода регистра 87.2.3 управления поступает на первый информационный выход 83.2.3 вычислительного модуля 5 1.2.3. В девятом такте на выходе , сумматора-вычитателя 79.2.3 получаем

выражение

10

15

20

25

35

С(0

L н

-С

& 1„Ю

ъ

/с

ъъ

,ta

i

«р

Ы 4

которое поступает на первый вход умножителя 80.2.3, на выходе которого

, (г) (г (г получаем выражение (С -С /С,3 f

г(г) г(ъ}

Ь13 Jdet с, , которое по нулевому

сигналу через коммутатор 82.2.3 поступает на первый информационный выход 83.5,3 вычислительного модуля )1,2,3, На выходе умножителя 80.3.3 в девятом такте получаем CJj , которое по нулевому сигналу поступает на первый информационный выход 83.3.3 вычислительного модуля 1.3.3. В десятом такте на выходе умножителя 80.2,3

W „Ю /- v

30

40

(С ,с С 35 /С

1 15

ъъ

получаем выражение

W N , (2) ()

С „ )det C ,,5 которое поступает

на первый информационный выход 83,2.3 вычислительного модуля 1.2.3. На выходе сумматора-вычитателя 79,3.3 по) () ,„() (г)

лучаем выражение См .W

-С

ъ

/с

W

гъ

С

«4

которое поступает на первый

информационный вход умножителя 80.2,3 на выходе которого получаем выражение Д

(С™ -С(1) W

/г С2)

/(j

гг

)

d.tw-cg

которое поступает на первый информа- ционньй выход 83.3.3 вычислительного модуля 1.3.3.

Рассмотрим работу устройства при умножении матриц размерности .

42

1гг

аэг

а2э

из

В первом такте на второй информационный вход 8.1.1 вычислительного модуля 1.1.1 поступает элемент а 19, который принимается во входной регистр 10.1.1 и по нулевому сигналу, поступающему с четвертого разряда регистра 23.1.1 управления, через коммутатор 15.1,1 поступает на информационный выход 18,1.1.

Во втором такте элемент а, принимается в регистр 43.2.1, элемент

ыражение

С(0

L н

-С

& 1„Ю

ъ

/с

ъъ

,ta

i

«р

Ы 4

5

0

5

которое поступает на первый вход умножителя 80.2.3, на выходе которого

, (г) (г (г получаем выражение (С -С /С,3 f

г(г) г(ъ}

Ь13 Jdet с, , которое по нулевому

сигналу через коммутатор 82.2.3 поступает на первый информационный выход 83.5,3 вычислительного модуля )1,2,3, На выходе умножителя 80.3.3 в девятом такте получаем CJj , которое по нулевому сигналу поступает на первый информационный выход 83.3.3 вычислительного модуля 1.3.3. В десятом такте на выходе умножителя 80.2,3

W „Ю /- v

0

(С ,с С 35 /С

1 15

ъъ

получаем выражение

W N , (2) ()

С „ )det C ,,5 которое поступает

на первый информационный выход 83,2.3 вычислительного модуля 1.2.3. На выходе сумматора-вычитателя 79,3.3 по) () ,„() (г)

лучаем выражение См .W

-С

ъ

/с

W

гъ

С

«4

которое поступает на первый

5

информационный вход умножителя 80.2,3, на выходе которого получаем выражение Д

(С™ -С(1) W

/г С2)

/(j

гг

)

d.tw-cg

ко

торое поступает на первый информа- ционньй выход 83.3.3 вычислительного модуля 1.3.3.

Рассмотрим работу устройства при умножении матриц размерности .

а - в регистр 1041.1 и по нулевому сигналу через коммутатор 15.1.1 поступает на информационный выход 18.2.1, а элемент а43 поступает на информационный выход 18.1.2.

В третьем такте элемент а15 пересылается в вычислительный модуль 1.3.1 и принимается в регистр 42.3.1, элемент а - в регистр 42.2.1, элемент а - в регистр 9.1.1. Элемент

71575205 18

агэ принимается в регистр A3.2.2, сумматора-вычитателя 51.2.1 получаем элемент а гг - в регистр 9.1.2, а эле- выражение а „ , которое по- мент в регистр 10.1.3.ступает на третий информационный выВ четвертом такте на третий инфор- ход 53.2.1. Элемент Ъэ, поступает в мационный вход 12.1.1 вычислительно- регистр 44.3.1. На выходе умножитего модуля 1.1,1 поступает элемент b и , который принимается в регистр 11.1.1. На выходе умножителя IP. 1,1 получаем произведение а««Ъ« , которое поступает на третий информационный выход 21,1.1 вычислительного модуля 1.1.1. Элемент Ь« через коммутатор 20.1.1 поступает на четвертый выход 22.1.1 вычислительного модуля 1.1.1. Элемент а21 принимается в регистр 9.1.2, элемент аг2 принимается в регистр 42.2.2, элемент принимается в регистр 42.3.2. Элемент принимается в регистр 43.2,3, а элемент а 32 - в регистр 10.1.3.

В пятом такте элемент Ь12 принимается в регистр 11.1.1, на выходе умножителя 19.1.1 получаем произведеля 49.3.1 получаем произведение а,Ьг1 , которое поступает на второй вход сумматора-вычитателя 51.3.1,

10 на первый вход которого поступает выражение амЬ„, . На выходе сумматора-вычитателя 5i.3.l получаем выражение а,, Ь11 . +апЪ П14 , которое поступает на третий информа15 ционный выход 53.3.1 вычислительного модуля 1.3.1. На выходе умножителя 19.1.2 получаем произведение , которое поступает на третий информационный выход 21.1.2 вычислительного

20 модуля 1.1.2. На выходе умножителя 49.2.2 получаем произведение a/2jb21 , которое поступает на второй вход сумматора-вычитателя 51.2.2, на первый

вход которого через регистр 47.2,2 ние &щЪ, которое поступает на тре- 25 поступает произведение а2,Ъ, . На вы- тий информационный выход 21.1.1 вы- ходе сумматора-вычитателя 51.2.2 пот числительного модуля .1,1. Элемент лучаем выражение +аиЬ21 , ко- Ье1 принимается в регистр 44.2.1. На торое поступает на третий информа- выходе умножителя 49... получаем ционный выход 53.2.2 вычислительного произведение , которое поступа- 30 модуля 1.2.2. На выходе умножителя ет на второй вход сумматора-вычитате- 19.1.3 получаем произведение a5ib , ля 51.2.1. Произведение при- которое поступает на третий информа- нимэется в регистр 47.2.1 и через коммутатор 50.2.1 подается Яд первый вход сумматора-вычитателя 51.2.1, на выходе которого получаем выражение +а12 Ь21 , которое поступает на третий информационный выход 53.2.1 вычислительного модуля 1.2.1. На выходе умножителя 19.1.2 получаем про- до 51.2.I на первый вход которого через изведение а21Ь4 , которое поступает регистр 47.2.1 поступает произведение на третий информационный выход 21.1.2 анЪ . На выходе сумматора-вычитате35

ционный выход 21.1.3 вычислительного ко дуля 1.1.3.

В седьмом такте элемент Ь2Э принимается в регистр 44.2.1. На выходе умноя-ителя 49.2.1 получаем произведение которое поступает на второй вход сумматора-вычитателя

вычислительного модуля 1.1.2. Элемент а Э1 принимается в регистр 9.1.3, элемент а 52 в регистр 70.2.3, а элемент аэз в регистр 70.3.3.

В тестом такте элемент Ь принимается в регистр 11.1.1. На выходе умножителя 19.1.1 получаем произведение , которое поступает на третий информационный выход 21.1.1 вычислительного модуля 1.1.1. Элемент Ьаг принимается в регистр 44.2.1. На выходе умножителя 49.2.1 получаем произведение а12Ь2г, которое поступает на второй вход суммато-, ра-вычитателя 51.2.1, на первый вход которого через регистр 47.2.1 поступает произведение На выходе

ля 49.3.1 получаем произведение а,Ьг1 , которое поступает на второй вход сумматора-вычитателя 51.3.1,

на первый вход которого поступает выражение амЬ„, . На выходе сумматора-вычитателя 5i.3.l получаем выражение а,, Ь11 . +апЪ П14 , которое поступает на третий информационный выход 53.3.1 вычислительного модуля 1.3.1. На выходе умножителя 19.1.2 получаем произведение , которое поступает на третий информационный выход 21.1.2 вычислительного

модуля 1.1.2. На выходе умножителя 49.2.2 получаем произведение a/2jb21 , которое поступает на второй вход сумматора-вычитателя 51.2.2, на первый

вход которого через регистр 47.2,2 поступает произведение а2,Ъ, . На вы- ходе сумматора-вычитателя 51.2.2 пот лучаем выражение +аиЬ21 , ко- торое поступает на третий информа- ционный выход 53.2.2 вычислительного модуля 1.2.2. На выходе умножителя 19.1.3 получаем произведение a5ib , которое поступает на третий информа- 51.2.I на первый вход которого через регистр 47.2.1 поступает произведение анЪ . На выходе сумматора-вычитате

ционный выход 21.1.3 вычислительного ко дуля 1.1.3.

В седьмом такте элемент Ь2Э принимается в регистр 44.2.1. На выходе умноя-ителя 49.2.1 получаем произведение которое поступает на второй вход сумматора-вычитателя

ля 51.2.1 получаем выражение + а,2Ь2Э, которое поступает на третий

информационный выход 53.2.1 вычислительного модуля 1.2.1. Элемент bg2 поступает в регистр 44.3.1. На выходе умножителя 49.3.1 получаем произведение i, ,b, , которое поступает на второй вход сумматора-вычитателя 51.3.1, на первый вход которого поступает выражение а,э Ь аЪ2з . На выходе сум- матора-вгчитаетля 51.3.1 получаем выражение а 1( , +а12 Ьгг +а,э 2, i

которое поступает на третий информационный выход 53.3.1 вычислительного модуля 1.3.1. На выходе умножителя 19.1.2 получаем произведение которое поступает на третий информационный выход 21.1,2 вычислительного- ходе умножителя 49.3.2 получаем промодуля 1.1.2. На выходе умножителя 49.2.2 получаем произведение аг4Ь44, которое поступает на второй вход суммлтора-вычитателя 51.2.2, на первый вход которого через регистр 47.2.2 поступает произведение . На выходе сумматора-вычитателя 51.2.2

получаем выражение а71Ь14+а

22°22.5

которое поступает на третий информационный выход 53„2.2 вычислительного модуля 1.2.2, На выходе умножителя

На выходе сумматора-вычитателя 51.3.2 получаем выражение +а2гЬ2( + +а23Ъ31 Сц, которое поступает на третий информационный выход 53.3.2 вычислительного модуля 1.3.2. На выходе умножителя 19.1.3 получаем про- изведение а5, Ь14, которое поступает на третий информационный выход

.I.I,3вычислительного модуля 1.1.3. На выходе умножителя 77.2.3 получаем произведение ,,, которое поступает на первый вход сумматора-вычитателя 79,2.3, на второй вход которого через регистр 75.2.3 и коммутатор 78.2.3 поступает произведение аЭ1Ь1( . На выходе сумматора-вычитателя 79.2.3 получаем выражение , которое поступает на третий информационный выход 85.2.3 вычислительного модуля 1.2.3,

В восьмом такте элемент b3J поступает в регистр 44.3.1. На выходе умножителя 49.3.1 получаем произведе10

15

на третий информационный выход 31.1.3 вычислительного модуля 1.1,3. На выходе умножителя 77.2.3 получаем произведение , которое поступает на первый вход суммагора-вычитателя .3, на второй вход которого через

20 регистр 75.2.3 поступает произведение a fbtfc а выходе сумматора-вычитателя 7Ч.2.3 получаем выражение +а которое поступает на третий информационный выход 85,2.3

25 вычислительного модуля 1.3.2. На выходе умножителя 77.3.3 получаем произведение , которое поступает на первый вход сумматора-вычитателя

Ь +аъгЪы На выходе сумматора- вычитателя 79,3.3 получаем igib + +a3zb f +а м Ь3, С-Э1 , которое поступает на третий информационный выход 85.3.3 вычислительного модуля 1.3.3. В девятом такте на выходе умножителя 49.3.2 получаем произведение , которое поступает на второй вход сумматора-вычитателя 51.3.2, 40 на первый вход которого через регистр 47.3.2 поступает выражение аг 1$ На выходе сумматора- вычитателя 51.3.2 получаем аг1Ь13 + +a42b23+а2 Ь33 23 которое поступает

35

ние а15Ьэ, которое поступает на второй вход сумматора-вычитателя 51.3.1, на первый вход которого поступает выражение ач1 Ь19+а гЬгэ . На выходе сум- 45 на третий информационный выход 53.3.2

матора-вычитателя 31.3.1 получаем ап ь +а«ь«з+а,эЬ3, С13 , которое поступает на третий информационный выход 53.3.1 вычислительного модуля 1.3.1. На выходе умножителя 49.2.2 получаем произведение , которо поступает на второй вход сумматора- вычитателя 51.2.2, на первый вход которого через регистр 47.2.2 поступает произведение а21Ьяз.На выходе сумматора-вычитателя 51.2,2 получаем а,Ь13+а22Ь23, которое поступает на третий информационный выход 53.2.2 вычислительного модуля 1,2.2. На вы

5

изведение , которое поступает на второй вхпд сумматора-вычитателя

на третий информационный выход 31.1.3 вычислительного модуля 1.1,3. На выходе умножителя 77.2.3 получаем произведение , которое поступает на первый вход суммагора-вычитателя .3, на второй вход которого через

0 регистр 75.2.3 поступает произведение a fbtfc а выходе сумматора-вычитателя 7Ч.2.3 получаем выражение +а которое поступает на третий информационный выход 85,2.3

5 вычислительного модуля 1.3.2. На выходе умножителя 77.3.3 получаем произведение , которое поступает на первый вход сумматора-вычитателя

Ь +аъгЪы На выходе сумматора- вычитателя 79,3.3 получаем igib + +a3zb f +а м Ь3, С-Э1 , которое поступает на третий информационный выход 85.3.3 вычислительного модуля 1.3.3. В девятом такте на выходе умножителя 49.3.2 получаем произведение , которое поступает на второй вход сумматора-вычитателя 51.3.2, 0 на первый вход которого через регистр 47.3.2 поступает выражение аг 1$ На выходе сумматора- вычитателя 51.3.2 получаем аг1Ь13 + +a42b23+а2 Ь33 23 которое поступает

5

5 на третий информационный выход 53.3.2

вычислительного модуля 1.3.2. На выходе умножителя 77.2.3 получаем произведение а Ь23 , которое поступает на первый вход сумматора-вычитателя

третий информационный выход 85.2.3 вычислительного модуля 1.2,3. На выходе умножителя 77.3.3 получаем произведение а5,Ьэ2, которое поступает на первый вход сумматора-вычитателя

32Ь23 +

В десятом такте на выходе умножителя 77.3.3 получаем произведение ,э , которое поступает на первый вход сумматора-вычитателя 79.3.3, на второй вход которого через регист 75.3.3 поступает выражение а,, Ъ13 + +азгЬ2з. На выходе сумматора-вычита- теля 79.3.3 получаем а„Ь +а55Ь33 Сзз которое поступает на третий информационный выход 85.3,3 вычислительного модуля 1.3.3.

Дальнейшая работа устройства в данном режиме аналогична указанной. Начиная с четвертого такта, на входы 18.1.J начинает подаваться следующая матрица T)Јd;j3 аналогично действиям матрицы A--Јa-- J, При наращивании размерности предлагаемое устройство не требует увеличения количества связей с блоком управления.

Формула изобретения

45

ного модуля (К, N-1) подключен к третьему информационному входу (1, К+1)-го вычислительного модуля, второй выход блока управления подключен к управляющему входу коммутатора, третий, четвертый, пятый и шестой выходы блока управления подключены соответственно к управляющим входам (2,1)-го, (1,1)-го, (2,N)-ro вычислительных модулей и к первому - четвертому разрядам входа управления

50

(1

-го вычислительного модуля, пя55

тый, иестой и седьмой разряды которого соединены с управляющим выходом (i,)-ro вычислительного модуля, управляющие выходы (m,i)-ro, (2, 1)-го и (1,п)-го рычислительных модулей (,N-i, ,N-2) подключены к управляющим входам соответственно (л+1,i)-ro, (2„1+1)-го и (1, п+1)-го вычислительных модулей.

0

входам вгех регистров и к синхровхо- дам всех вычислительных модулей, о т личающееся тем, что, с целью расширения функциональных возможностей за счет выполнения операций умножения матриц, вычисления определителя и элементов присоединенной матрицы, Б устройство введен коммутатор, первый информационный вход которого подключен к потенциалу логической единицы, второй информационный вход (l,i)-ro вычислительного модуля является (N+i)-M информационным вхос дом устройства, второй информационный вход и выход коммутатора подключены соответственно к первому и третьему информационным входам (1,1)-го вычислительного модуля, третьи инфор0 мационные входы (j,1)-х вычислительных модулей объединены с их первыми информационными входами,, третий информационный выход (N,i)-ro вычисли- тепьного модуля является (i+2N-l)-M

5 выходом устройства, (i+3N-l)-M выходом которого является четвертый ин- форм ационный выход (i,X)-ro вычислительного модуля, четвертый информационный выход (N,l)-ro выяислительQ но го модуля подключен к информационному входу 1-го регистра и третьему информационному входу (N,l+l)-ro вычислительного модуля, третий информационный выход (l,i)-ro вычислительного модуля подключен к четвертому инфор

ного модуля (К, N-1) подключен к третьему информационному входу (1, К+1)-го вычислительного модуля, второй выход блока управления подключен к управляющему входу коммутатора, третий, четвертый, пятый и шестой выходы блока управления подключены соответственно к управляющим входам (2,1)-го, (1,1)-го, (2,N)-ro вычислительных модулей и к первому - четвертому разрядам входа управления

(1

-го вычислительного модуля, пя

тый, иестой и седьмой разряды которого соединены с управляющим выходом (i,)-ro вычислительного модуля, управляющие выходы (m,i)-ro, (2, 1)-го и (1,п)-го рычислительных модулей (,N-i, ,N-2) подключены к управляющим входам соответственно (л+1,i)-ro, (2„1+1)-го и (1, п+1)-го вычислительных модулей.

0

5

0

5

50

5

синхровход третьего регистра подключен к третьему разряду выхода регистра управления, четвертый разряд которого подключен к управляющим входам второго и четвертого коммутаторов, пятый разряд выхода регистра управления подключен к первому управляющему входу первого коммутатора, .второй управляющий вход которого подключен к четвертому разряду выхода регистра управления, шестой и седьмой разрйды которого подключены соответственно к первому и второму входам управления третьего коммутатора.

модуля, четырехразрядные вход и выход регистра управления являются соответственно управляющими входом и выходом вычислительного модуля, выход первого разряда регистра управления подключен к синхровходу первого регистра, выход второго разряда регистра управления подключен к синхровходам второго, четвертого, пятого и шестого регистров, выход третьего разряда регистра управления подключен к синхровходу третьего регистра, выход четвертого разряда регистра управления подключен к управляющим входам сум- матора-вычитателя, первого, второго и третьего коммутаторов.

4, Устройство по п. 1, отличающееся тем, что (i,N)-H вы- числительный модуль (,N) содержит шесть регистров, четыре коммутатора, два умножителя, сумматор-вычитатель и регистр управления, причем первый информационный вход вычислительного модуля подключен к информационным входам первого и второго регистров, выходы которых соответственно подключены к первым информационным входам первого и второго коммутаторов, вто- рой информационный вход вычислительного модуля подключен к объединенным информационным входам третьего и четвертого регистров, выход третьего-регистра подключен к первому входу первого умнржителя, выход которого подключен к первому входу сумматора- вычитателя, выход которого подключен к первому информационному входу четвертого коммутатора, к первому входу второго умножителя и к второму информационному входу третьего коммутатора, выход второго умножителя подключен к второму информационному входу четвертого коммутатора, выход кото- рого подключен к первому информацион

0

5

Q 5 о о 5

5

ному выходу вычислительного модуля, второй информационный выход которого подключен к выходу четвертого регистра, выход третьего коммутатора является третьим информационным выходом вычислительного модуля, третий информационный вход которого подключен к информационному входу пятого регистра, выход которого подключен к второму информационному входу первого коммутатора и четвертому информационному выходу вычислительного модуля, четвертый информационный вход которого подключен к информационному входу шестого регистра, выход которого подключен к второму входу второго умножителя, второму информационному входу второго коммутатора и к первому информационному входу третьего коммутатора, выход первого коммутатора подключен ко E opoMv входу первого умножителя, выход второго коммутатора подключен к втором входу сумма- , тора-вычитателя, синхровход регистра управления является синхровходом вычислительного модуля, пятиразрядные .гзход и выход регистра vnnaBneKHfl являются соответственно управляющими входом и выходом вычислительного модуля, выход первого разряда регистра управления подключен к синхровходам второго, четвертого и пятого регистров, выход второго разряда регистра управления подключен к синхрозходам первого и шестого регистров, выход третьего разряда регистра управления подключен к синхровхоцу третьего регистра, выход четвертого разряда регистра управления подключен к управляющему входу четвертого коммутатора, выход пятого разряда регистра управления подключен к управляющим входам первого, второго и третьего коммутаторов и сумматора-вычитате- ля.

Г7

|I

2U.J

V I

ГУЛ I1

й/г.2

w

1575205

fifV 4Uj

Фиг.З

Sbi.NVV

1

m.a

Фаг.4

.iV

I

Фиг 5

Составитель К. Кухаренко Редактор С, Лисина Техред М.Хрданич Корректор А.Обручар

Закаэ 1786

Тираж 571

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб,, д. 4/5

8 9 fO t 12 13 /4

t эLгu J J J J J J J J J JTЛJтл

яз.nn

WU LrinJ J-LriTLrUlJ-U-U rL

т1

0 t 2 3 5 6 1 В 9 10 11 12 IS tk

i - i i t i

1

in121

m jrLrurLnj j j j nj ru TLru-(

7

no. LГLЛJTЛJ J J1J J J J J J J J

то

т.

Фиг б

г

Подписное

| Устройство для LU-разложения матриц | 1986 |

|

SU1401478A1 |

| Устройство для операций над матрицами | 1987 |

|

SU1443003A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1990-06-30—Публикация

1988-08-18—Подача