1

Устройство относится к вычисли- тельной технике и предназначено для построения систем цифровой обработки сигналов, основанных на выполнении алгоритма быстрого преобразования Фурье.

Целью изобретения является расширение его функциональных возможностей за счет вычисления усреднения, модуля и фазы комплексных чисел, а также повышение точности за счет нормализации исходных операндов

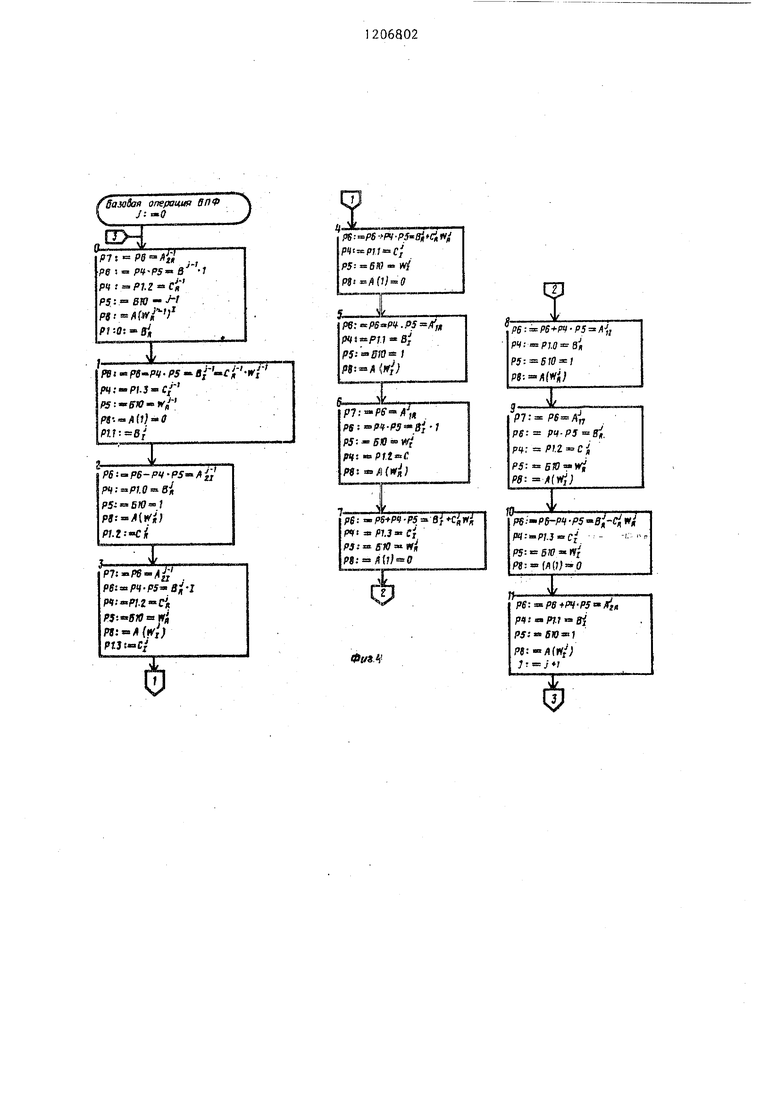

В устройстве производится вычисление базовой операции быстрого преобразования Фурье (БПФ1 по формулам

BR + CKW - CtWi

BI + C«,Wt + CiWR

Aj BR + - CrWi

20

A: A 12068Q22

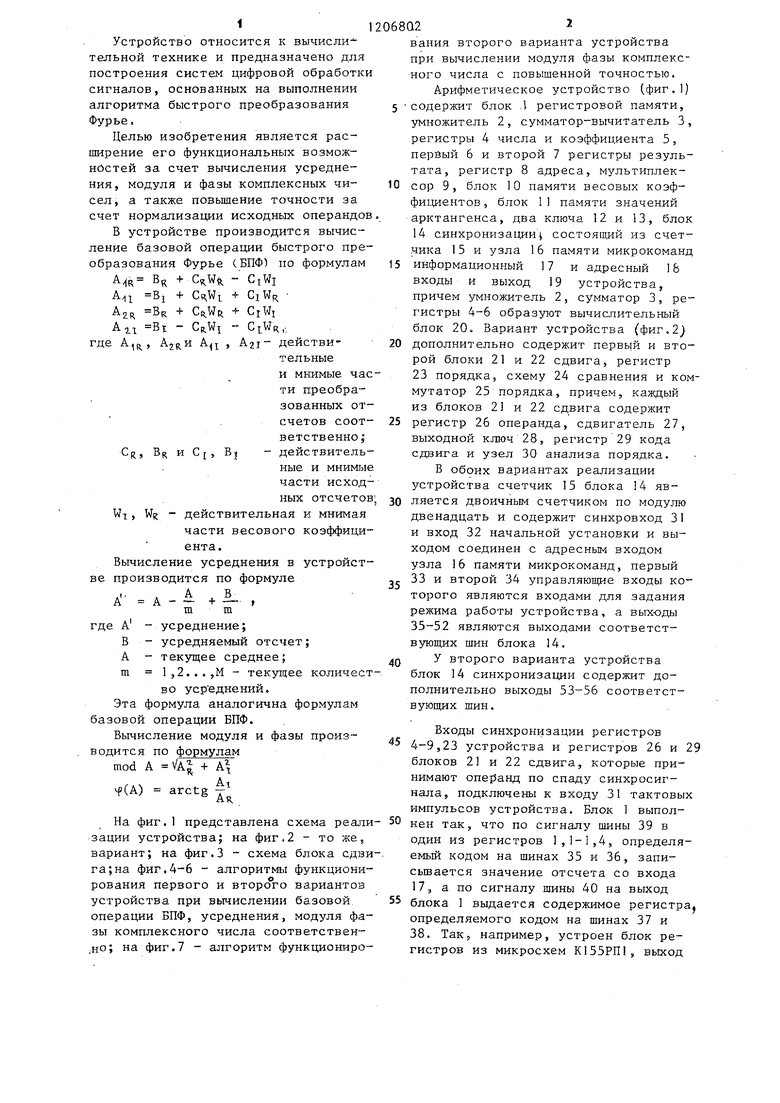

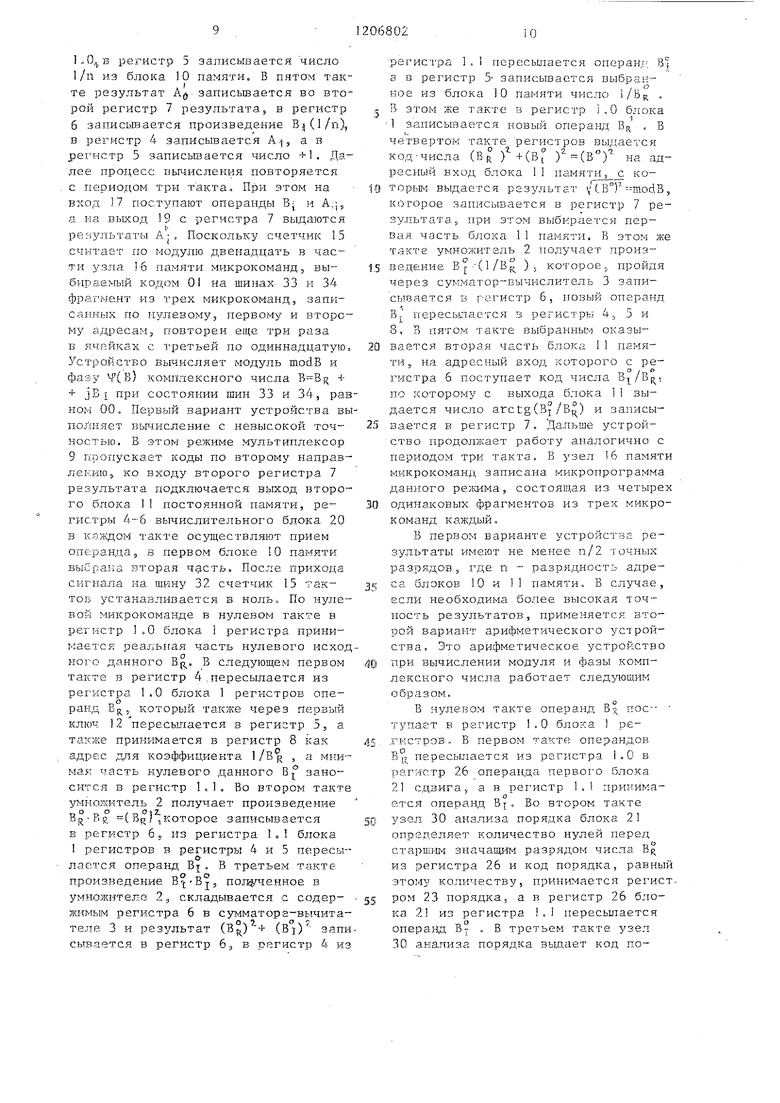

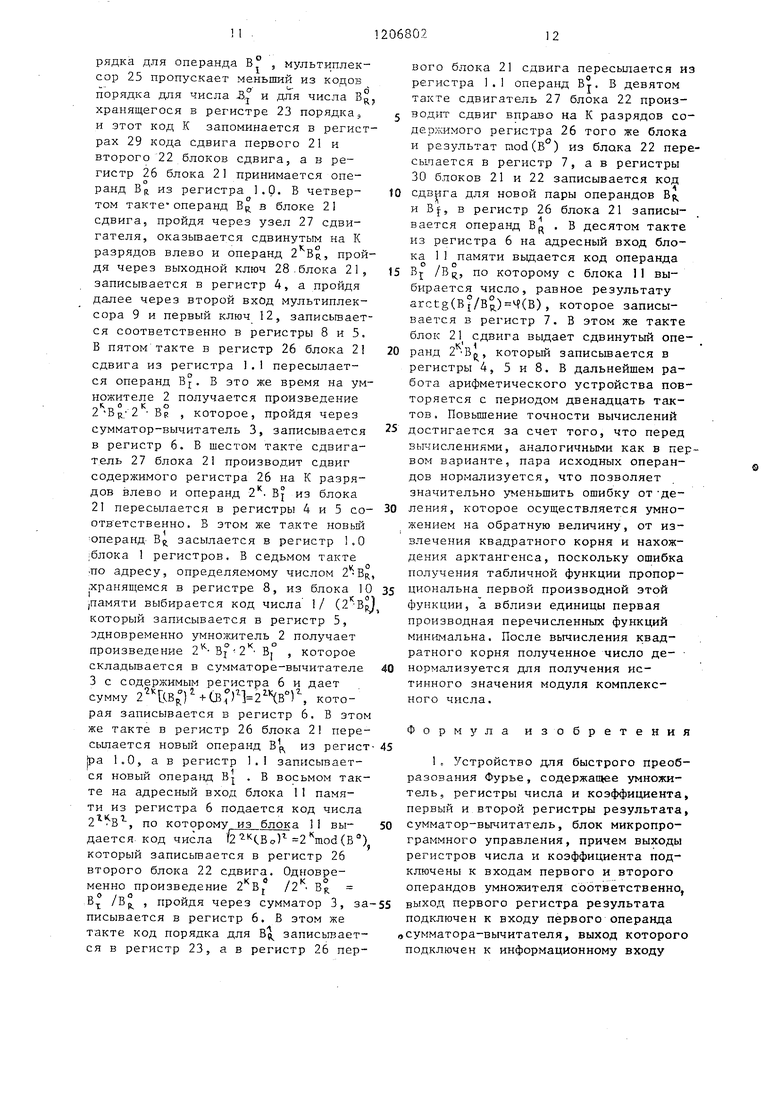

вания второго варианта устройства при вычислении модуля фазы комплексного числа с повышенной точностью. Арифметическое устройство (фиг.1)

5 содержит блок .1 регистровой памяти, умножитель 2, сумматор-вычитатель 3, регистры 4 числа и коэффициента 5, первый 6 и второй 7 регистры результата, регистр 8 адреса, мультиплек10 сор 9, блок 10 памяти весовых коэффициентов 5 блок I1 памяти значений арктангенса, два ключа 12 и 13, блок 14 синхронизации I состоящий из счетчика 15 и узла 16 памяти микрокоманд

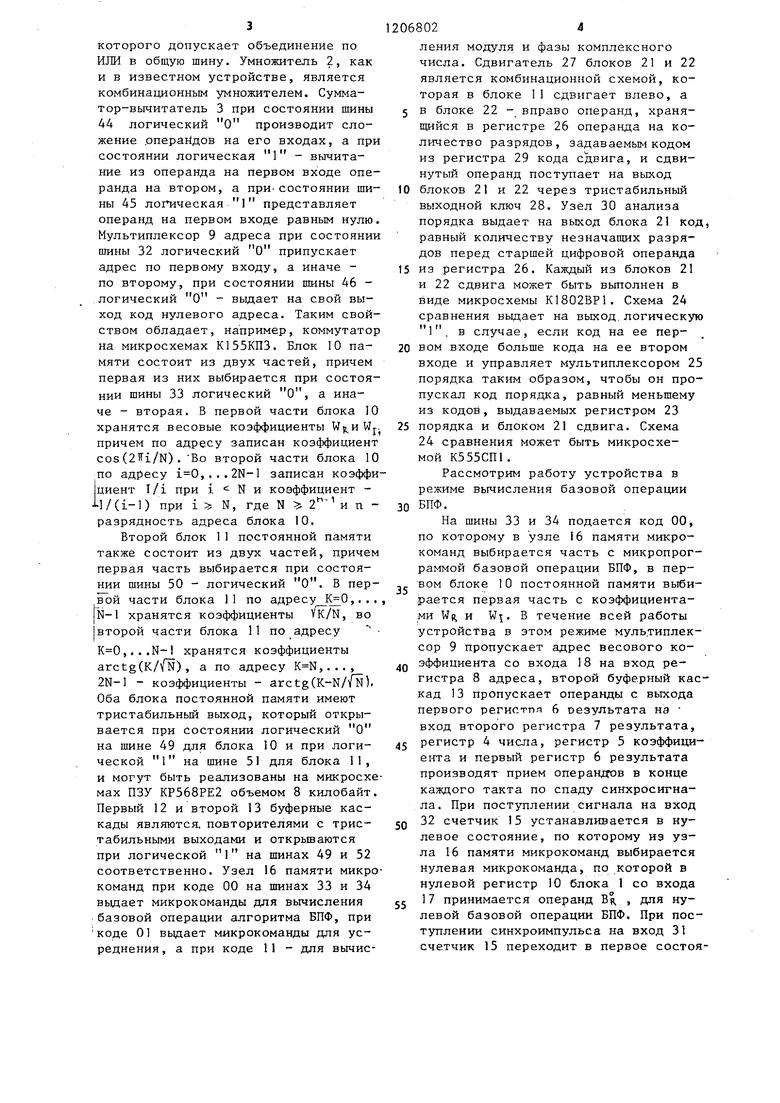

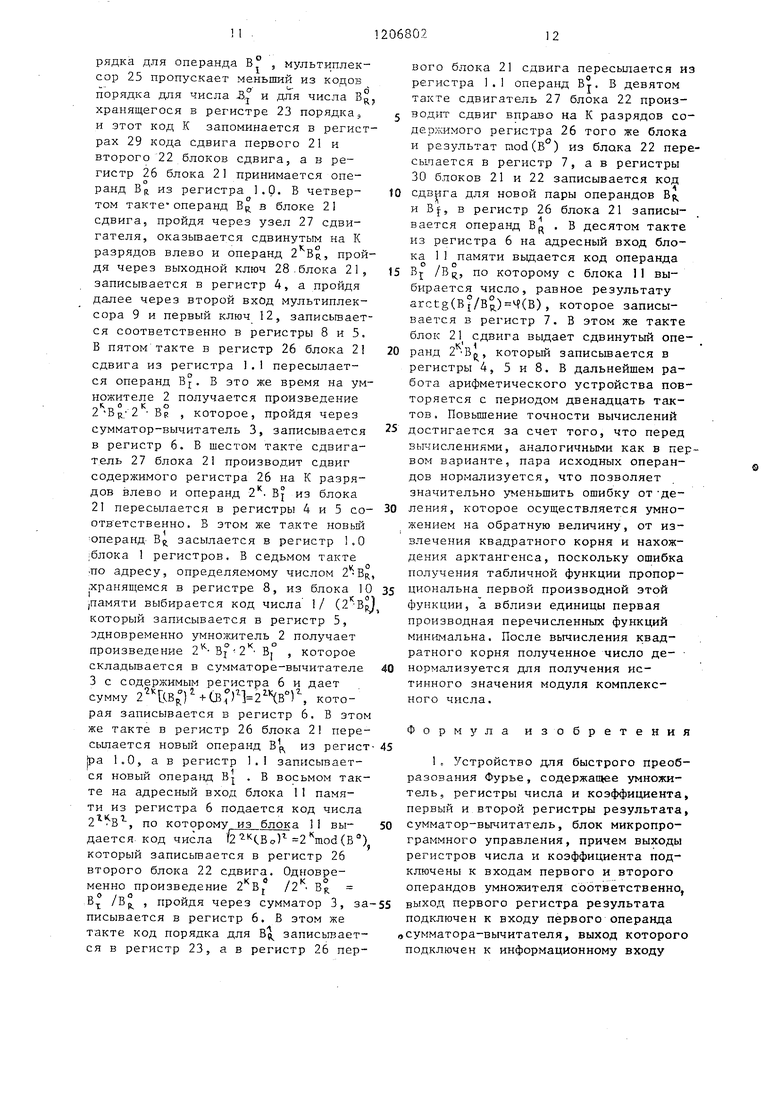

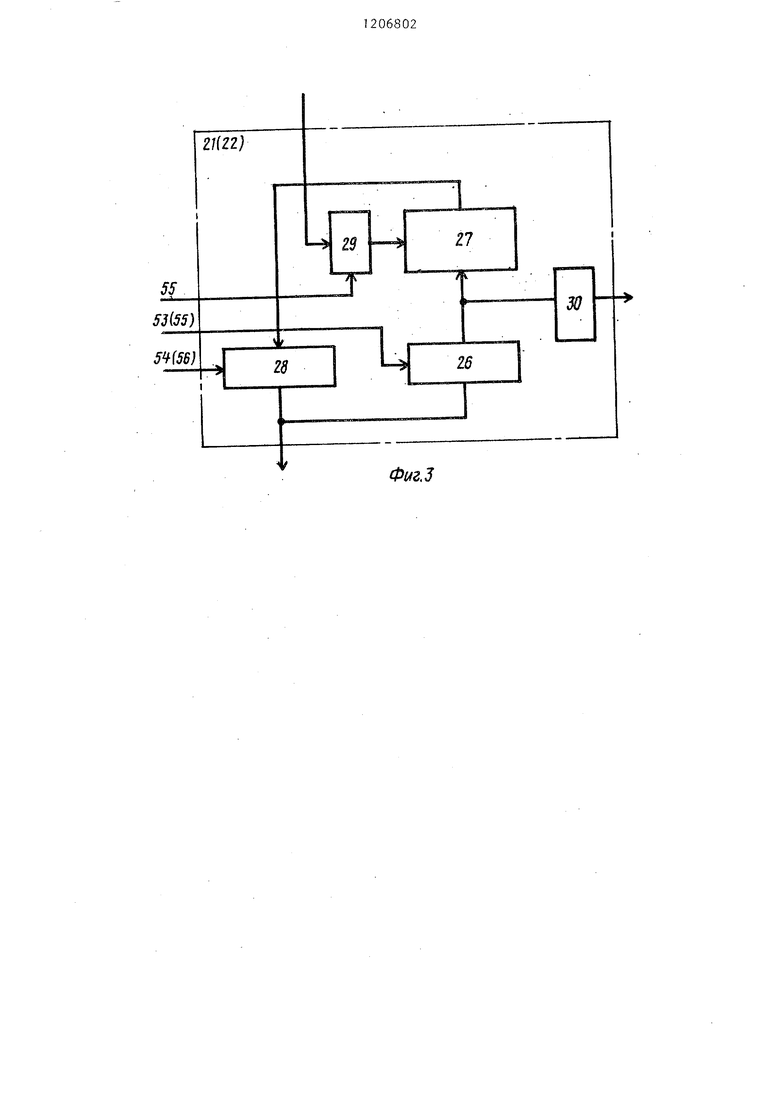

15 информационный 17 и адресный 18 входы и выход 19 устройства, причем умножитель 2, сумматор 3, регистры 4-6 образуют вычислительный блок 20, Вариант устройства (фиг.2} дополнительно содержит первый и второй блоки 21 и 22 сдвига, регистр 23 порядка, схему 24 сравнения и ком мутатор 25 порядка, причем, каждый из блоков 21 и 22 сдвига содержит

25 регистр 26 операнда, сдвигатель 27, выходной ключ 28, регистр 29 кода сдвига и узел 30 анализа порядка.

В обоих вариантах реализации устройства счетчик 15 блока 14 яв30 ляется двоичным счетчиком по модулю двенадцать и содержит синхровход 31 и вход 32 начальной установки и выходом соединен с адресным входом узла 16 памяти микрокоманд, первый

,г 33 и второй 34 управляющие входы которого являются входами для задания режима работы устройства, а выходы 35-52 являются выходами соответствующих шин блока 14.

У второго варианта устройства блок 14 синхронизации содержит дополнительно выходы 53-56 соответст- вуюших шин.

Bi - CP,WI - CtWR,, где , А , Aaj- действительныеи мнимые части преобразованных отсчетов соответственно

CR, BR и Cj, В} - действительные и мнимые части исходных отсчетов;

Wi, WR - действительная и мнимая части весового коэффициента.

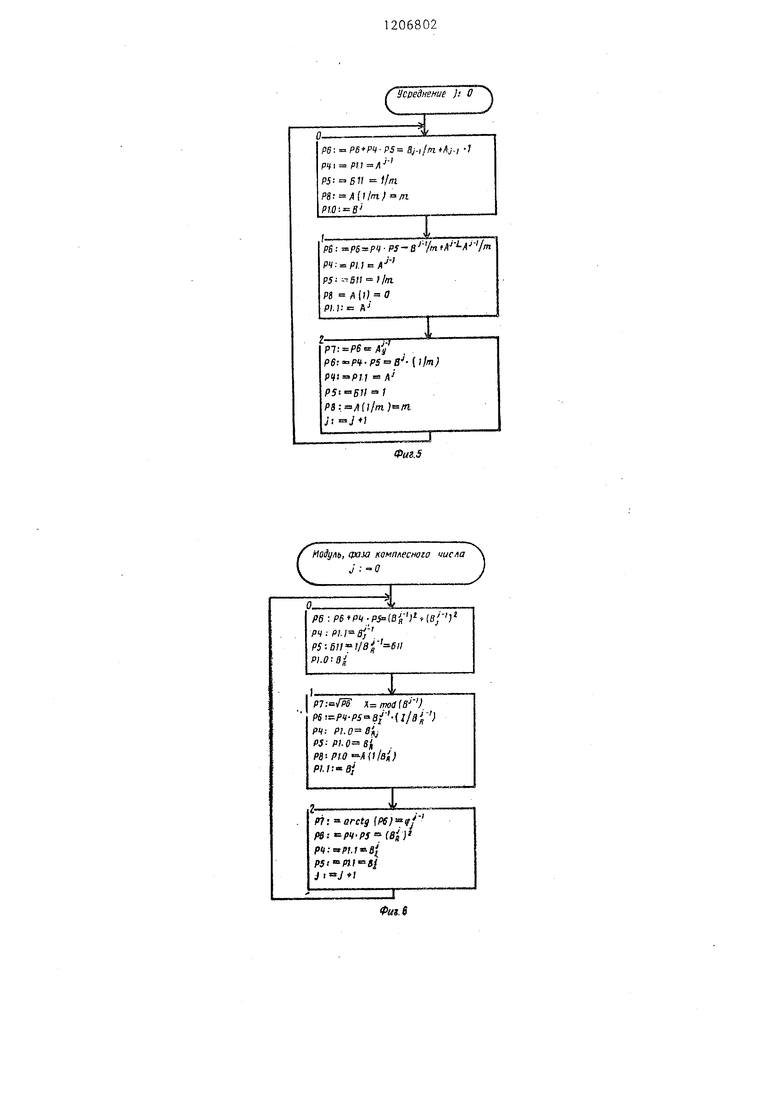

Вычисление усреднения в устройстве производится по формуле

4. S

+

m m где А - усреднение;

В - усредняемый отсчет; А - текущее среднее; m 1,2,..,М - текущее количество уср еднений.

Эта формула аналогична формулам базовой операции БПФ.

Вычисление модуля и фазы производится по формулам mod А VA + А

AI f(А) arctg д

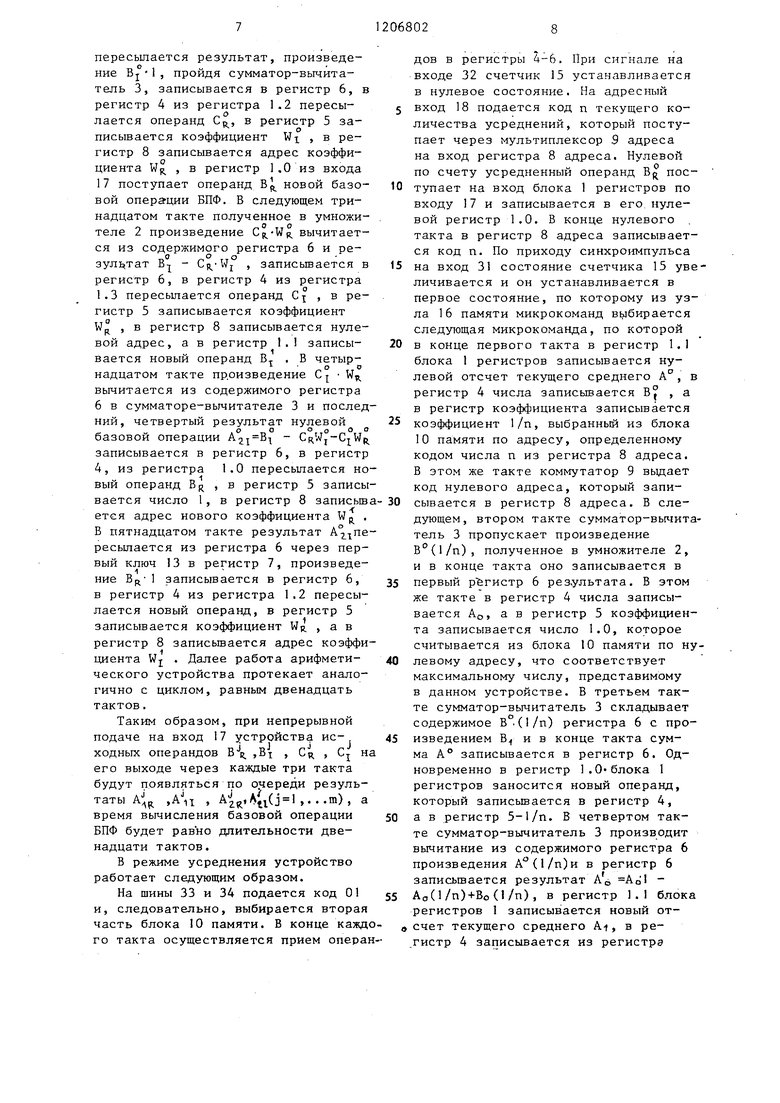

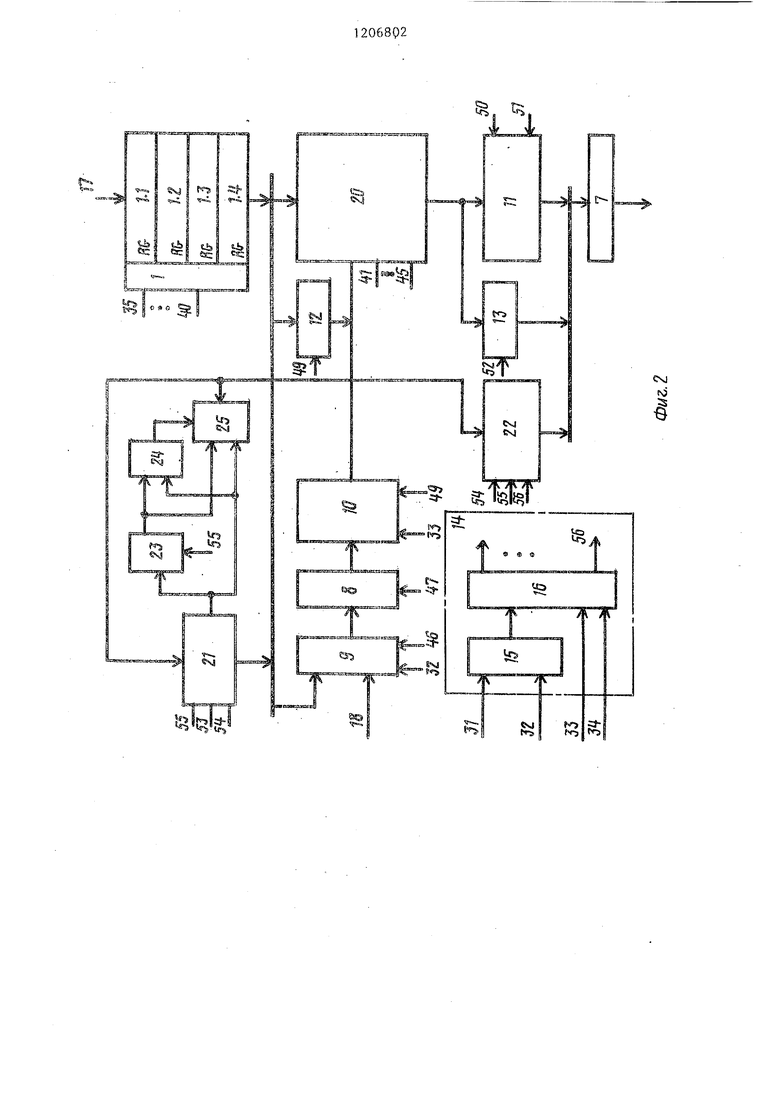

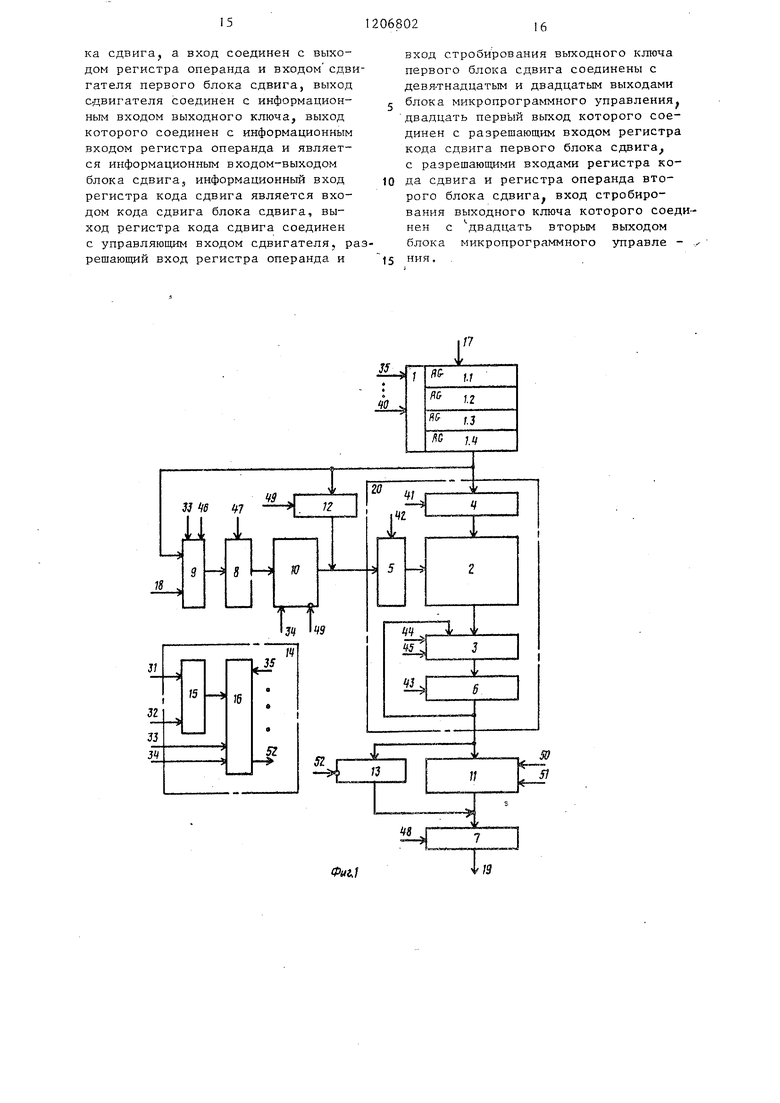

импульсов устройства. Блок 1 выполНа фиг.1 представлена схема реали- 50 нен так, что по сигналу шины 39 в зации устройства; на фиг,2 - то же, один из регистров 1,1-1,4, определя- вариант; на фиг.З - схема блока сдви-. емьш кодом на шинах 35 и 36, запи- га;на фиг.4-6 - алгоритм1,1 функционирования первого и второго вариантов устройства при вычислении базовой операции БПФ, усреднения, модуля фазы комплексного числа соответствен40

Входы синхронизации регистров 4-9,23 устройства и регистров 26 и 2 блоков 21 и 22 сдвига, которые принимают опе13анд по спаду синхросигнала, подключены к входу 31 тактовых

сывается значение отсчета со входа 17, а по сигналу шины 40 на выход 55 блока 1 выдается содержимое регистра определяемого кодом на шинах 37 и 38., Так, например, устроен блок ресывается значение отсчета со входа 17, а по сигналу шины 40 на выход 55 блока 1 выдается содержимое регистра определяемого кодом на шинах 37 и 38., Так, например, устроен блок ре.но; на фиг.7 - алгоритм функциониро- гистров из микросхем К155РП1, выход

20

2068Q22

вания второго варианта устройства при вычислении модуля фазы комплексного числа с повышенной точностью. Арифметическое устройство (фиг.1)

5 содержит блок .1 регистровой памяти, умножитель 2, сумматор-вычитатель 3, регистры 4 числа и коэффициента 5, первый 6 и второй 7 регистры результата, регистр 8 адреса, мультиплек10 сор 9, блок 10 памяти весовых коэффициентов 5 блок I1 памяти значений арктангенса, два ключа 12 и 13, блок 14 синхронизации I состоящий из счетчика 15 и узла 16 памяти микрокоманд

15 информационный 17 и адресный 18 входы и выход 19 устройства, причем умножитель 2, сумматор 3, регистры 4-6 образуют вычислительный блок 20, Вариант устройства (фиг.2} дополнительно содержит первый и второй блоки 21 и 22 сдвига, регистр 23 порядка, схему 24 сравнения и коммутатор 25 порядка, причем, каждый из блоков 21 и 22 сдвига содержит

25 регистр 26 операнда, сдвигатель 27, выходной ключ 28, регистр 29 кода сдвига и узел 30 анализа порядка.

В обоих вариантах реализации устройства счетчик 15 блока 14 яв30 ляется двоичным счетчиком по модулю двенадцать и содержит синхровход 31 и вход 32 начальной установки и выходом соединен с адресным входом узла 16 памяти микрокоманд, первый

,г 33 и второй 34 управляющие входы которого являются входами для задания режима работы устройства, а выходы 35-52 являются выходами соответствующих шин блока 14.

У второго варианта устройства блок 14 синхронизации содержит дополнительно выходы 53-56 соответст- вуюших шин.

;

40

Входы синхронизации регистров 4-9,23 устройства и регистров 26 и 29 блоков 21 и 22 сдвига, которые принимают опе13анд по спаду синхросигнала, подключены к входу 31 тактовых

50 нен так, что по сигналу шины 39 в один из регистров 1,1-1,4, определя- емьш кодом на шинах 35 и 36, запи-

сывается значение отсчета со входа 17, а по сигналу шины 40 на выход 55 блока 1 выдается содержимое регистра определяемого кодом на шинах 37 и 38., Так, например, устроен блок ре гистров из микросхем К155РП1, выход

которого допускает объединение по ИЛИ в общую шину. Умножитель 2, как и в известном устройстве, является комбинационным умножителем. Сумма- тор-вычитатель 3 при состоянии шины 44 логический О производит сложение .операь дов на его входах, а при состоянии логическая 1 - вычитание из операнда на первом входе операнда на втором, а при-состоянии шины 45 логическая 1 представляет операнд на первом входе равным нулю. Мультиплексор 9 адреса при состоянии шины 32 логический О припускает адрес по первому входу, а иначе по второму, при состоянии ЕМНЫ 46 логический О - вьщает на свой выход код нулевого адреса. Таким свойством обладает, например, коммутатор на микросхемах К155КПЗ. Блок 10 памяти состоит из двух частей, причем первая из них выбирается при состоянии шины 33 логический О, а иначе - вторая. В первой части блока 10 хранятся весовые коэффициенты УциИр причем по адресу записан коэффициент cos (2T i/N) . Во второй части блока 10 по адресу ,...2N-1 записан коэффициент I/i при i N и коэффициент - (i-l) при i : N, где N : и п - разрядность адреса блока 10.

Второй блок 11 постоянной памяти также состоит из двух частей, причем первая часть выбирается при состоянии шины 50 - логический О. В первой части блока 11 по адресу ,... N-1 хранятся коэффициенты VK/N, во второй части блока 11 по адресу ,...N-1 хранятся коэффициенты arctg(K/fN), а по адресу ,..., 2N-1 - коэффициенты - arctg(K-N/yN)i Оба блока постоянной памяти имеют тристабильный выход, который открывается при состоянии логический О на шине 49 для блока 10 и при логической 1 на шине 51 для блока 11, и могут быть реализованы на микросхемах ПЗУ КР568РЕ2 объемом 8 килобайт. Первый 12 и второй 13 буферные каскады являются, повторителями с трис- табильными выходами и открьтаются при логической 1 на шинах 49 и 52 соответственно. Узел 16 памяти микрокоманд при коде 00 на шинах 33 и 34 выдает микрокоманды для вычисления базовой операции алгоритма БПФ, при коде 01 выдает микрокоманды для усреднения, а при коде 11 - для вычис

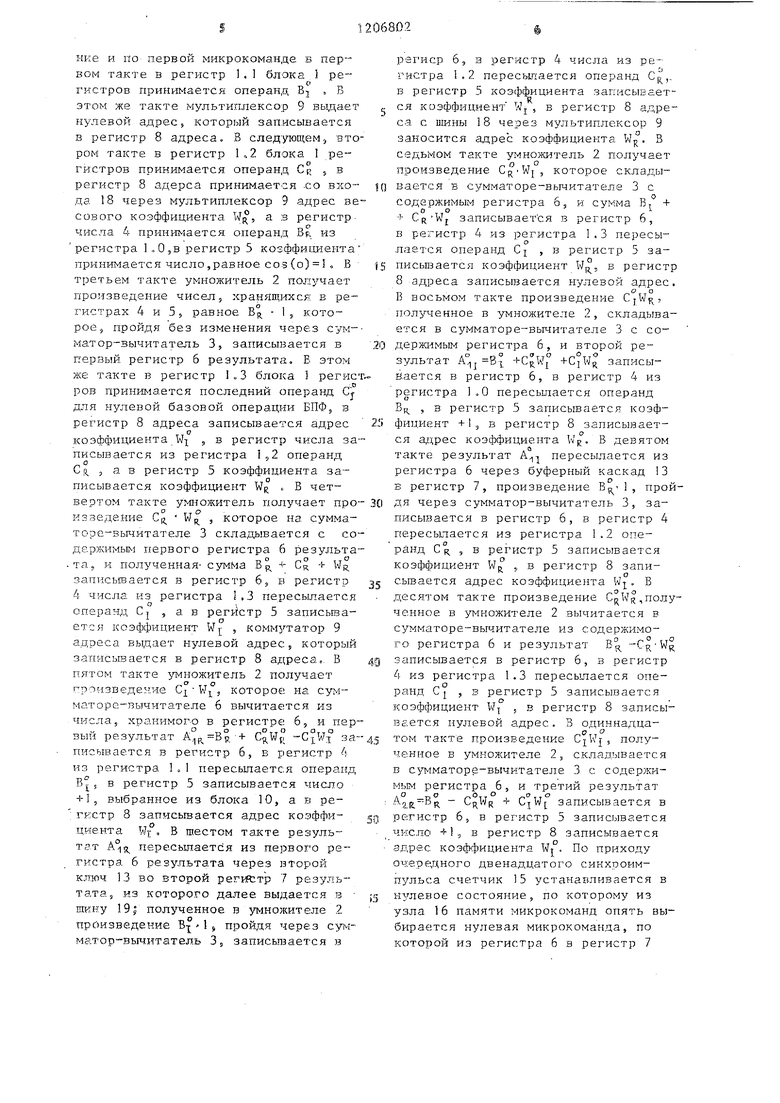

2068024

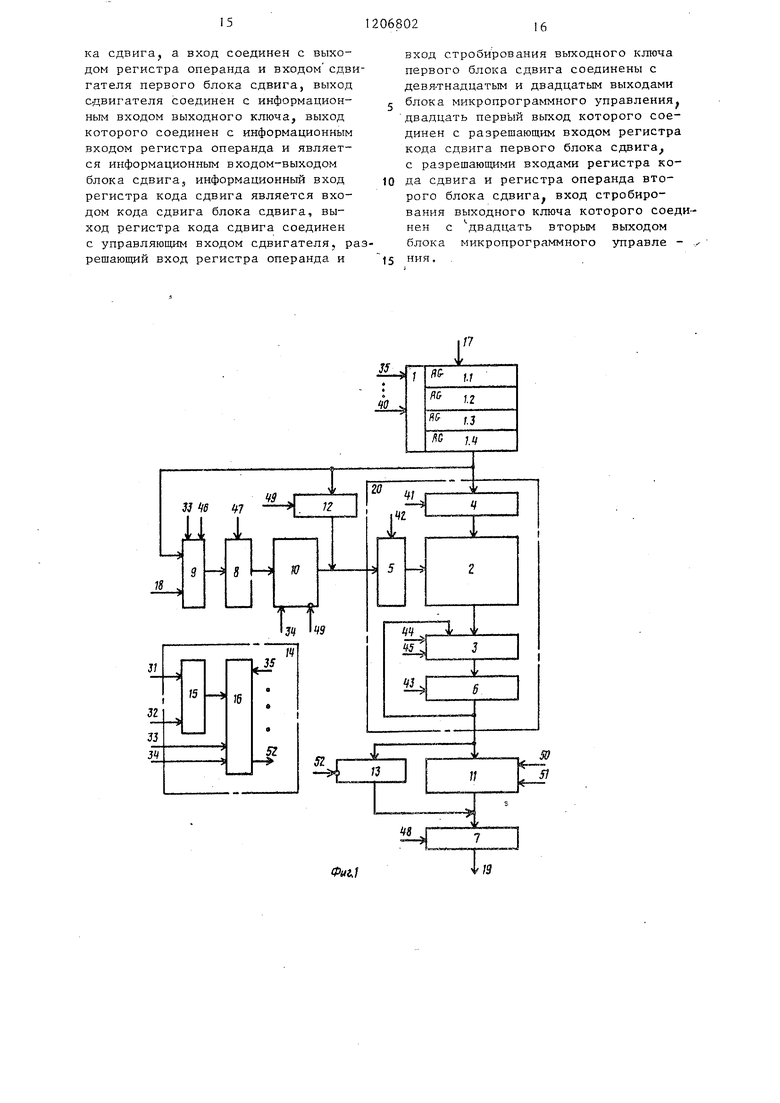

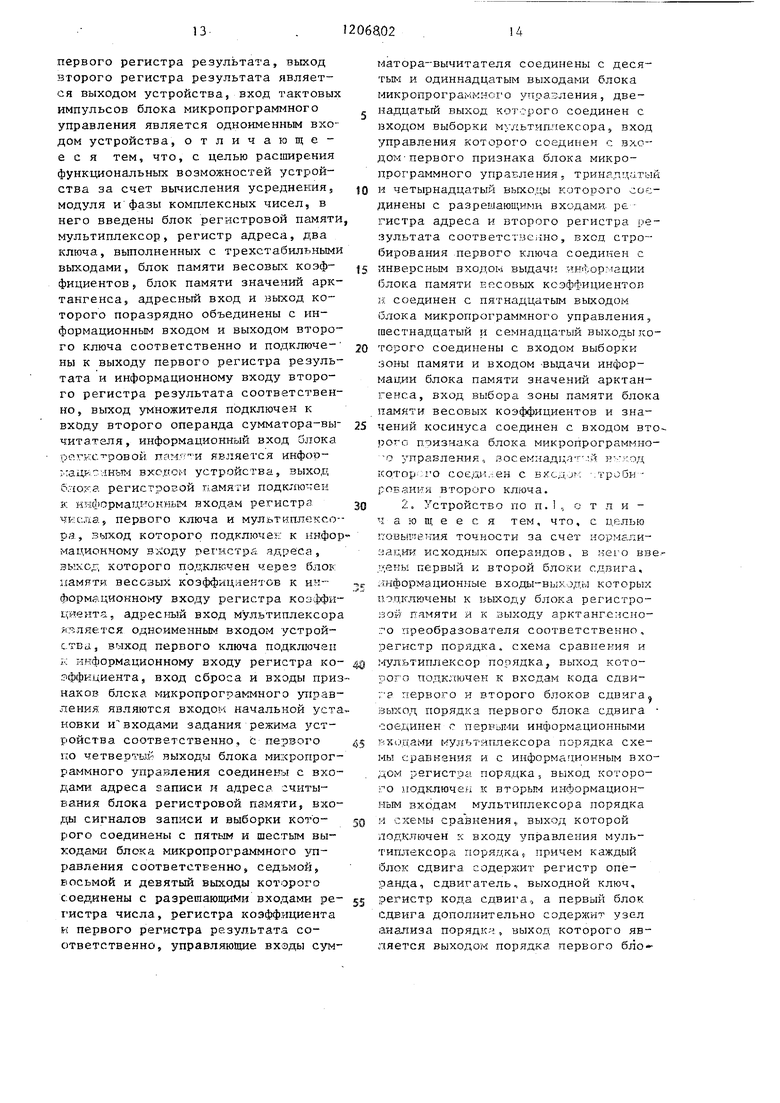

ления модуля и фазы комплексного числа. Сдвигатель 27 блоков 21 и 22 является комбинационной схемой, которая в блоке 11 сдвигает влево, а 5 в блоке 22 - вправо операнд, хранящийся в регистре 26 операнда на количество разрядов, задаваемым кодом из регистра 29 кода сдвига, и сдвинутый операнд поступает на выход

10 блоков 21 и 22 через тристабильный выходной ключ 28. Узел 30 анализа порядка выдает на выход блока 21 код, равный количеству незначаш 1х разрядов перед старшей цифровой операнда

15 из регистра 26. Каждый из блоков 21 и 22 сдвига может быть выполнен в виде микросхемы К1802ВР1. Схема 24 сравнения выдает на выход, логическую 1, в случае, если код на ее пер20 ном входе больше кода на ее втором входе и управляет мультиплексором 25 порядка таким образом, чтобы он пропускал код порядка, равный меньшему из кодов, выдаваемых регистром 23

25 порядка и блоком 21 сдвига. Схема 24 сравнения может быть микросхемой К555СП1.

Рассмотрим работу устройства в режиме вычисления базовой операции

30 БПФ.

На шины 33 и 34 подается код 00, по которому в узле 16 памяти микрокоманд выбирается часть с микропрограммой базовой операции БПФ, в первом блоке 10 постоянной памяти выбирается первая часть с коэффициентами W( и W. В течение всей работы устройства в этом режиме мультиплексор 9 пропускает адрес весового коэффициента со входа 18 на вход регистра 8 адреса, второй буферный каскад 13 пропускает операнды с выхода первого регистпя 6 результата на вход второго регистра 7 результата,

регистр 4 числа, регистр 5 коэффициента и первый регистр 6 результата производят прием операндов в конце каждого такта по спаду синхросигнала. При поступлении сигнала на вход

32 счетчик 15 устанавливается в нулевое состояние, по которому из узла 16 памяти микрокоманд выбирается нулевая микрокоманда, по которой в нулевой регистр 10 блока 1 со входа

17 принимается операнд BR, , для нулевой базовой операции БПФ, При поступлении синхроимпульса на вход 31 счетчик 15 переходит в первое состоянке и по первой микрокоманде в ггер- вом такте в регистр 1.1 блока 1 регистров принимается операнд Bj , В этом -же такте мультиплексор 9 выдает нулеворт адрес, который записывается в регистр 8 адреса. В след утощем, втором такте в регистр 1,2 блока 1 регистров принимается операнд С(; „в регистр 8 адерса принимается -со вхо- да 18 через мультиплексор 9 адрес весового коэффициента Wj, а в регистр числа 4 принш- ается операнд BR из регистра 1,, ОэВ регистр 5 козффигдаепта принимается число,равное cos (о) , В третьем такте умножитель 2 получает произведение чисел, хранящтгпсся в регистрах 4 и 5 5 равное Вд - 1 ., которое, пройдя без изменения через сумматор-вычитатель 3, записывается в первый регистр 6 результата. В этом же такте в регистр КЗ блока 1 регис ров принимается последний операнд Cj для нулевой базовой операции БПФ, в регистр 8 адреса записывается адрес

о

коэффициента Wj , в регистр числа записывается из регистра 1,,2 операнд

О

СIJ, 3 а в регистр 5 коэффициента записывается коэффициент Wg . Б четвертом такте умножитель получает про иэзедение С, Wp , которое на сумма- торе-Бычитателе 3 складывается с содержимым первого регистра 6 результа . та, и полученная- сумма В р CR + V/R записьгоается в регистр 6, в регистр 4 числа из регистра 1.3 пересылается операнд Cj , а в регистр 5 записьиа- ется коэф(.1)идиент Wj , коммутатор 9 адреса выдает нулевой адрес, который записывается в регистр 8 адреса,, В пятом такте умножитель 2 получает пpoизвeдe.гяe , которое на cyi-.r- маторе-вычитателе 6 вычитается из числа, хранимого в регистре 6, и первый результат А. + за письшается в регистр 6, в регистр 4 из регистра пересылается операпд В 5 в регистр 5 записывается число +1, выбранное из блока 10, а в ре- гкстр 8 записьшается адрес коэффи- диента Wj, В шестом такте результат , пересыпается из первого регистра 6 результата через второй ключ 13 во второй рег1«:тр 7 результата, из которого далее выдается в пшну 19| полученное в умножителе 2 прйизведение j пройдя через cyi4- матор-вычитатель 3, записывается в

региср 6, в регистр 4 числа из регистра 1.2 пересьшается операнд С,.

в регистр 5 коэффициента записывает-

ся коэффициент Wj , в регистр 8 адреса с шины 18 через мультиплексор 9 заносится адрес коэффициента W. В седьмом такте умножитель 2 получает произведение C., которое складывается в сумматоре-вычитателе 3 с

содержимым регистра 6. и сумма В, +

о о

+ CR-WJ записывается в регистр 6,

в регистр 4 из регистра 1.3 пересылается операнд Cj , в регистр 5 за- письБзается коэффициент W. в регистр 8 адреса записывается нулевой адрес

о о

в восьмом такте произведение CjWi, пол -1енное в умножителе 2, складывается в сумматоре-вычитателе 3 с содержимым регистра б, и второй результат В +CRW° +CiW записывается в регистр 6, в регистр 4 из регистра 1.0 пересьшается операнд Bf( 5 в регистр 5 записывается коэффициент +, в регистр 8 записывается адрес коэффициента Wg. В девятом такте результат А пересылается из

регистра 6 через буферный каскад 13

о

в регистр / , произведение В, 1 , пройдя через сумматор-вычитатель 3, записывается в регистр 6, в регистр 4 пересылается из регистра 1.2 операнд С R 5 в регистр 5 записьшается коэффициент Wt, „ в регистр 8 запио

сьшается адрес коэффициента Wj. В десятом такте произведение Cp,WR,полученное в умножителе 2 вычитается в сумматоре-вычитателе из содержимого регистра 6 и результат В- -Cp/W записывается в регистр 6, з регистр 4 из регистра 1.3 пересьшается операнд Cj 5 в регистр 5 записывается коэффициент Wj , в регистр 8 записыве.ется пулевой адрес. В одиннадцас с

ТОМ такте произведение CjWj, полученное в умножителе 2, складывается в сумматоре-вычитателе 3 с содержимым регистра 6, и третий результат - + CjW записывается в регистр 6, в регистр 5 записывается число ., в регистр 8 записывается адрес коэффициента Wj. По приходу очередного двенадцатого синхроимпульса счетчик 15 устанавливается в нулевое состояние, по которому из узла 16 памяти микрокоманд опять выбирается нулевая микрокоманда, по которой из регистра 6 в регистр 7

пересылается результат, произведение , пройдя сумматор-вычита- тель 3, записывается в регистр 6, в регистр 4 из регистра 1.2 пересылается операнд С, в регистр 5 записывается коэффициент Wt , в регистр 8 записывается адрес коэффициента Wfi , в регистр 1 ,0 из входа 17 поступает операнд Bj новой базовой операции БПФ. В следующем тринадцатом такте полученное в умножителе 2 произведение , вычитается из содержимого регистра 6 и ре0 о о зуль,тат В| - , записьшается в

регистр 6, в регистр 4 из регистра 1.3 пересылается операнд С , в регистр 5 записывается коэффициент Wp , в регистр 8 записывается нулевой адрес, а в регистр 1. записывается новый операнд В , В четырнадцатом такте произведение Сj W вычитается из содержимого регистра 6 в сумматоре-вычитателе 3 и последний, четвертый результат нулевой базовой операции Aj, - записывается в регистр 6, в регистр 4, из регистра 1.0 пересылается новый операнд Вр; , в регистр 5 записывается число 1, в регистр 8 записьшется адрес нового коэффициента W . В пятнадцатом такте результат ресылается из регистра 6 через первый ключ 13 в регистр 7, произведение 1 записывается в регистр 6, в регистр 4 из регистра 1.2 пересылается новый операнд, в регистр 5 записывается коэффициент WR. , а в регистр 8 записьшается адрес коэффициента Wj . Далее работа арифметического устройства протекает аналогично с циклом, равным двенадцать тактов.

Таким образом, при непрерывной подаче на вход 17 устройства исходных операндов В-, ,Bi , С, , С н его выходе через каждые три такта будут появляться по о.череди результаты , , А,A(|(J I ,. . .т) , а время вычисления базовой операции БПФ будет равно длительности двенадцати тактов.

В режиме усреднения устройство работает следующим образом.

На шины 33 и 34 подается код 01 и, следовательно, выбирается вторая часть блока 10 памяти. В конце каждго такта осуществляется прием операндов в регистры 4-6, При сигнале на входе 32 счетчик 15 устанавливается в нулевое состояние. На адресный вход 18 подается код п текущего количества усреднений, который поступает через мультиплексор Э адреса на вход регистра 8 адреса. Нулевой по счету усредненный операнд В пос- тупает на вход блока 1 регистров по входу 17 и записывается в его нулевой регистр 1.0. В конце нулевого такта в регистр 8 адреса записывается код п. По приходу синхроимпульса на вход 31 состояние счетчика 15 увеличивается и он устанавливается в первое состояние, по которому из узла 16 памяти микрокоманд выбирается следующая микрокоманда, по которой

в конце первого такта в регистр 1.1 блока 1 регистров записывается нулевой отсчет текущего среднего А°, в регистр 4 числа записьшается В , а в регистр коэффициента записывается

коэффициент 1/п, выбранный из блока 10 памяти по адресу, определенному кодом числа п из регистра 8 адреса. В этом же такте коммутатор 9 выдает код нулевого адреса, который записывается в регистр 8 адреса. В следующем, втором такте сумматор-вычита- тель 3 пропускает произведение в (1/п), полученное в умножителе 2, и в конце такта оно записывается в

первый р ёгистр 6 результата. В этом же такте в регистр 4 числа записывается АО, а в регистр 5 коэффициента записывается число 1.0, которое считывается из блока 10 памяти по нулевому адресу, что соответствует максимальному числу, представимому в данном устройстве. В третьем такте сумматор-вычитатель 3 складывает содержимое В .(1/п) регистра 6 с произведением В и в конце такта сумма А° записьшается в регистр 6. Одновременно в регистр 1.0-блока 1 регистров заносится новый операнд, который записьшается в регистр 4,

а в регистр 5-1/п. В четвертом такте сумматор-вычитатель 3 производит вычитание из содержимого регистра 6 произведения А(1/п)и в регистр 6 записьшается результат А Ао1 AO(I/п)+Во(1/п), в регистр 1.1 блока

регистров 1 записывается новый от- счет текущего среднего Af, в ре- ,гистр 4 записывается из регистра

l.,0,,B регистр 5 записывается число

1/п из блока 10 памяти, В пятом так. I

те результат А§ записьшается во второй регистр 7 результата, в регистр 6 записывается произведение B,j(l/n), в регистр 4 записывается А., а в регистр 5 записьгоается число -ь1. Далее процесс вычисления повторяется с пешиодом три такта. При этом на вход 17 поступают операнды Bj li A;-,, а на выход 19 с регистра 7 выдаются результаты A J Поскольку счетчик 15 считает по модулю двенадцать в час- ти узла 16 па.мяти микрокоманд, выбираемый кодом 01 на шинах- 33 и 34 фрагмент из трех микрокоманд, записанных по иулевомуз первому и второму адресам повторен еще три раза в ячейках с третьей по одиннадцатую Устройство вычисляет модуль modB и фазу М(В) комплексного числа + + jBi при состоянии шин 33 и 34, равном 00, Первый вариант устройства выполняет вьгаисление с невысокой точностью, В этом режиме мультиплексор 9 пропускает коды по второму направ- лекиЮэ ко входу второго регистра 7 результата подключается выход второго блока 11 постоянной памяти, регистры 4-6 вычислительного блока 20 в каждом такте осуществляют прием операнда, в первом блоке 0 памяти выбрана вторая часть. После прихода сигнала па шршу 32 счетчик 15 тактов устанавливается в ноль. По нулевой микрокоманде в нулевом такте в регистр 1.0 блока 1 регистра принимается реальная часть нулевого исходного данного Вр, В следующем первом такте в регистр 4 , пересылается из регистра 1,0 блока 1 регистров операнд Bg., который также через первый ключ 12 пересылается в регистр 5, а принимается в регистр 8 как адрес для коэффициента 1 /В , а мнимая часть нулевого данного В заносится в регистр I.1 о Во втором такте . мнолситель 2 получает произведение , ( Bf;), которое записывается в регистр 6 S из регистра 1.1 блока

1 регистров в регистры 4 и 5 Пересы

лается операнд Bj, В третьем такте произведение B-j- Bj-, по:: ченное в

умножителе

складывается с содержимым регистра 6 в сумматоре-вычита- теле 3 и результат (В) (в) записывается в регистр 6;, в регистр 4 из

0

5

регистра 1 . 1 пересылается операн,г , В а в регистр 5 записывается выбранное из блока 10 памяти число i/B . В зтом же такте в регистр 1.0 блока 1 записывается новый операн/д BR . В четвертом такте регистров выдается код-числа (BR f+(Bt° )(В°) на адресный вход блока 1 памяти, с которым выдается результат yCB°) -modB, которое записывается в регистр 7 результата j при этом выбирается первая часть блока 11 памяти. В этом же такте умножитель 2 получает произведение Bj- (l/B )j которое.; пройдя через сумматор-вычислитель 3 записывается 3 регистр 6, повый операнд В, пересылается в регистры 4. 5 и 8, Б пятом такте выбранным оказы- 0 Бается вторая часть блока 11 памяти на адресн.ый вход которого с регистра 6 поступает код числа , по которому с выхода блока 11 выдается число arctg(Bj/Вц) и записывается в регистр 7. Дальше устройство продолжает работу аналогично с периодом три такта. В узел 16 памяти микрокоманд записана микропрограмма данного режима, состоящая из четырех одинаковых фрагментов из трех микро- команд каждый,

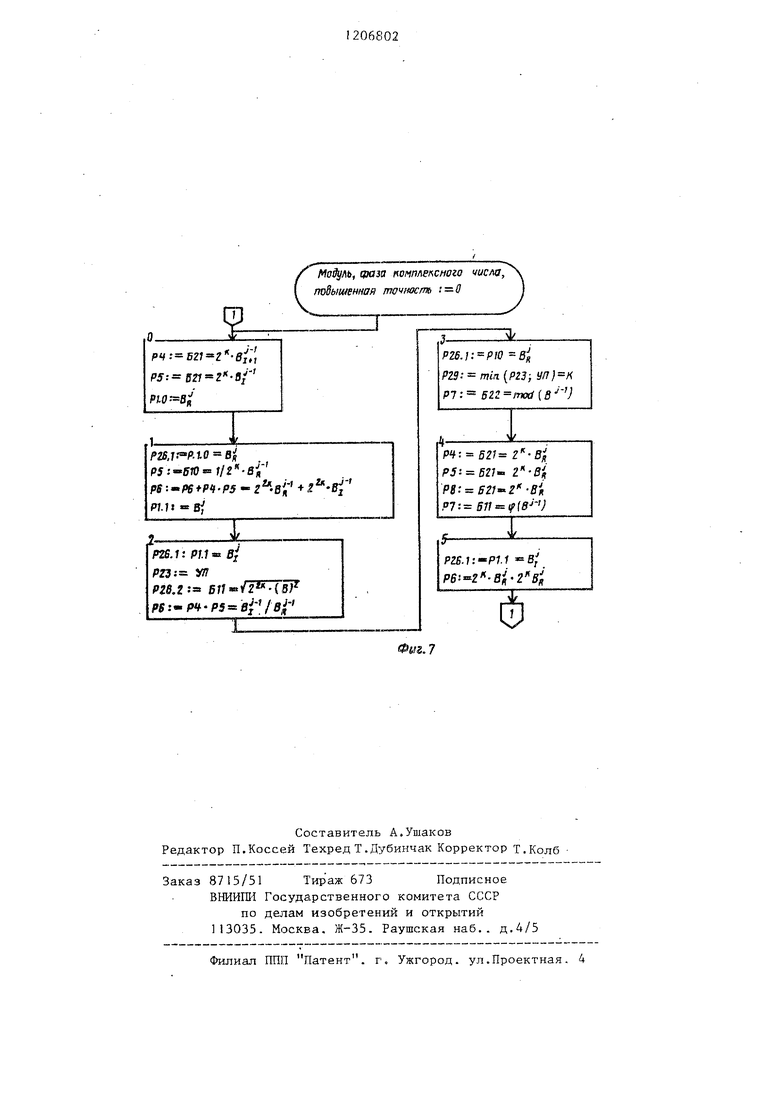

В первом варианте устройства результаты имеют не менее п/2 точных разрядов, где п - разрядность адреса блоков 10 и 11 памяти, В случае, если необходима более высокая точность результатов, применяется второй вариант арифметического устройства. Это арифметическое устройство при вычислении модуля и фазы комплексного числа работает следующим образом.

5

lf

5

В нулевом такте операнд, В-; тупает в регистр .О блока 1 ре- .гкстроз. В первом такте операндов пересылается из регистра 1.0 в регистр 26 операнда первого блока 21 сдвига, а в регистр 1. принимается операнд В. Во втором такте узел 30 анализа порядка блока 21 определяет количество нулей перед старшим значащим разрядом числа Вр из регистра 26 и код порядка, равный этому количеству, принимается регистром 23 порядка, а в регистр 26 блока 21 из регистра 1.1 пересылается опера.нд В- . В третьем такте узел 30 анализа порядка выдает код порядка для операнда В° , мультиплексор 25 пропускает меньший из кодов порядка для числа & и для числа Вц, хранящегося в регистре 23 порядка,, и этот код К запоминается в регистрах 29 кода сдвига первого 21 и второго 22 блоков сдвига, а в регистр 26 блока 2 принимается операнд Вц из регистра 1.0. В четвертом такте-операнд В в блоке 2 сдвига, пройдя через узел 27 сдви- гателя, оказьшается сдвинутым на К разрядов влево и операнд , пройдя через выходной ключ 28.блока 21, записывается в регистр 4, а пройдя далее через второй вход мультиплексора 9 и первый ключ 12, записьшает- ся соответственно в регистры 8 и 5, В пятом такте в регистр 26 блока 21 сдвига из регистра 1.1 пересылается операнд Bj. В это же время на умножителе 2 получается произведение 2-Bg;2 Вр , которое, пройдя через сумматор-вычитатель 3, записывается в регистр 6. В шестом такте сдвига- тель 27 блока 21 производит сдвиг содержимого регистра 26 на К разрядов влево и операнд 2. Bj из блока 21 пересылается в регистры 4 и 5 со- отв етственно, В этом же такте новьй операнд Ъу засылается в регистр 1.0 ;блока 1 регистров. В седьмом такте по адресу, определяемому числом .хранящемся в регистре 8, из блока 10 памяти выбирается код числа 1/ ( который записывается в регистр 5, одновременно умножитель 2 получает произведение 2 -В° 2 В , которое складьшается в сумматоре-вычитателе 3 с содержимым регистра 6 и дает сумму )Ч(В, )2 ЧВ°)% кото- рая записывается в регистр 6. В этом же такте в регистр 26 блока 2 пересылается новый операнд Вр из регист ра 1.0, а в регистр 1.1 записывается новый операнд В . В восьмом такте на адресный вход блока 11 памяти из регистра 6 подается код числа 2 .В, по которому из блока 11 выдается, код числа ) 2Vod(B ) который записьгаается в регистр 26 второго блока 22 сдвига. Одновременно произведение BR В° /В , пройдя через сумматор 3, записывается в регистр 6. В этом же такте код порядка для BR записывается в регистр 23, а в регистр 26 первого блока 21 сдвига пересылается из регистра 1 . 1 операнд Вт-. В девятом такте сдвигатель 27 блока 22 произ5 водит сдвиг вправо на К разрядов содержимого регистра 26 того же блока и результат mod(B°) из блока 22 пере- сьшается в регистр 7, а в регистры 30 блоков 21 и 22 записывается код

0 сдвига для новой пары операндов Ef

и Bf, в регистр 26 блока 21 записы-

вается операнд В . В десятом такте из регистра 6 на адресный вход блока 11 памяти выдается код операнда

О I О

5 BJ- /Вц, по которому с блока II выбирается число, равное результату arctg(Bj/B)4(B) , которое записывается в регистр 7. В этом же такте

блок 21 сдвига выдает сдвинутый опек 0 ранд 2 Вр, который записьшается в

регистры 4, 5 и 8. В дальнейшем работа арифметического устройства повторяется с периодом двенадцать тактов . Повьшение точности вычислений

5 достигается за счет того, что перед вычислениями, аналогичными как в первом варианте, пара исходных операндов нормализуется, что позволяет значительно уменьшить ошибку от де0 лениЯ, которое осуществляется умножением на обратную величину, от извлечения квадратного корня и нахождения арктангенса, поскольку ошибка получения табличной функции пропор5 циональна первой производной этой функции, а вблизи единицы первая производная перечисленных функций минимальна. После вычисления квадратного корня полученное число де-

0 нормализуется для получения истинного значения модуля комплексного числа.

Формула изобретения

1 Устройство для быстрого преобразования Фурье, содержащее умножитель, регистры числа и коэффициента, первый и второй регистры результата,

сумматор-вычитатель, блок микропрограммного управления, причем выходы регистров числа и коэффициента подключены к входам первого и второго операндов умножителя соответственно,

выход первого регистра результата

подключен к входу первого операнда сумматора-вычитателя, выход которого подключен к информационному входу

первого регистра результата, выход второго регистра результата является выходом устройства, вход тактовых импульсов блока микропрограммного управления является одноименным входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет вычисления усредненияs модуля и фазы комплексных чисел, в него введены блок регистровой памяти мультиплексор, регистр адреса, два ключа, выполненных с трехстабильными выходами, блок памяти весовых коэф- фициентов, блок памяти значений арктангенса, адресный вход и вькод которого поразрядно обьединены с ин- формационньм входом и выходом второго ключа соответственно и подключены к выходу первого регистра результата и информационному входу второго регистра результата соответственно , выход умножителя подключен к входу второго операнда сумматора-вы- читателя, информационный вход блока рягкс-провой панг; :-и является инфор- -.:а1дас ,-шам вхс.пси устройства, выход блока регистровой памяти подклю тек к инсЬормадиокным входам регистра чнсла, первого ключа и мультиплсксора, выход которого подключен к информационному Влоду регистрй. адреса , зыход которого подключен через блов памяти весовых козффиц;1ек Г Ов к ин- формационному входу регистра циекта, адресный вход мультиплексора йлляется одноименным входом устройства, выход первого ключа подключен ,:. информационному входу регистра ко- зффициента, вход сброса и входы признаков блока микропрограммного управления являются входом начальной уста новки и входами задания режима устройства соответственно, с первого по четвертый выходы блока микропрограммного управления соединенна с входами адреса записи и адреса считывания блока регистровой памяти, входа сигналов записи и выборки кото- рого соединены с пятым и шестым выходами блока микропрограммного управления соответственно, седьмой, восьмой и девятый выходы которого соединены с разрешающими входами ре- гистра числа, регистра коэффициента и первого регистра результата соответственно, управляющие вхэды сумматора-вычитателя соединены с десятым и одиннадцатым выходами блока микропрограммног о упразления, двенадцатый выход ко7 срого соединен с входом выборки мультиплексора, вход управления которого соединен с входом- первого признака блока микропрограммного управления, тринадцаты и четырнадцатый выходы которого соединены с разрешающими входами ре гистра адреса и второго регистра результата соответствемно, вход стро- бирования первого ключа соединен с инверсным входом выдачи инфоргтации блока памяти весовых коэффициентов м соединен с пятнадцатым выходом блока микропрограммного управления, пестнадцатый и семнадцатый выходы которого соединены с входом выборки зоны памяти и входом -выдачи информации блока памяти значений арктангенса, вход выбора зоны памяти блок памяти весовых коэффициентов и значений косинуса соединен с входом втрого признака блока микропрограммно О управления, зосемнадцат .:й кoтop.ro сое,ди.-:ен с нхсдо -: -Тро Зи - рования второго ключа.

2. Устройство по п. 1 , о т л и - ч а ю щ е а с я тем, что, с целью п овьпления точности за счет нормализации исходных операндов, в Kei o вв .день первый к второй блоки сдвига, информационные входы-выходы которых подключены к выходу блока регистро- зой памяти и к выходу арктангеисио- го преобразователя соответственно, регистр порядка, схема сравнения и мультиплексор порядка, выход которого подключен к входам кода сдви- rs первого и второго блоков сдвига выход порядка первого блока сдвига соединен с первыми информационными вхс ггами мультиплексора порядка схемы сравкения и с информагщонным входом регистрг порядка, выход которо- г о иодьспючея к вторьм информацион- Hbns3 входам мультиплексора порядка и срайнения, выход которой подключен к входу управления муль- тигшексора порядка причем каждый блок сдвига содержит регистр операнда, сдвигатель, выходной ключ, регистр кода сдвига, а первый блок сдвига дополнительно содержит узел анализа порядк-ч, выход которого является выходом порядка первого бло-

ка сдвига, а вход соединен с выходом регистра операнда и входом сдви- гателя первого блока сдвига, выход сдвигателя соединен с информационным входом выходного ключа, выход которого соединен с информационным входом регистра операнда и является информационным входом-выходом блока сдвига, информационный вход регистра кода сдвига является входом кода сдвига блока сдвига, выход регистра кода сдвига соединен с управляющим входом сдвигателя, разрешающий вход регистра операнда и

fat.l

вход стробирования выходного ключа первого блока сдвига соединены с девя-тнадцатым и двадцатым выходами блока микропрограммного управления двадцать первый выход которого соединен с разрешающим входом регистра кода сдвига первого блока cдвигa с разрешающими входами регистра кода сдвига и регистра операнда второго блока сдвига вход стробирования выходного ключа которого соединен с двадцать вторым выходом блока микропрограммного управле ния, .

/7

I

19

§ч

f

i

Kfe r:stia

й|..в

ргизжл1сззаг ви;

Ы

рэ г- ITS, i-t

, TTT

еч1

N

Фиг.З

/ SaiaSm операция вПФ IУ: m(

С

Модуль, рам комплесмага числа J -.О

Рб: ре p -pj fBi ; t(ff/ }

P4:Pll B i

PS-6t1 4/e -6ii Pl.O-si

)

p/.-EvW K mHS 8- }

PS-.-pf-ps af -djej, )

РЧ: ,j

P5:PI.,

(|в)

P/.

.

fi; arctg iPSf yff : f4-PS- -(8i)i

Р4:арпк {

J

ФыгЛ

С

Усреднение Jt О

/ Модцкь, фозя телексного числа, поВышетав mavftocm

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для быстрого преобразования Фурье | 1986 |

|

SU1392577A1 |

| Устройство для быстрого преобразования Фурье | 1989 |

|

SU1633425A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для вычисления скользящего спектра | 1988 |

|

SU1527642A1 |

Изобретение относится к области вычислительной техники и позволяет одновременно с вьтолнением базовой операции быстрого преобразования Фурье вычислять усреднение, модуль и фазу комплексьшх чисел. Устройство содержит блок регистровой памяти, умножитель, сумматор-вычитатель, регистры числа и коэффициента, первый и второй регистры результата, регистр адреса, мультиплексор, блок памяти весовых коэффициентов, блок памяти значений арктангенса, два ключа, блок синхронизации. Для повышения точности вычислений предусмотрен вариант устройства со средствами нормализации чисел. I з.п. ф-лы, 7ил. i (Л

| Арифметическое устройство | 1981 |

|

SU1012240A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ящик для хранения катушек швейных ниток и пользования ими | 1924 |

|

SU1896A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-23—Публикация

1984-08-25—Подача