Изобретение относится к автоматике и вычислительной технике и может быть использовано для оперативного вывода информации из вычислительных машин на матричные экраны в форме, удобной для восприятия зрительным анализатором человека-оператора.

Цель изобретения - расширение возможностей устройства за счет отображения символов любого начертания и различных по размерам.

В основе принципа построения и работы устройства лежит кодовый эквивалент символа, подлежащего отображению. Этот кодовый эквивалент в рассматриваемом случае имеет следующий вид:

{ vj} =  { XoYo, np xi, np yi, sign yi, nizi} , где Nj - количество участков в образующей i-го отображаемого символа;

{ XoYo, np xi, np yi, sign yi, nizi} , где Nj - количество участков в образующей i-го отображаемого символа;

ni - количество элементов разложения в i-м участке образующей символа;

Xo, Yo - координаты исходной точки, относительно которой отображается символ Vj;

0, если i-й участок вертикальный, { прXi} =

1, в противном случае;

0, если i-й участок горизонтальный, { прYi} =

1, в противном случае;

1, если Xi при отображении { sign Xi} = i-го участке увеличивается,

0, если уменьшается;

1, если Yi при отображении { sign Yi} = i -го участка увеличивается;

0, если уменьшается;

1, если i-й участок в образующей { zi} = символа подлежит отображению;

0, если не подлежит.

Структурная схема устройства изображена на фиг. 1. В ее состав входят первый 1, второй 2, третий 3 и четвертый 4 регистры, первый 5, второй 6, третий 7, четвертый 8, пятый 9, шестой 10 триггеры, счетчик 11, первый 12 и второй 13 дешифраторы, первая 14 и вторая 15 группы ключей, матричный индикатор 16, первый элемент 17 задержки, первый 18 и второй 19 элементы И, первый генератор 20, первый элемент ИЛИ 21, третий 22 и четвертый 23 элементы И, второй генератор 24, блок сравнения 25, второй элемент 26 задержки, пятый элемент И 27, третий элемент 28 задержки.

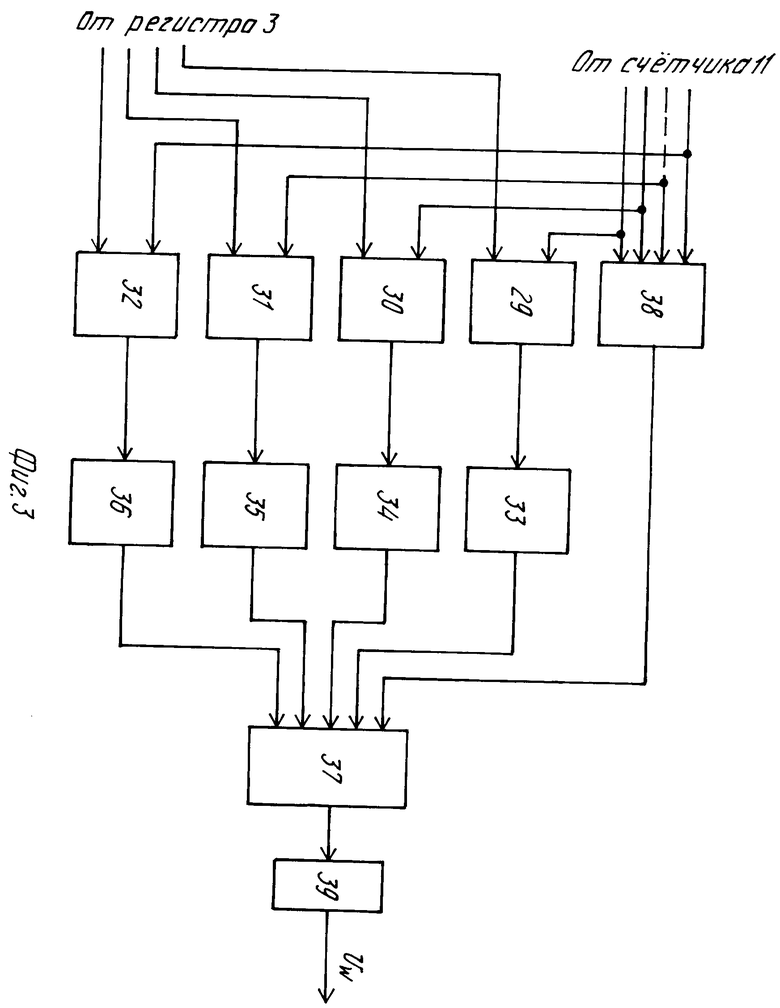

На фиг. 2 изображены эпюры сигналов, поясняющие работу устройства; на фиг. 3 изображена структурная схема блока 25 сравнения с блокировкой выходного сигнала при входных числах, равных нулю. В его состав входят первый 29, второй 30, третий 31 и четвертый 32 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 33, второй 34, третий 35 и четвертый 36 инверторы, шестой элемент И 37, второй элемент ИЛИ 38 и дифференцирующий элемент 39.

Сущность изобретения состоит в том, что устройство дополнено элементами с соответствующими связями между ними. Это позволяет отображать на матричном экране символы любого начертания и различных размеров, что соответствует критерию "существенные отличия".

Устройство работает следующим образом.

Первоначально от блока буферной памяти (не показан) по первому управляющему входу R поступает импульс UR (фиг. 2). Этот импульс подводится к первым управляющим входам первого 1, второго 2, третьего 3 и четвертого 4 регистров, первого 5, второго 6, третьего 7, четвертого 8 и пятого 9 триггеров и цифрового двоичного счетчика 11 и сбрасывает их в ноль. Затем от блока буферной памяти по второму управляющему входу V подводится импульс Vv к вторым управляющим входам регистров 1, 2 и 4 и к третьим управляющим входам регистров 3 и триггеров 5-9. Под воздействием этого импульса из блока буферной памяти по информационным входам в регистр 1 засылается { Xo} , в регистр 2 - { Yo} , в регистр 3 - { ni+1} , в регистр 4 - { Nj} , в триггер 5 - { прXi} , в триггер 6 - { прYi} , в триггер 7 - { sign Xi} , в триггер 8 - { sign Yi} , в триггер 9 - { zi} . Импульсом Uvшестой триггер 10 сбрасывается в ноль, так как этот импульс подводится к его первому входу.

Выходы регистра 1 замыкаются на входы первого дешифратора 12, а выходы регистра 2 - на входы второго дешифратора 13. Содержимое регистра 1 определяет номер выхода дешифратора 12, а регистра 2 - дешифратора 13. Выходы дешифратора 12 замыкаются через первый блок 14 ключей на вертикальные входы матричного индикатора 16, а выходы дешифратора 13 через второй блок 15 ключей - на горизонтальные, чем достигается выбор исходного элемента разложения [Xo, Yo] матричного индикатора.

На время загрузки регистров 1 и 2 и выбора исходных выходов дешифраторов 13 и 14 импульс Uv задерживается в первом элементе 17 задержки, первый вход которого подключен к входу V устройства, а выход - к первым входам первого 18 и второго 19 элементов И. Второй вход элемента И 18 подключен к первому выходу триггера 9, а второй вход элемента И 19 - к второму выходу этого триггера. Если { zi} = 1, то импульс VD, снимаемый с выхода элемента 17, проходит через элемент И 18, выход которого замыкается на первый вход первого генератора 20. Генератор 20 запускается, и с его выхода снимается импульс VG, который через первый элемент ИЛИ 21 подводятся к третьим входам третьего 22 и четвертого 23 элементов И. Первый вход элемента И 22 подключен к выходу триггера 5, а элемента И 23 - к выходу триггера 6. Вторые входы элементов И 22 и 23 подключены к выходу триггера 10.

Выход элемента И 22 подключен к пятому (счетному) входу регистра 1, третий и четвертый входы которого подключены соответственно к первому и второму выходам триггера 7. Если { singXi} = 1, то сигнал, эквивалентный единице, снимается с первого выхода триггера 7 и регистр 1 работает в режиме суммирования счетных импульсов, поступающих по его пятому входу. Если { sign Xi} = 0, то сигнал, эквивалентный единице, снимается с второго выхода триггера 7 и регистр 1 работает в режиме вычитания счетных импульсов, поступающих по его пятому входу.

Выход элемента И 23 подключен к пятому (счетному) входу регистра 2, третий и четвертый входы которого подключены соответственно к первому и второму выходам триггера 8. Если { sign Yi} = 1, то регистр 2 работает в режиме суммирования импульсов, поступающих по его пятому входу, а если { sign Yi} = 0, то - в режиме вычитания. Если { прXi} = 1, то с выхода триггера 5 снимается сигнал, эквивалентный единице, а если { прXi} = 0, то - нулю. Аналогично если { прYi} = 1, то с выхода триггера 6 снимается сигнал, эквивалентный единице, а если { прYi} = 0, то - нулю.

Первый импульс UG1, поступающий с выхода элемента ИЛИ 21 на третьи входы элементов И 22 и 23, через них не проходит, так как с выхода триггера 10, который замыкается на второй вход этих элементов, снимается сигнал, эквивалентный нулю. Первый импульс UG1, который с выхода элемента ИЛИ 21 через третий элемент 28 задержки, в котором задерживается на длительность входного сигнала, подводится к второму входу триггера 10, перебрасывает этот триггер в противоположное состояние (устанавливает его в состояние "1").

Если { прXi} = 1, а { прYi} = 0, то импульсы UG1, начиная с второго, проходят через элемент И 22, обуславливая изменение содержимого регистра 1 (в сторону его увеличения или уменьшения), чем достигается перекоммутация выходов дешифратора. Если { zi} = = 1, то это обуславливает через блок 14 ключей перекоммутацию вертикальных выводов индикатора 16, так как первый выход триггера 9 замыкается на группу входов блока 14 ключей (и блока 15 ключей). С выбираемых выходов дешифратора 12 относительно выхода { Xo} снимаются прямоугольные импульсы Ux1, Ux2, Ux3, Ux4, Ux5, Ux6 и Ux7 (при ni = 7), длительность которых равна периоду следования импульсов UG1, чем достигается возбуждение соответствующих элементов разложения индикатора 16, включая элемент [Xo, Yo] , т. е. отображение первого (в общем случае i-го) отрезка образующей графического символа.

При { прXi} = 0, { прYi} = 1 и { zi} = 1 перекоммутируются горизонтальные выводы индикатора 16 через дешифратор 13 и блок 15 ключей. Если { прXi} = 1, { прYi} = 1 и { zi} = 1, перекоммутация осуществляется как вертикальных, так и горизонтальных выводов индикатора 16, чем достигается отображение участков в образующих символов, ориентированных относительно оси абсцисс под углами 4, 135, 225 и 315о.

Когда { zi} = 0, т. е. участок образующей не подлежит отображению, то сигнал, эквивалентный единице, снимается с второго выхода триггера 9, который замыкается на второй вход элемента И 19. В этом случае импульс UD с выхода элемента 17 проходит через элемент И 19, выход которого подключен к первому входу второго генератора 24, и запускает его. Если период следования импульсов UG1 определяет яркость отображаемых символов и в зависимости от типа индикатора 16 лежит в пределах 2-10 мкс, то период следования выходных импульсов генератора 24 определяет только скорость изменения содержимого регистров 1 и 2. Поэтому период следования импульсов, снимаемых с выхода генератора 24, в 100-300 раз меньше периода следования импульсов UG1, что уменьшает время отображения символов и, как следствие, повышает быстродействие устройства.

Выходные импульсы генератора 20 (или 24) через элемент ИЛИ 21 подводятся к третьему (счетному) входу счетчика 11. После отображения ni элементов разложения индикатора 16 (или после изменения содержимого регистров 1 и 2 на ni содержимое счетчика 11 оказывается равным { ni + 1} , и с выхода блока 25 сравнения, на первую группу входов которого замыкаются выходы счетчика 11, а на вторую - регистра 3, снимается импульс UW, который подводится к вторым входам счетчика 11, регистра 3 и триггеров 5-9 и сбрасывает из в ноль. Кроме того, импульс UW подводится к второму входу генераторов 20 и 24 и срывает генерацию. Импульс UW, как и в устройстве-прототипе, подводится к блоку буферной памяти, информируя его об окончании процесса отображения i-го участка образующей символа. Этот импульс подводится к входу второго элемента 26 задержки, в котором задерживается на время сброса счетчика 11, регистра 3 и триггеров 5-9 в ноль. С выхода элемента 26 задержанный импульс UW подводится к четвертым входам регистра 3 и триггеров 5-9. Под воздействием этого импульса из блока буферной памяти по информационным шинам в регистр 3 засылается ni+1 + 1, в триггер 5 - { прXi+1} , в триггер 6 - { прYi+1} , в триггер 7 - { sign Xi+1} , в триггер 8 - { singYi+1} и в триггер 9 - { zi+1} , и описанный процесс повторяется, так как второй вход элемента 17 подключен к выходу элемента 26, и задержанный импульс UW выполняет функции импульса Uv, который поступает к первому входу элемента 17.

Импульс UW с выхода блока 25 поступает также на третий (счетный) вход регистра 4, который работает в режиме вычитания, т. е. с течением времени содержимое регистра 4 уменьшается. По окончании отображения последнего Nj-го отрезка в образующей символа содержимое регистра 4 становится равным нулю, и с выхода пятого элемента И 27 снимается импульс UW1, который подводится к блоку буферной памяти, информируя его об окончании процесса отображения данного символа.

В качестве примера, чтобы не возникли сомнения в работоспособности устройства, когда содержимое регистра 3 и счетчика 11 равно нулю, на фиг. 3 приведена структурная схема четырехразрядного блока 25 сравнения с блокировкой выходного сигнала при нулевых числах на его входах. Если числа на его первой и второй группах входов равны нулю, с выходов первого 29, второго 30, третьего 31 и четвертого 32 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ снимаются сигналы "Лог. 0", а с выходов первого 33, второго 34, третьего 35 и четвертого 36 - инверторов "Лог. 1". Эти сигналы подводятся к второму, третьему, четвертому и пятому входам шестого элемента И 37, с выхода которого снимается сигнал "Лог. 0", так как с выхода второго элемента ИЛИ 38 снимается сигнал "Лог. 0", который подводится к первому входу этого элемента.

Если входные числа равны между собой и не равны нулю, то с выхода элемента ИЛИ 38 снимается сигнал "Лог. 1", и с выхода элемента И 37 снимается сигнал "Лог. 1", который поступает на вход дифференцирующего элемента 39, с выхода которого снимается кратковременный импульс.

Если входные числа не равны, то с выхода одного или нескольких элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 29-32 снимается сигнал "Лог. 1", а с выхода соответствующего инвертора 33-36 - "Лог. 0", в результате чего сигнал на выходе элемента И 37 также равен "Лог. 0".

Технико-экономическая эффективность предлагаемого устройства заключается в отображении символов различных размеров и любого начертания. (56) Авторское свидетельство СССР N 1124374, кл. G 09 G 3/28, 1983.

Говоров В. С. , Исмагилов Д. И. Преобразователи машинного кода в графические символы. Киев: Техника, с. 162.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ СИМВОЛОВ НА МАТРИЧНОМ ИНДИКАТОРЕ | 1991 |

|

RU2006961C1 |

| ФОРМИРОВАТЕЛЬ АДРЕСА | 1989 |

|

RU2025046C1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1988 |

|

SU1654862A1 |

| Устройство для отображения символов на экране электронно-лучевой трубки | 1985 |

|

SU1280437A1 |

| Устройство для отображения символов на экране электронно-лучевой трубки | 1991 |

|

SU1833915A1 |

| Устройство для адресации памяти | 1990 |

|

SU1753476A1 |

| Устройство для отображения символов на экране электронно-лучевой трубки | 1985 |

|

SU1293753A1 |

| Устройство для преобразования чисел | 1990 |

|

SU1730614A1 |

| Устройство для преобразования чисел из десятичной в двоичную систему счисления | 1989 |

|

SU1649526A1 |

| Преобразователь код-временной интервал | 1989 |

|

SU1695507A1 |

Использование: автоматика и вычислительная техника, системы сбора и отображения информации. Сущность изобретения: устройство содержит регистры 1 - 4, триггеры 5 - 10, элементы И 18, 19, 22, 23, 27, элементы 26, 17, 28 задержки, элемент ИЛИ 21, дешифраторы 12, 13, счетчик 11, группы 14, 15 ключей, матричный индикатор 16, блок 25 сравнения, генераторы 20, 24 импульсов. 3 ил.

УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ СИМВОЛОВ НА МАТРИЧНОМ ИНДИКАТОРЕ, содержащее три регистра, два дешифратора, первый генератор тактовых импульсов, два элемента И, элемент ИЛИ, блок сравнения, первый элемент задержки, счетчик и матричный индикатор, вертикальные шины которого подключены к выходам ключей первой группы, информационные входы которых подключены к выходам первого дешифратора, информационные входы которого подключены к выходам первого регистра, информационный вход которого является первым информационным входом устройства, а первый установочный вход соединен с первыми установочными входами второго и третьего регистров, первого триггера и счетчика и является установочным входом устройства, первый управляющий вход первого регистра соединен с первыми управляющими входами второго и третьего регистров и первого триггера и является управляющим входом устройства, информационные входы второго дешифратора подключены к выходам второго регистра, информационный вход которого является вторым информационным входом устройства, информационный вход третьего регистра является третьим информационным входом устройства, выходы третьего регистра подключены к первому информационному входу блока сравнения, второй информационный вход которого подключен к выходам счетчика, второй установочный вход которого соединен с вторым установочным входом третьего регистра и первого триггера и является первым выходом устройства, тактовый вход счетчика подключен к выходу первого элемента ИЛИ, отличающееся тем, что в него введены четвертый регистр, пять триггеров, два элемента И, второй генератор тактовых импульсов, два элемента задержки, информационный вход четвертого регистра является четвертым информационным входом устройства, второй управляющий вход четвертого регистра соединен с входом пятого элемента И, входом второго элемента задержки, вторыми установочными входами второго - пятого триггеров и первыми управляющими входами первого и второго генераторов тактовых импульсов, выходы которого подключены к первому и второму входам элемента ИЛИ, а вторые управляющие входы подключены к выходам соответственно первого и второго элементов И, первые входы которых подключены к выходу первого элемента задержки, а вторые входы - соответственно к прямому и инверсному выходам пятого триггера, информационный вход которого является пятым информационным входом устройства, а второй управляющий вход пятого триггера соединен с вторыми управляющими входами второго, третьего и четвертого триггеров и выходом второго элемента задержки, информационные входы первого - четвертого триггеров являются соответственно шестым - девятым информационными входами устройства, выходы первого и второго триггеров подключены к первым входам третьего и четвертого элементов И, вторые входы которых подключены к выходу шестого триггера, а третьи входы соединены с выходом элемента ИЛИ и с входом третьего элемента задержки, выход которого подключен к входу "Установка 1" пятого триггера, вход "Установка 0" которого соединен с первым управляющим входом третьего триггера, прямой и инверсный выходы которого подключены соответственно к второму и третьему управляющим входам первого регистра, второй и третий управляющие входы второго регистра подключены соответственно к прямому и инверсному выходам четвертого триггера, четвертые управляюище входы первого и второго регистров подключены к выходам соответственно третьего и четвертого элементов И, вход первого элемента задержки соединен с первым управляющим входом первого регистра, входы групп пятого элемента И подключены к выходам четвертого регистра, а выход является вторым выходом устройства, горизонтальные шины матричного индикатора подключены к выходам ключей второй группы, информационные входы которых подключены к выходам второго дешифратора, управляющие входы ключей первой и второй групп подключены к прямому выходу пятого триггера, вход первого элемента задержки подключен к выходу второго элемента задержки.

Авторы

Даты

1994-01-30—Публикация

1991-07-01—Подача