Изобретение относится к области автоматики и вычислительной техники и может быть использовано для выбора корпуса большой интегральной схемы модуля ре- программируемой памяти и формирования адреса символа применительно к этому корпусу по номеру инструкции или текста, хранящихся в этом модуле

Известно устройство аналогичного назначения, содержащее селектор-мультиплексор, тактовый генератор, генератор строба, цифровой двоичный счетчик и дешифратор.

Наиболее близким к предлагаемому является устройство, содержащее ждущий генератор, элемент ИЛИ и двоичный счетчик

Недостаток этих устройств состоит в том, что для формирования номера большой интегральной схемы (БИС), входящей в модуль репрограммируемой памяти (ОРЗУ), и адреса символа применительно к данной БИС предлагается использование микропроцессора, т е. выполнение устройств по принципу гибкой логики, что значительно усложняет и удорожает их.

Цель изобретения - расширение функциональных возможностей устройства за счет возможности преобразования номера инструкции в требуемый номер корпуса памяти и адрес в рамках корпуса.

Эта цель достигается тем, что в устройство, содержащее ждущий генератор, элемент ИЛИ и двоичный счетчик, в ведены два регистра, четыре счетчика, две схемы сравнения, два элемента И, ждущий генератор, причем первый синхровход устройства подключен к синхровходу первого регистра, входам начальной установки счетчиков с

VJ

сл со

VJ

о

первого по четвертый и к входу запуска первого ждущего генератора, выход которого подключен к счетному входу четвертого счетчика, выходы которого подключены к выходам адреса символа устройства и к вхо- дам первого элемента И, выход которого подключен к входу установки в ноль четвертого счетчика и к счетному входу третьего счетчика, выход которого подключен к выходу номера корпуса памяти устройства, выхо- ды второго счетчика подключены к входам второго элемента И, выход которого под- ключе н к входу установки и в ноль второго счетчика и счетному входу первого счетчика, выход которого подключен к первому входу первой схемы сравнения, вход номера инструкции устройства подключен к информационному входу первого регистра, выход которого подключен к второму входу первой схемы сравнения, выход которой подклю- чен к входу индикации завершения определения номера корпуса памяти устройства, второй синхровход устройства подключен к синхровходу второго регистра, входу начальной установки Пятого счетчика и к входу запуска второго ждущего генератора, вход номера символа в инструкции устройства подключен к информационному входу второго регистра, выход которого подключен к первому входу второй схемы сравнения, вы- ход которой подключен к выходу индикации завершения формирования адреса устройства и к входу останова второго ждущего генератора, выход которого подключен к второму входу элемента ИЛИ и счетному входу пятого счетчика, выход которого подключен к второму входу второй схемы сравнения.

Сущность изобретения состоит в том, что устройство, выполненное по принципу жесткой логики, позволяет управлять модулем репрограммируемой памяти без усложнения структуры устройства при любом количестве инструкций, которые хранятся в модуле РПЗУ с целью их отображения и с возможностью замены БИС РПЗУ кодов устаревших символов.

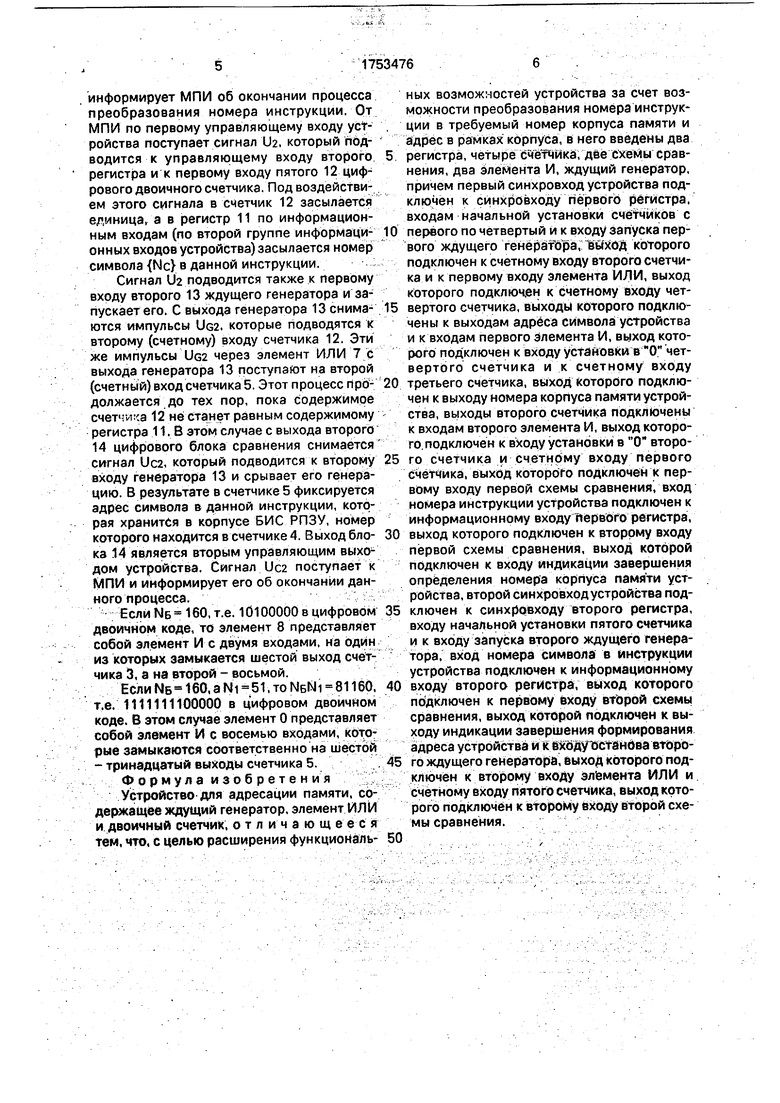

На фиг. 1 дана структурная схема устройства; на фиг. 2 - эпюры сигналов, пояс- няющие работу устройства.

На схеме обозначены первый 1 регистр, первый 2, второй 3, третий 4 и четвертый 5 цифровые двоичные счетчики, первый ждущий генератор 6, элемент ИЛИ 7, первый 8 и второй 9 элементы И, первый блок 10 сравнения, второй регистр 11, пятый цифровой двоичный счетчик 12, второй ждущий генератор 13 и второй цифровой блок 14 сравнения.

Устройство (фиг. 1) работает в следующей последовательности.

Сигнал Ui (фиг. 2), поступающий от МПИ по первому управляющему входу устройства, подводится к управляющему входу первого регистра 1 и первому входу первого 2, второго 3 и третьего 4 цифровых двоичных счетчиков, а также к первому входу четвертого цифрового двоичного счетчика 5. Под воздействием этого сигнала в счетчик 2 засылается единица, а счетчики 3-5 устанавливаются в нуль. Под воздействием сигнала Ui в регистр 1 по информационным входам засылается номер инструкции {Ми} (по первой группе информационных входов устройства).

Сигнал Ui подводится также к первому входу первого ждущего генератора и запускает его. С выхода генератора 6 снимаются импульсы UGI, которые поступают на второй (счетнцй) вход счетчика 3 и через элемент ИЛИ 7 - на второй (счетный) вход счетчика 5.

Выходы счетчика 3 замыкаются на входы первого 8 элемента И. Когда содержимое счетчика 3 становится равным NB, с выхода элемента И 8 снимается сигнал, который подводится к второму (счетному) входу счетчика 2 и увеличивает его содержимое на единицу. Этот же сигнал с выхода элемента 8 подводится к третьему (второму управляющему) входу счетчика 3 и сбрасывает его в нуль.

Импульсы UGI с выхода генератора б через элемент ИЛИ 7 подводятся к второму (счетному) входу счетчика 5. Когда его содержимое становится равным NI.NB, с выхода второго элемента И 9 снимается сигнал, который подводится к третьему входу счетчика 5 и сбрасывает его в нуль. Этот же сигнал с выхода элемента 9 подводится к второму (счетному) входу счетчика 4 и увеличивает его содержимое на единицу.

Рассмотренный процесс продолжается до тех пор, пока содержимое счетчика 2 не станет равным содержимому регистра 1. В этом случае с выхода первого 10 цифрового блока сравнения снимается сигнал Uci, который подводится к второму входу генератора б и срывает его генерацию. В результате в счетчике 4 фиксируется номер корпуса БИС РПЗУ, в котором находится инструкция, номер которой равен {Ми} и находится в регистре 1, а в счетчике 5 - адрес первого символа в инструкции применительно к данному номеру корпуса БИС РПЗУ. Выход блока 10 является первым управляющим выходом устройства.

Сигнал Uci с выхода блока 10 подводится к МПИ. Передний фронт этого сигнала

информирует МПИ об окончании процесса преобразования номера инструкции. От МПИ по первому управляющему входу устройства поступает сигнал U2, который подводится к управляющему входу второго регистра и к первому входу пятого 12 цифрового двоичного счетчика. Под воздействием этого сигнала в счетчик 12 засылается единица, а в регистр 11 по информационным входам (по второй группе информационных входов устройства) засылается номер символа {Nc} в данной инструкции.

Сигнал Ua подводится также к первому входу второго 13 ждущего генератора и запускает его. С выхода генератора 13 снимаются импульсы UG2. которые подводятся к второму (счетному) входу счетчика 12. Эти же импульсы Uoa через элемент ИЛИ 7 с выхода генератора 13 поступают на второй (счетный) вход счетчика 5. Этот процесс продолжается до тех пор, пока содержимое счет -ича 12 не станет равным содержимому регистра 11, В этом случае с выхода второго 14 цифрового блока сравнения снимается сигнал Uca, который подводится к второму входу генератора 13 и срывает его генерацию. В результате в счетчике 5 фиксируется адрес символа в данной инструкции, которая хранится в корпусе БИС РПЗУ, номер которого находится в счетчике 4. Выход блока 14 является вторым управляющим выходом устройства. Сигнал Ucz поступает к МПИ и информирует его об окончании данного процесса.

Если NB 160, т.е. 10100000 в цифровом двоичном коде, то элемент 8 представляет собой элемент И с двумя входами, на один из которых замыкается шестой выход счетчика 3, а на второй - восьмой.

Если ЫБ 160, a Ni -51, то NeNi 81160, т.е. 1111111100000 в цифровом двоичном коде. В этом случае элемент 0 представляет собой элемент И с восемью входами, которые замыкаются соответственно на шестой - тринадцатый выходы счетчика 5.

Формула изобретения

Устройство для адресации памяти, содержащее ждущий генератор, элемент ИЛИ и двоичный счетчик, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет возможности преобразования номера инструкции в требуемый номер корпуса памяти и адрес в рамках корпуса, в него введены два

регистра, четыре счетРчика, две схемы сравнения, два элемента И, ждущий генератор, причем первый синхровход устройства подключен к синхровходу первого регистра, входам начальной установки счетчиков с

первого по четвертый и к входу запуска первого ждущего генератора, выход которого подключен к счетному входу второго счетчика и к первому входу элемента ИЛИ, выход которого подключен к счетному входу четвертого счетчика, выходы которого подключены к выходам адреса символа устройства и к входам первого элемента И, выход которого подключен к входу установки в О чет- вертого счетчика и к счетному входу

третьего счетчика, выход которого подключен к выходу номера корпуса памяти устройства, выходы второго счетчика подключены к входам второго элемента И, выход которого подключен к входу установки в О второго счетчика и счетному входу первого счетчика, выход которого подключен к первому входу первой схемы сравнения, вход номера инструкции устройства подключен к информационному входу Первого регистра,

выход которого подключен к второму входу первой схемы сравнения, выход которой подключен к входу индикации завершения определения номера корпуса памяти устройства, второй синхровход устройства подключей к синхровходу второго регистра, входу начальной установки пятого счетчика и к входу запуска второго ждущего генератора, вход номера символа в инструкции устройства подключен к информационному

входу второго регистра, выход которого подключен к первому входу второй схемы сравнения, выход которой подключен к выходу индикации завершения формирования адреса устройства и к входу останова второго ждущего генератора, выход которого подключен к второму входу элемента ИЛИ и счетному входу пятого счетчика, выход которого подключен к второму входу второй схемы сравнения.

CUN&MQ

Фиг J

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ АДРЕСА | 1989 |

|

RU2025046C1 |

| Устройство для преобразования чисел | 1990 |

|

SU1730614A1 |

| Формирователь символов для устройств отображения информации на матричных экранах | 1989 |

|

SU1688280A1 |

| Устройство для формирования сигналов алфавитно-цифровых и графических изображений | 1982 |

|

SU1083406A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1508272A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1427412A1 |

| Устройство для измерения скорости движения моделей | 1986 |

|

SU1448282A1 |

| Генератор символов | 1989 |

|

SU1633386A1 |

| Многоканальный программируемый генератор импульсов | 1986 |

|

SU1374413A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для выбора корпуса большой интегральной схемы модуля репрограмми- руемой памяти и формирования адреса символа применительно к этому корпусу по номеру инструкции или текста, хранящихся в этом модуле Целью изобретения является расширение функциональных возможностей устройства за счет преобразования номера инструкции в требуемый номер корпуса памяти и адрес в рамках корпуса. Цель достигается тем, что в устройство, содержащее первый ждущий генератор, элемент ИЛИ и первый цифровой двоичный счетчик, введены два регистра, четыре двоичных счетчика, две схемы сравнения, два элемента И и второй ждущий генератор 2 ил. СО С

,,-JJJJJL...ll

СУ

Ч

us

X

tfcr

t

ИМИ IN

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| УСТРОЙСТВО ДЛЯ ПРЕДУПРЕЖДЕНИЯ РАЗМЫВОВ ДНА У ВОДОСПУСКОВ ПЛОТИН, ВОДОСЛИВОВ И ДРУГИХ ГИДРОТЕХНИЧЕСКИХ СООРУЖЕНИЙ | 1925 |

|

SU2387A1 |

| Устройство вывода информации | |||

| ПРИБОР ДЛЯ ПАРАЛЛЕЛЬНОЙ УСТАНОВКИ ПРЕДМЕТОВ | 1927 |

|

SU6205A1 |

| Ровно, п/я А-7208, 1980, с 22-25 | |||

Авторы

Даты

1992-08-07—Публикация

1990-02-21—Подача