Изобретение относится к преобразовательной технике и может быть использовано для управления тиристорами в непосредственных преобразователях частоты.

Известен синхронизатор импульсов управления тиристорным преобразователем, который содержит три канала управления, каждый из которых состоит из блока индикации нулевого напряжения, выход которого через формирователь подключен к S-входу основного RS-триггера и через инвертор и дополнительный формирователь - к S-входу дополнительного RS-триггера. Основные RS-триггеры соединены по кольцевой схеме таким образом, что инверсный выход триггера последующего канала соединен с R-входом RS-триггера предыдущего канала. Аналогично соединены по кольцевой схеме дополнительные RS-триггеры. Кроме того, в каждом канале дополнительные R-входы основного и дополнительного триггеров данного канала подключены к инверсным выходам друг друга.

Синхронизатор работает следующим образом. При подаче на входы блоков индикации нулевого напряжения трехфазной системы синхронизирующих напряжений на их выходах образуются прямоугольные импульсы длительностью до 180 эл. град. , сдвинутые относительно друг друга на 120 эл. град. Эти импульсы инвертируются инверторами. Инвертируемые и неинвертируемые импульсы подаются на формирователи, на входах которых появляется последовательность коротких импульсов, сдвинутых относительно друг друга на 60 эл. град. Эти импульсы воздействуют на входы триггеров обоих колец основных и дополнительных триггеров, приводя к изменению их состояний в том случае, если на их R-входах отсутствуют сигналы, запрещающие переключение и которые формируются в результате логического сложения импульсов с инверсных выходов последующих триггеров данного кольца и триггеров другого кольца, S-входы которых связаны с предыдущей фазой питающей сети. Таким образом, результирующая длительность запрета составляет 180 эл. град. , т. е. на протяжении полупериода питающего напряжения частотой 50 Гц обеспечивается помехоустойчивость синхронизатора.

Однако при применении данного синхронизатора в непосредственных преобразователях частоты на 150 Гц не обеспечивается синхронизация импульсов управления по линейным напряжениям и снижается его помехоустойчивость, так как в этом случае для обеспечения помехоустойчивости требуется запрет на формирование импульсов синхронизации длительностью 300 эл. град. , который, как следует из характеристик синхронизатора, известный синхронизатор не обеспечивает. Следовательно, в пределах 120 эл. град при частоте 150 Гц возможно формирование ложных синхроимпульсов.

Целью изобретения является расширение функциональных возможностей и повышение помехоустойчивости.

Цель достигается тем, что в синхронизатор введены каналы управления по числу линейных напряжений, аналогичных каналам управления по фазным напряжениям, трехвходовые логические элементы И, количество которых определяется числом тиристоров непосредственного преобразователя частоты. Входы логических элементов соединены с соответствующими прямыми и инверсными выходами основных и дополнительных RS-триггеров каналов управления по фазным и линейным напряжениям, а именно к входам первого логического элемента 3И подключены инверсный и прямой выходы основных RS-триггеров первого и второго каналов управления по фазным напряжениям соответственно и прямой выход дополнительного RS-триггера третьего канала управления по фазному напряжению, к входам второго логического элемента 3И подключены инверсный и прямой выходы дополнительных RS-триггеров соответственно первого и второго каналов управления по фазным напряжениям и прямой выход основного RS-триггера третьего канала управления по фазному напряжению, входы третьего и пятого логических элементов 3И подключены аналогично входам первого логического элемента 3И, а входы четвертого и шестого логических элементов 3И подключены аналогично входам второго логического элемента 3И в порядке чередования фазных напряжений со сдвигом на один канал, аналогично, начиная с четвертого канала управления, подключены выходы каналов управления по линейным напряжениям к входам седьмого - двенадцатого логических элементов 3И в порядке чередования линейных напряжений.

Введение дополнительных каналов управления по числу линейных напряжений позволяет использовать предлагаемый синхронизатор на частоте 150 Гц. Введение трехвходовых логических элементов И и соответствующих связей между выходами каналов управления и входами логических элементов 3И обеспечивает повышение помехоустойчивости синхронизатора за счет расширения зоны запрета на формирование ложных синхроимпульсов со 180 до 300 эл. град.

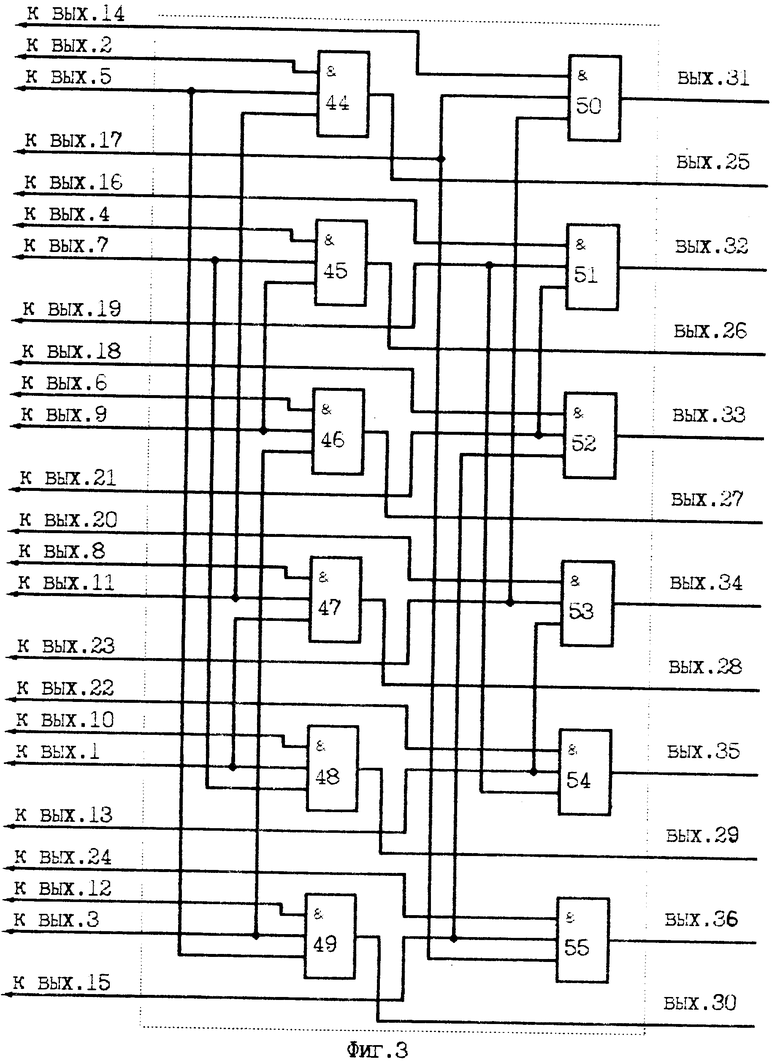

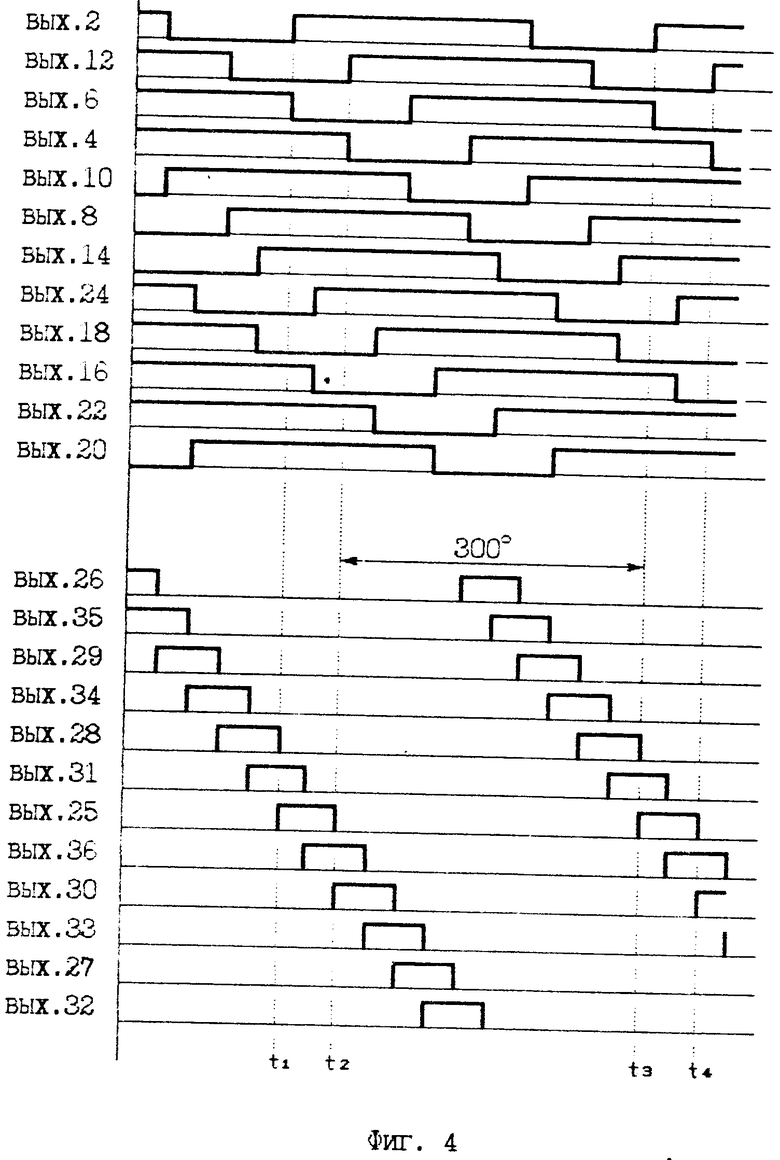

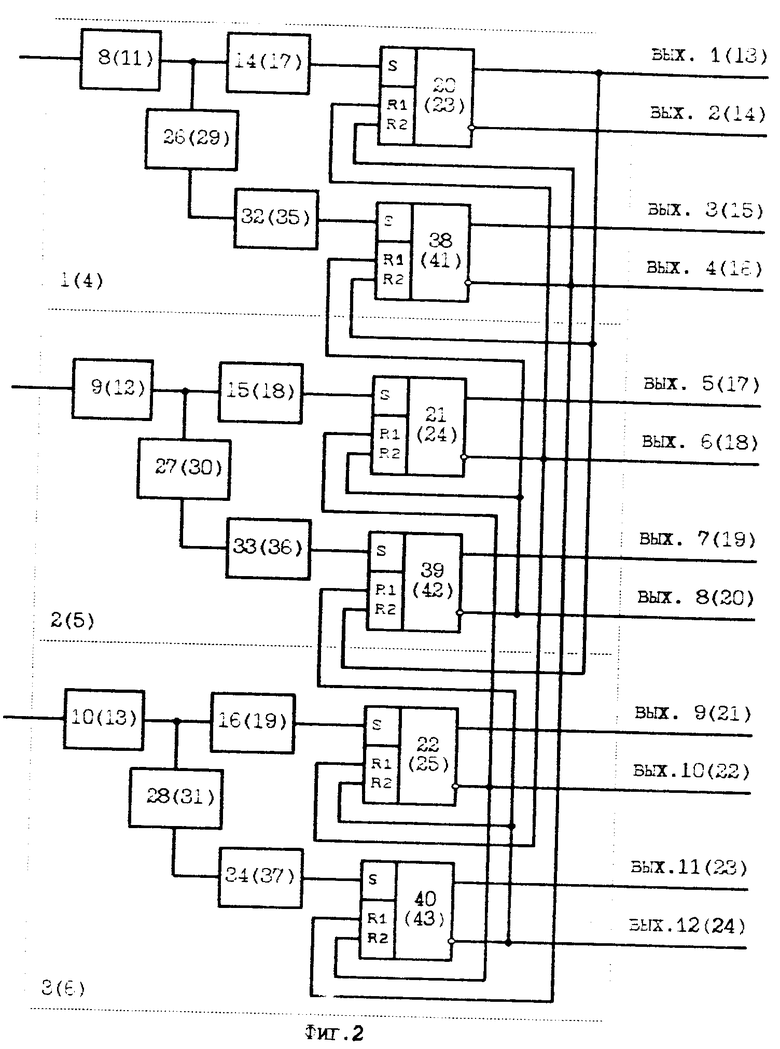

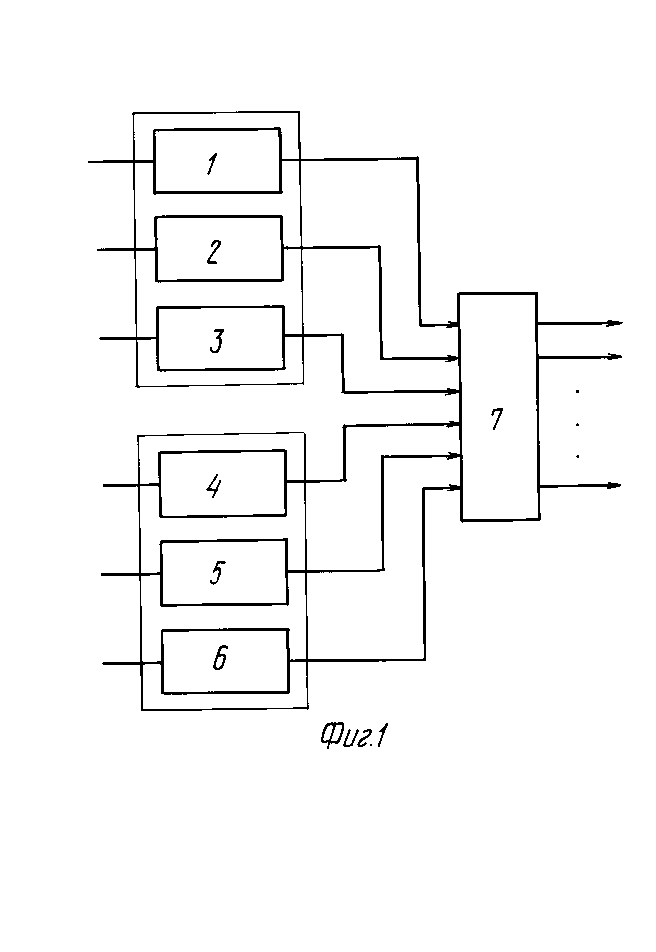

На фиг. 1 изображена структурная схема синхронизатора импульсов управления; где 1. . . 3 - каналы управления по фазным напряжениям , 4. . . 6 - каналы управления по линейным напряжениям, 7 - блок логических элементов; на фиг. 2 - принципиальная электрическая схема каналов управления по фазным (линейным) напряжениям, где 1. . . 3 - каналы управления по фазным напряжениям, 4. . . 6 - каналы управления по линейным напряжениям, 8. . . 10 (11. . . 13) - блоки индикации нулевого фазного (линейного) напряжения 14. . . 16 (17. . . 19) - формирователи импульсов в каналах управления по фазному (линейному) напряжению, 20. . . 22 (23. . . 25) - основные RS-триггеры в каналах управления по фазному (линейному) напряжению, 26. . . 28 (29. . . 31) - инверторы в каналах управления по фазному (линейному) напряжению, 32. . . 34 (35. . . 37) - дополнительные формирователи импульсов в каналах управления по фазному (линейному) напряжению, 38. . . 40 (41. . . 43) - дополнительные RS-триггеры в каналах управления по фазному (линейному) напряжению; на фиг. 3 - принципиальная электрическая схема блока логических элементов синхронизатора, где 44. . . 49 - трехвходовые логические элементы И каналов управления по фазному напряжению, 50. . . 55 - трехвходовые логические элементы И каналов управления по линейному напряжению; на фиг. 4 изображены диаграммы напряжений на выходах элементов синхронизатора на 150 Гц (фиг. 2 и 3). Каждый из каналов (1. . . 3) управления по фазному напряжению и каналов (4. . . 6) управления по линейному напряжению содержит (фиг. 2) блок 8 (9. . . 13) индикации нулевого напряжения, выход которого через формирователь 14 (15. . . 19) подключен к S-входу основного RS-триггера 20 (21. . . 25) и через инвертор 26 (27. . . 31) и дополнительный формирователь 32 (33. . . 37) - к S-входу дополнительного RS-триггера 38 (39. . . 43). Основные RS-триггеры 20. . . 25 соединены по кольцевой схеме так, что инверсный выход триггера последующего канала соединен с R-входом предыдущего канала. Аналогично соединены по кольцевой схеме дополнительные RS-триггеры 38. . . 43. Кроме того, в каждом канале 1. . . 6 дополнительные R-входы основного и дополнительного триггеров данного канала подключены к инверсным выходам друг друга. Прямые и инверсные выходы основных RS-триггеров 20. . . 25 и дополнительных RS-тригеров 38. . . 43 подключены к входам трехвходовых логических элементов И 44. . . 55 (фиг. 3) так, что для формирования импульсов синхронизации по фазному напряжению в каждом канале управления входы одного логического элемента И 44 (46, 48) соединены с инверсным выходом основного RS-триггера 20 (21, 22) этого же канала 1 (2, 3) управления по фазному напряжению и прямыми выходами основного и дополнительного RS-триггеров 21 и 40 (22 и 38, 20 и 39) соответственно в порядке чередования фаз других каналов 2 и 3 (3 и 1, 1 и 2) управления по фазному напряжению. Входы другого логического элемента И 45 (47, 49) соединены с инверсным выходом дополнительного RS-триггера 38 (39, 40) этого же канала 1 (2, 3) управления, по фазному напряжению и прямыми выходами дополнительного и основного RS-триггеров 39 и 22 (40 и 20, 38 и 21) соответственно в порядке чередования фаз других каналов 2 и 3 (3 и 1, 1 и 2) управления по фазному напряжению. Для формирования импульсов синхронизации по линейным напряжениям в каждом канале управления входы одного логического элемента И 50 (52, 54) соединены с инверсным выходом основного RS-триггера 23 (24, 25) этого же канала 4 управления (5, 6) по линейному напряжению и прямыми выходами основного и дополнительного RS-триггеров 24 и 43 (25 и 41, 23 и 42) соответственно в порядке чередования линейных напряжений других каналов 5 и 6 (6 и 4, 4 и 5) управления, по линейному напряжению. Входы другого логического элемента И 51 (53, 55) соединены с инверсным выходом дополнительного RS-триггера 41 (42, 43) этого же канала 4 (5, 6) управления по линейному напряжению и прямыми выходами дополнительного и основного RS-триггеров 42 и 25 (43 и 23, 41 и 24) соответственно в порядке чередования линейных напряжений других каналов 5 и 6 (6 и 7, 4 и 5) управления по линейному напряжению. Аналогично соединены по кольцевой схеме в порядке чередования фазных и линейных напряжений со сдвигом на один канал управления как по линейному так и по фазному напряжениям выходы RS-триггеров с входами логических элементов И 46-49 и 52. . . 55.

Синхронизатор импульсов управления работает следующим образом.

При подаче на входы блоков 8. . . 13 (фиг. 2) индикации нулевого напряжения трехфазной системы синхронизирующих напряжений на их выходах образуются прямоугольные импульсы длительностью до 180 эл. град. Эти импульсы непосредственно подаются на формирователи 32. . . 37. В результате на выходах формирователей появляется последовательность коротких импульсов, которые воздействуют на входы триггеров обоих колец, приводя к изменению их состояний в том случае, если на их R-входах отсутствуют сигналы, запрещающие переключение и которые формируются в результате сложения импульсов с инверсных выходов последующих триггеров данного кольца, S-входы которых связаны с предыдущим фазным или линейным напряжением питающей сети. В результате результирующая длительность запрета по каждому каналу составляет 180 эл. град. Диаграммы напряжений на инверсных выходах RS-триггеров (фиг. 2) представлены на фиг. 4.

Прямоугольные импульсы с прямых и инверсных выходов RS-триггеров (фиг. 2) поступают на входы логических элементов 44. . . 55, выполняющих логическую операцию И. Например, при приходе на логический элемент И 44 (фиг. 3) импульсов с прямого выхода RS-триггера 20 и инверсных выходов RS-триггеров 40 и 21 на выходе логического элемента И 44 формируется импульс синхронизации (вых. 25, фиг. 4), длительность запрета на формирование ложных импульсов при этом составляет 300 эл. град. (от t2 до t3). Аналогично работают и другие каналы синхронизатора.

Отличительными признаками предлагаемого синхронизатора являются каналы управления по числу линейных напряжений, трехвходовые логические элементы И и соответствующие связи между входами логических элементов и выходами основных и дополнительных RS-триггеров каналов управления.

Доказательство существенности отличий. Известен синхронизатор импульсов управления, основанный на формировании импульсов синхронизации по индикации нулевого уровня напряжения как фазного, так и линейного. Известно использование RS-триггеров в формировании импульсов синхронизации, в результате чего обеспечивается запрет на формирование ложных синхроимпульсов в 180 эл. град.

Однако в патентной и научно-технической литературе неизвестно применение логических элементов с подключением их входов к соответствующим выходам RS-триггеров каналов управления по фазным и линейным напряжениям, что дает возможность использовать синхронизатор в непосредственных преобразователях частоты на 150 Гц и повысить его помехоустойчивость за счет расширения запрета на формирование ложных синхронизаторов со 180 до 300 эл. град.

Проведенные испытания синхронизатора импульсов управления в непосредственных преобразователях частоты на 150 Гц показали его работоспособность и высокую помехоустойчивость.

Использование изобретения в непосредственных преобразователях частоты, нашедших применение в качестве источников питания повышенной частоты для электроинструмента, электропривода и стригальных машинок, позволяет получить экономический эффект, обусловленный снижением затрат на ремонт и обслуживание преобразователей, сокращение простоев технологического оборудования за счет повышения надежности работы и уменьшения числа возможных аварийных режимов работы преобразователей. Кроме того, идентичность каналов управления и использование однотипной элементной базы позволяют унифицировать системы управления и повысить технологичность их изготовления. (56) Авторское свидетельство СССР N 725183, кл. Н 02 Р 5/28, 1978.

Авторское свидетельство СССР N 1239797, кл. Н 02 М 1/08, 1984.

Синхронизатор импульсов содержит каналы 1 . . . 3 управления по фазному напряжению, каналы 4 . . . 6 управления по линейному напряжению, блок 7 логических элементов. Каждый из каналов 1 . . . 3 управления по фазному напряжению и каналов 4 . . . 6 управления по линейному напряжению содержит блок индикации нулевого напряжения, выход которого через формирователь подключен к S-входу основного RS-триггера через инвертор и дополнительный формирователь - к S-входу дополнительного RS-триггера. Прямые и инверсные выходы основных RS-триггеров и дополнительных триггеров подключены в определенной совокупности к входам трехвходовых элементов И, формирующих импульсы синхронизации по фазным и линейным напряжениям. 4 ил.

СИНХРОНИЗАТОР ИМПУЛЬСОВ УПРАВЛЕНИЯ ТИРИСТОРНЫМ ПРЕОБРАЗОВАТЕЛЕМ, содержащий каналы управления по числу фазных напряжений, каждый из которых имеет блок индикации нулевого напряжения, выходом через основной формирователь подключенный к S-входу основного RS-триггера и через инвертор и дополнительный формирователь подключенный к S-входу дополнительного RS-триггера, при этом основные RS-триггеры соединены по кольцевой схеме так, что инверсный выход триггера последующего канала соединен с R-входом триггера предыдущего канала, аналогичным образом соединены по кольцевой схеме дополнительные RS-триггеры, а дополнительные R-входы RS-триггеров одного канала подключены к инверсным выходам друг друга, отличающийся тем, что в него введены каналы управления по числу линейных напряжений, каждый из которых аналогичен каналу управления по фазному напряжению, и двенадцать логических элементов 3И по числу тиристоров силового блока, при этом к входам первого логического элемента 3И подключены инверсный и прямой выходы основных RS-триггеров первого и второго каналов управления по фазным напряжениям соответственно и прямой выход дополнительного RS-триггера третьего канала управления по фазному напряжению, к входам второго логического элемента 3И подключены инверсный и прямой выходы дополнительных RS-триггеров соответственно первого и второго каналов управления по фазным напряжениям и прямой выход основного RS-триггера третьего канала управления по фазному напряжению, входы третьего и пятого логических элементов 3И подключены аналогично входам первого логического элемента 3И, а входы четвертого и шестого логических элементов 3И подключены аналогично входам второго логического элемента 3И в порядке чередования фазных напряжений со сдвигом на один канал, аналогичным образом, начиная с четвертого канала управления, подключены выходы каналов управления по линейным напряжениям к входам седьмого - двенадцатого логических элементов 3И в порядке чередования линейных напряжений.

Авторы

Даты

1994-01-30—Публикация

1991-11-04—Подача