полнительного двухвходового элемента И соединен с выходом источника сигнала разрешающего формирование отрицательного полупериода выходного напряжения, а второй вход второго дополнительного .лвухвходового элемента И соединен с выходом источника сигнала, разрешающего формирование положительного полупериода выходного напряжения, выход первого логического элв мента ЗАПРЕТ подключен к второму входу первого элемента ИЛИ, выход которого соединен с 5 -входом RS-триггера, а выход второго логического элемента ЗАПРЕТ подключен к второму входу второго элемента ИЛИ, выход которого соединен с Й-входом RS-триггера, причем прямой вход первого логического элемента ЗАПРЕТ подключен к выходу первого дополнительного двухвходового элемента И, а прямой вход второго логического элемента ЗАПРЕТ подключен к выходу второго дополнительного двухвходового элемента И, при этом инверсный вход первого логического элемента ЗАПРЕТ соединен с выходом первого элемента И, а инверсный вход второго логического элемента ЗАПРЕТ - с выходом второго элемента И, причем длительность импульса на выходе формирователей определяют как

(.тах + 9(,|,,).,

где Kj -- коэффициент запаса по длительности, К 5. 1,25;

вклтсмх выклтах соответственно

максимальное значение времени включения и времени выключения наиболее инерционного тиристора в силовой цепи циклоконвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое переключающее устройство для раздельного управления группами непосредственного преобразователя частоты | 1985 |

|

SU1319201A1 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 2005 |

|

RU2297096C1 |

| Устройство для автоматического счета подвижных объектов | 1975 |

|

SU658023A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1986 |

|

SU1374229A1 |

| Устройство для контроля последовательности импульсов | 1980 |

|

SU930630A1 |

| Регенератор двоичных сигналов | 1984 |

|

SU1185630A1 |

| Двухканальное устройство для разделения совпадающих по времени импульсов | 1979 |

|

SU783970A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU687578A1 |

| Цифровое устройство для управления вентильным преобразователем | 1984 |

|

SU1239806A1 |

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

ЛОГИЧЕСКОЕ ПЕРЁКЛЮЧАНЩЁЕ УСТРОЙСТВО ДЛЯ РАЗДЕЛЬНОГО УПРАВЛЕНИЯ ГРУППАМИ ТИРЙСТОРНОГО ЦИКЛОКОНВЕРТОРА, содержащее два элемента задержки, входы которых соединены с выходами &-триггера, 5 -вход которого подключен к выходу первого элемента ИЛИ, а R -вход - к выходу второго элемента ИЛИ первый вход первого элемента ИЛИ соединен с выходом первого двухвходового элемента И, .а первый вход второго элемента ИЛИ соединен с выходом второго двухвходового элемента И, первый вход первого элемента И подключен через первый элемент НЕ к источнику сигнала, разрешающего фондирование положительного полупериода выходного напряжения, а первый вход второго элемента И подключен через второй элемент НЕк источнику сигнала, разрешающего форячирование отрицательного полупериода выходного напряжения, вторые входы каждого элемента И соединены между собой V через третий элемент НЕ подключены к выходу датчика состояния проводимости вентилей, отличавю щ е е с я тем, что,с целью повышения помехоустойчивости и надежности раздельного управления, оно снабжено двумя логическими элементами ЗАПРЕТ, двумя формирователями импульсо 7 Йвумя дополнительными элементами И, двумя дополнительнБми элементами НЕ и двумя трехвходовыми элементами И, причем вьоход первого трехвходового элемента И предназначен для подключения разрешающего формирование выходного тока отрицательного направле ния входа блока управления, выход второго трехвходового элемента И предназначен для подключения разрешакицего Формирование выходного тока положительного направления входа блока управления, первый вход первого трехвходового элемента И соединен с выходом элемента задержки, подклю- Щ ченного к прямому выходу триггера, а (Л первый -вход второго, трехвходового элемента И соединен с выходом элемента задержки, -подключенного к инверсному выходу RS-триггера, вторые входы каждого из трехвходовых элементов И соединены между собой и подключены к выходу первого дополнительного элемента НЕ, третьи входы каяодого из трехвходовых элементов И соединены между собой и подключены к выходу второго дополнительного элемента НЕ, при этом вход первого до Р1 полнительного элемента НЕ соединен с выходом первого дополнительного двухвходового элемента И, а Bxojct второго дополнительного элемента НЕ соединен с выходом второго дополнительного двухвходового элемента и, первый вход первого дополйительного двухвходового элемента И соединен с выходом первого формирователя импульса длительностью Т, подключенного к пргямому выходу,RS-триггера,а первый вход второго дополнительного двухвходового элемента И соединен с выходом второго формирователя импульса.подключенного к инверсному выходу F -TPHI гера, причем второй вход первого д6

Изобретение относится к электротехнике и может быть использовано для раздельного управления циклоконверторами.

Известно устройство для раздельного управления преобразователем, содержащее элементы И, подключенные к входам соответствующих триггеров, выходы которых через элемент ИЛИ подключены к входам элементов И 1 .

Недостатком данного устройства является его невысокая надежность.

Наиболее близким к предлагаемому является устройство раздельного управления группами тиристорного циклоконвертора, состоящее из трех входных логических инверторов, двух входных логических элементов И, двух входных логических элементов ИЛИ, RS-триггера и двух элементов задержки, входы которых соединены с выходами RS-триггера, дтричем S-вход триггера подключен к выходу первого входного элемента ИЛИ, а R-вход триггера подключен к выходу второго входного элемента ИЛИ, первый вход первого входного элемента ИЛИ соединен с вьоходом первого входного двухвходового логического элемента И, а первый вход второго входного элемента ИЛИ соединен с выходом второго входного двухвходового логического элемента И, при этом первый вход первого элемента И подключен через первый входной логический инвертор к источнику сигнала, разрешающего формирование положительного полупериода выходного напряжения, а первый вход

второго элемента И подключен через второй входной логический инвертор к источнику сигнала, разрешающего формирование отрицательного полупериода выходного напряжения, причем вторые входы каждого входного элемента И соединены между собой и через третий входной логический инвертор подключены к выходу датчика состояния проводимости вентилей 2.

Недостатками известного устройства являются низкая помехоустойчивость и невысокая надежность,

Цель изобретения - повышение помехоустойчивости и надежность,

Поставленная цель достигается тем, что логическое переключающее устройство для раздельного управления группами тиристорного циклоконвертора, содержащее два элемента задержки, входы которых соединены с выходами RS-триггера, S-вход которого подключен к выходу первого элемента ИЛИ, а R-в,xoд - к выходу второго элемента ИЛИ, первый вход первого элемента ИЛИ соединен с выходом первого двухзходового элемента И, а первый вход второго элемента ИЛИ соединен с выходом второго двухвходового элемента И, первый вход первого элемента И подключен через первый элемент ;НВ к источнику сигнала, разрешающего формирование положительного полупериода выходного напряжения, а первый вход второго элемента И подключен че5,рез второй элемент НЕ к источнику сигнала, разрешающего формирование отрицательного полупериода выходного

напряжения, вторые входы каждого элемента И соединены между собой и чере третий элемент НЕ подключены к выходу датчика состояния проводимости вентилей, снабжено двумя логическими элементами ЗАПРЕТ, двумя формирователями импульсов, двумя дополнительными двухвходовыми элементами И, двумя дополнительными элементами НЕ и двумя трехвходовыми элементами И, причем выход первого трехвходового элемента И предназначен для подключения разрешающего формирование выходного тока отрицательного направления входа.блока управления, выход второго трехвходового элемента И предназначен для подключения разрешающего формирование выходного тока положительного направления входа блока управления, первый вход первого трехвходового элемента И соединен с выходом элемента задержки, подключенного к прямому выходу триггера,а первый вход второго трехвходового элемента И соединен с выходом элемента задержки,подключенного к инверсно му выходу RS-триггера,вторые входы каждого из трехвходовых элементов И соединены между собой и подключены к выходу первого дополнительного элел}ета НЕ,третьи входы каждого из трехвхо довых элементов И соединены между собой и подключены к выходу второго дополнительного элемента НЕ,при этом вход первого дополнительного элемент НЕ соединен с выходом первого дополнтельного двухвходового элемента И, а вход второго дополнительного элемента НЕ соединен с выходом второго дополнительного двухвходового элемента И, первый ВХОД-первого дополнительного двухвходового элемента И соединен с ВЕЛХОДОМ первого формирователя импульса длительностью Т, подключенного к прямому выходу RS-триггера, а первый вход второго дополнительного двухвходового элемента И соединен с выходом второго формирователя импульса, подключенного к инверсному выходу RS-триггера, причем второй вход первого дополнительного двухвходового элемента И соединен с выходом источника сигнала, разрешающего формирование отрицательного полупериода выходного напряжения, а второй вход второго дополнительного двухвходового элемента И соединен с выходом источника сигнала, разрешающего формирование положительного, полупериода выходного напряжения, выход первого логического элемента ЗАПРЕТ подключен к второму входу перво1ГО элемента ИДИ, выход которого соещинен с S-входом RS-триггера, а выход второго логического элемента ЗАПРЕТ подключен к второму входу второго элемента ИЛИ, выход которого соединен с R-входом RS-триггера, причем прямой вход первого логического элемента ЗАПРЕТ подключен к выходу первого дополнительного двухвходового элемента И, а прямой вход второго логического элемента ЗАПРЕТ подключен к выходу второго дополнительного двухвходового элемента и, при этом инверсный вход первого логического элемента ЗАПРЕТ соединен с выходом первого элемента И, а инверсный вход второго логического элемента ЗАПРЕТ соединен с выходом второго элемента И, прячем длительность импульса на выходе формирователей определяют как

.таг( выкл.гпаXI;

где Kg - коэффициент запаса по длительности, Кй$.1,25;

fiwmax WAmax соответственно

максимальное значение времени включения и времени выключения наиболее инерционного тиристора ,в силовой цепи циклоконвертора.

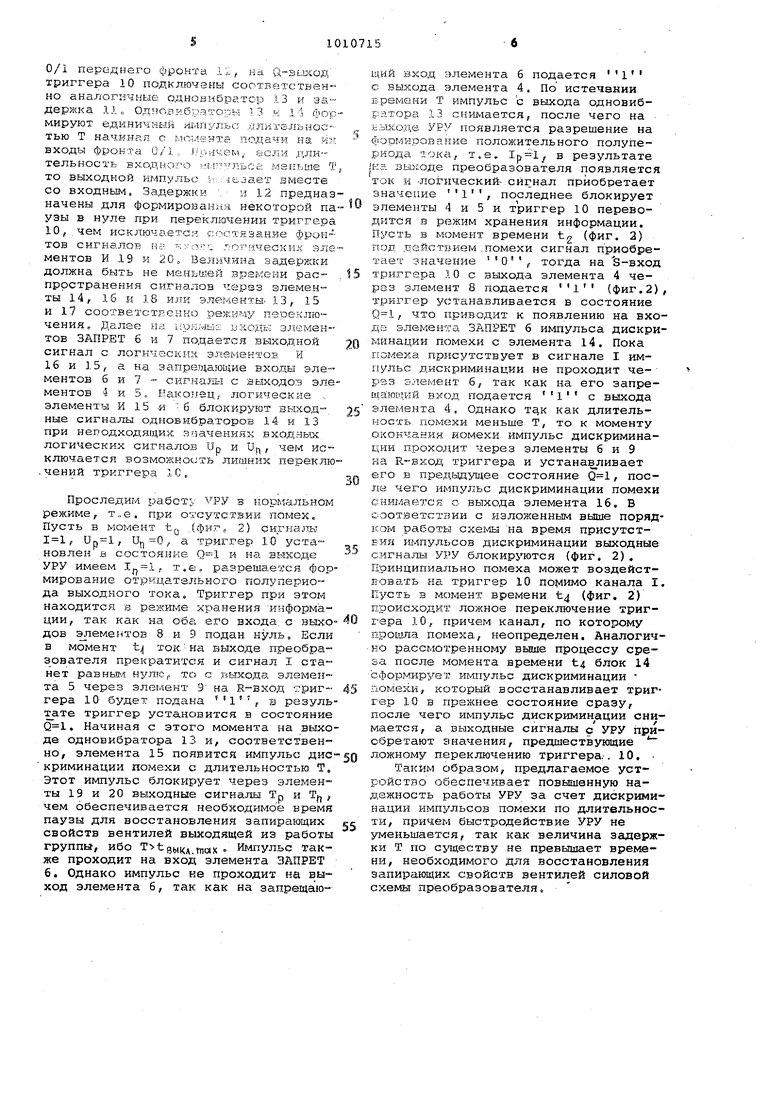

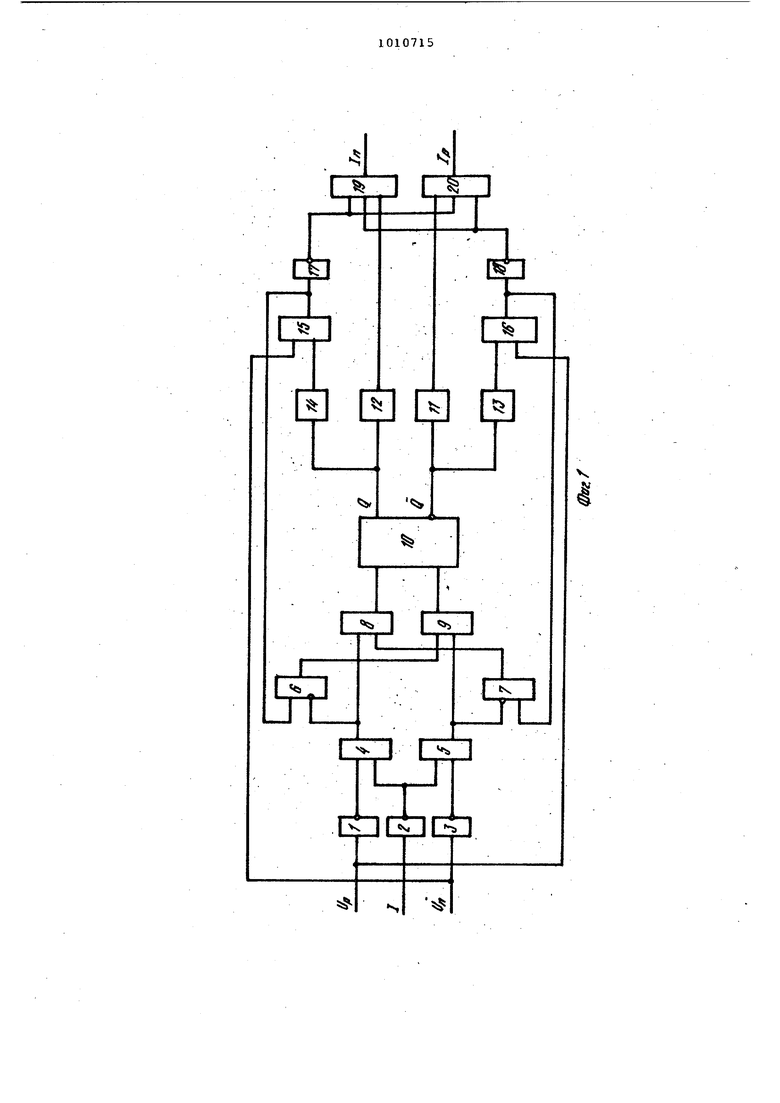

На фиг. 1 приведена схема устройства управления циклоконнертором; на фиг. 2 - временные диаграммы, пояснякндее его работу.

Устройство содержит элементы ИЛИ 1-3, элементы И 4 и 5, элементы ЗАПРЕТ 6 и 7, элементы ИЛИ 8 и 9, триггер 10, элементы 11 и 12 задержки, одновибраторы 13 и 14, подключенные к входам элементов И 15 и 16, элементы ИЛИ 17 и 18. и элементы И 19 и 20.

Пусть Up и U|., - логические сигналы, разрешающие формирование на выходе данной фазы циклокондертора соответственно положительную и отрицательную полуволны выходного напряжения; I - логический сигнал о наличии тока в этой же выходной фазе преобразователя; IP и ITI - выходные логические сигналы устройства раздельного управления (УРУ), раэрешаквдие формирование соответственно положительной или отрицательной полуволны выходного тока данной фазы.

Основным -Элементом УРУ является RS-триггер 10, каждый из входов которого соединен с выходами логических элементов ИЛИ 8 и 9 собственно. На одни из входов элементов 8 и 9 подключены выходы элементов ЗАПРЕТ б и 7, а на другие входы -: выходы логических элементов И 4 и 5. На входы логического элемента 4 подается инверсия сигналов Up и I у а на входы логического элемента 5 - инверсия сигналов и,д и I. На Q-выход триггера 10 подключен одновибратор 14, запускаемый фронтом 0/1 и задержка 0/1 переднего Фронта 11 на Q-stoxoA триггера 10 подключены соотБеаственно аналогичные однонибрато : 13 и задержка и., Одновибраторы 13 к 1Л фор мируют единичный ш-1лульо ллитальностью Т начиная с .момента подачи на п входы фронта и/1, , если длительность входно: о л: лг пьсе. мзыьше Т то выходной импульс г&зает вместе со входным. Задержки , и 12 предназ начены для формирования некоторой па узы в нуле при переключении триггера 10,, чем исключается. с:г1стязан.ие фронтов сигналов нг Г; о г ячеек их эле ментов И 19 и 20 о Величина задержки должна быть не меньшей вракени распррстранения с.игналов черзз элементы 14 , и 18 или элементы. 13, 15 и 1 соответстЕенно реж.иму п-эоеклю чениЯс Далее нд lajHivjbas икодь ; элементов ЗАПРЕТ б и 7 подает1-::я выходной сигнал с логичес11и.н элементов И 16 и 15, а на запрещающие входы элементов 6 и 7 - сигмальа с выходов эле ментов 4 и 5, Како1.тец; логические .. элементы И 15 .и 16 блоккруЕот вы:х:одные сигналы олиовибраторов 14 и 13 при неподкодящи.к з;}аченияк вход.ньтх логических сигналов Up и U.f, , чем ис ключается возможность лишних переклю ,чений триггера 1C. Проследим работ:;. v.py 3 нормальном режиме, т„е. при отсугствии помех. Пусть в момент tQ .(фиг, 2) сигналы f , Ufi 0 . а триггер 10 установлен .а состояние и на выходе УРУ имеем . т.е. разрешается фор мирование отрицательного полупериода выходного тока. Триггер при этом находится в режиме хранения информации, так как на o6cL его входа, с выхо дов элементов 8 и 9 подан нуль. Если в момент t ток.на выходе преобра™ зователя прекратится и сигнал I станет равньм нулю,, то с рнхода элемента 5 через элемент 9 на R-вход триггера 10 будет подана , в резуль гате триггер установится в состояние . Начиная с этого момента на выхо де одновибратора 13 и, соответственно, элемента 15 появится импульс дис криминации помехи с длительностью Т. Этот импульс блокирует через элементы 19 и 20 выходные сигналы Тр и Tj , чем обеспечивается необходимЬе время паузы для восстановления запирающих свойств вентилей выходящей из работы ГРУППЫ , ибо T tgbiKA.motx Импульс также проходит на вход элемента ЗАПРЕТ б. Однако импульс ке проходит на выход элемента 6, так как на запрещающий вход элемента б подается с выхода элемента 4, По истечании времени Т импульс с выхода одновиб: :атора 1.3 снимается, после чего на н.ык.оде- УРУ появляется разрешение на спормировамие положительного полупеIp l в результате риода тока, т.« KS, вг:Есоде преобразователя появляется ток и -логический- сигнал приобретает значение , последнее блокирует элементы 4 и 5 и триггер 10 переводится в режим хранения информации. Пусть в момент времени tg (фиг. 2) под действием .помехи сигнал приобретает значение О, тогда на S-вход триггера лО с выхода элемента 4 через элемент 8 подается (фиг.2), триггер устанавливается в состояние , что приводит к появлению на входе элемента ЗАПРЕТ 6 импульса дискриминации помехи с элемента 14. Пока помеха присутствует в сигнале I импульс дискриминации не проходит че- раз элемент б, так как на его запрешаюикй вход подается с выхода э.лемента 4, Однако как длительность помехи меньше Т, то к моменту окончания номехи импульс дискриминац.ии проходит через элементы 6 и 9 на Е--вход триггера и устанав ливает его в предыду11.(ее состояние , после чего импульс дискриминации помехи снимается о выхода элемента 16, В соответствии с изложенным выше порядком работы схемы на время присутствия импульсов дискриминации выходные сигналы УРУ блокируются (фиг. 2). ЕСрикципиально помеха может воздействовать на триггер 10 канала I. Пусть в момент времени t (фиг. 2) происходит ложное переключение триггера 10, причем канал, по которому прошла помеха, неопределен. Аналогично рассмотренному выше процессу среза после момента времени t4 блок 14 сформирует импульс дискриминации помехи, который восстанавливает триггер 10 в прежнее состояние сразу, после чего импульс дискриминации снимается, а выходные сигналы с УРУ приобретают значения, предшествующие ложному переключению триггера/. 10. Таким образом, предлагаемое устройство обеспечивает повышенную надежность работы УРУ за счет дискриминации импульсов помехи по длительности, причем быстродействие УРУ не уменьшается, так как величина задержки Т по c I ecтвy не преввлшает времени, необходимого для восстановления запирающих свойств вентилей силовой схемы преобразователя.

ГлП I

1-J

L2J

L5J

U П5

L L5

I у I I «S. Jlj-s

s

t3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Барский В.А | |||

| Раздельное управление реверсивными тиристорными преобразователями, Энергия, 1973, с | |||

| Механический грохот | 1922 |

|

SU41A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Полупроводниковые выпрямители, Под ред | |||

| Ф.И.Ковалева, М., Энергия ,1978, с.243. | |||

Авторы

Даты

1983-04-07—Публикация

1980-07-04—Подача