Изобретение относится к технике формирования цифровых унитарных сигналов, в частности к устройствам дешифрации.

Известен дешифратор, содержащий входной регистр, декодер и устройство для контроля дешифратора [1] .

Недостаток этого дешифратора состоит в сложности его схемы.

Наиболее близким к предлагаемому дешифратору является устройство [2] , содержащее входной регистр, информационный вход которого является входом дешифратора, причем выходы первого - n-го разрядов входного регистра (n - разрядность входного кода) соединены с соответствующими информационными входами декодера, выходы которого являются информационными выходами дешифратора.

Недостаток этого устройства состоит в том, что при возникновении сбоев в передающем или приемном устройстве дешифратор формирует неправильный выходной сигнал.

Цель изобретения - повышение достоверности дешифратора.

Сущность изобретения состоит в том, что в дешифратор, содержащий входной регистр, информационный вход которого является входом дешифратора, причем выходы первого - n-го разрядов входного регистра (n - разрядность входного кода) соединены с соответствующими информационными входами декодера, выходы которого являются информационными выходами дешифратора, введены элемент ИМПЛИКАЦИЯ и элементы задержки, при этом входной регистр содержит дополнительно два разряда на установку кода "01", выходы которых соединены соответственно с первым и вторым входами элемента ИМПЛИКАЦИЯ, выход которого соединен через первый элемент задержки с входом блокировки декодера и входом второго элемента задержки, выход которого является контрольным выходом дешифратора.

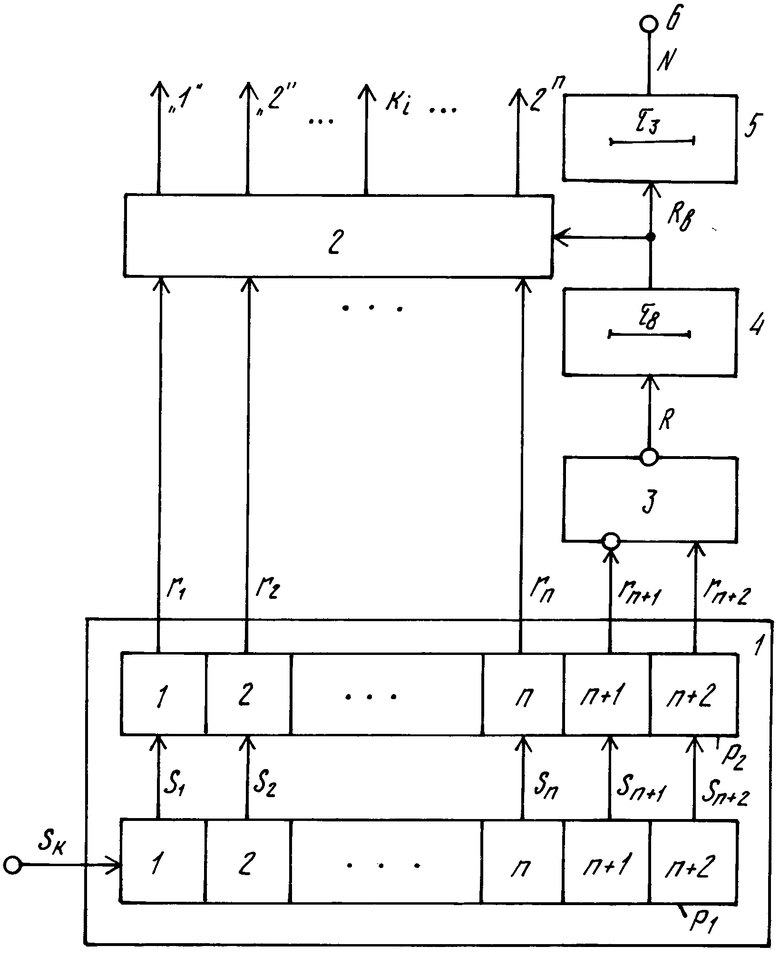

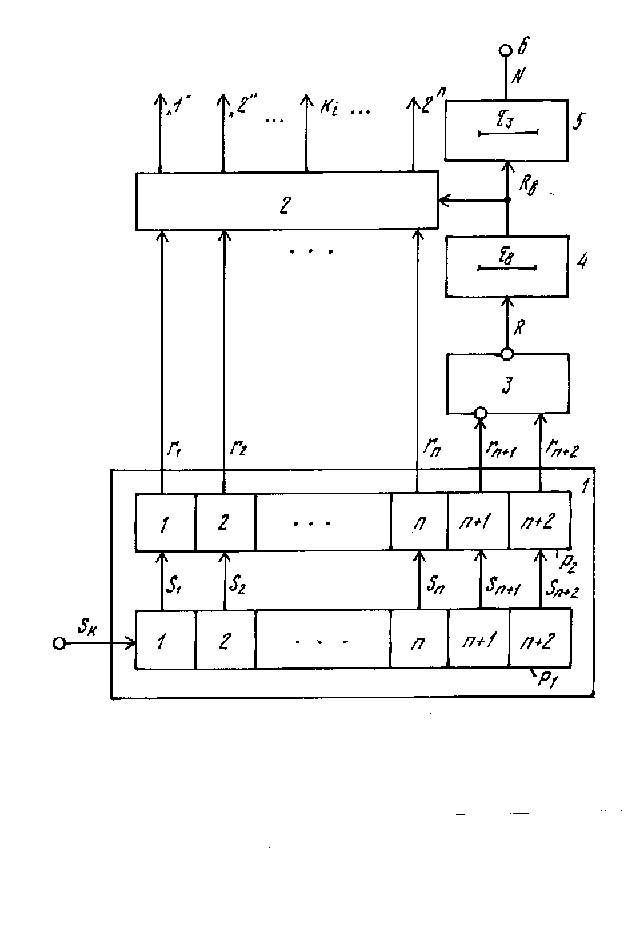

На чертеже представлена схема дешифратора.

Выходы первого - n-го разрядов входного регистра 1 соединены с соответствующими входами декодера 2, выход (n + 1)-го разряда соединен с первым входом элемента ИМПЛИКАЦИЯ 3, второй вход которого соединен с выходом (n + 2)-го разряда. Выход элемента ИМПЛИКАЦИЯ подключен к входу первого элемента 4 задержки, выход которого соединен с входом блокировки декодера 2 и входом второго элемента 5 задержки, выход которого является контрольным выходом 6 дешифратора.

Дешифратор работает следующим образом.

Пусть на вход входного регистра 1 поступает управляющее слово SК с элементами кода Sj (j = 1,2, . . . , n + 2), где n - число разрядов входного регистра, преобразуемых в выходные сигналы). Выходные сигналы входного регистра 1 rl (l = 1,2, . . . , n) поступают на соответствующие входы декодера 2, на выходе которого формируются сигналы Ki (i = 1,2, . . . , 2n). Выходные сигналы rn+1 и rn+2 входного регистра 1 подаются на первый и второй входы элемента ИМПЛИКАЦИЯ 3.

Пусть управляющее слово SК формируется таким образом, что его элементы кода Sn+1 = 0 и Sn+2 = 1. Тогда при правильной работе передающего и приемного устройств rn+1 = 0 и rn+2 = 1. В это случае выходной сигнал R элемента ИМПЛИКАЦИЯ 3 равен нулю и выходной сигнал Rв первого элемента 4 задержки также равен нулю. Если R = 0, то выходные сигналы Ki декодера 2 формируются согласно входному коду с элементами кода rl. Если сигнал rn+1 = 1 или rn+2 = 0, то сигнал R = 1. Этот сигнал через первый элемент 4 задержки на выключение блокирует выходные сигналы Ki декодера 2 и запускает второй элемент 5 задержки, который по истечении времени τ3 формирует на своем выходе 6 сигнал неисправности N = 1 (τ3 - время задержки элемента 5). Таким образом, при правильной работе (rn+2 = 1, rn+1 = 0, сигналы R = 0, Rв = 0, N = 0) отсутствует блокировка выходных сигналов Ki. При неправильной работе (rn+1 = 1 или rn+2 = 0, сигналы R = 1, Rв = 1, N = 1) осуществляется блокировка выходных сигналов Ki и формируется контрольный сигнал неисправности N = 1.

Рассмотрим работу дешифратора при возможных отказах передающего или приемного устройства входного регистра.

Пусть отказало передающее или приемное устройство таким образом, что входной регистр 1 все элементы кода Sj воспринимает в виде Sj = 1. В этом случае Sj = rj = 1, элемент ИМПЛИКАЦИЯ 3 формирует сигнал R = 1, первый элемент 4 задержки формирует сигнал Rв = 1, а второй элемент 5 задержки формирует контрольный сигнал неисправности N = 1. Одновременно сигнал Rв = 1 осуществляет блокировку выходных сигналов Ki декодера 2.

Пусть отказало передающее или приемное устройство таким образом, что входной регистр 1 воспринимает элементы кода в виде Sj = 0. В этом случае Sj = rj = 0, сигналы R = 1, Rв = 1, N = 1. Сигнал Rв = 1 осуществляет блокировку выходных сигналов Ki, а второй элемент задержки формирует контрольный сигнал неисправности N = 1.

Передача управляющего слова SК производится в условиях действиях помех. При это формирование Sj = 0 или Sj = 1 равновероятно и не зависит от передаваемого кода. В этом случае вероятность записи информации Sj = 0 или Sj = 1 равна

Pj = 0,5. (1)

Вероятность записи Р01 кода 01 в (n + 1)-й и (n + 2)-й разряды входного регистра 1 определяется равенство

Р01 = Pj. Pj = 0,25. (2)

Случайное событие считают достоверны, если вероятность его появления Рд > 0,9. В рассматриваемом случае вероятность формирования достоверного сигнала R = 1, характеризующего наличие сбоя при передаче информации, равна

PR = 1 - Р01 = 0,75. (3)

Определяют вероятность записи кода 01 в (n + 1)-й и (n + 2)-й разряды входного регистра 1 двумя управляющими словами SК, следующими друг за другом. Эта вероятность равна

Р011 = Р012 = 0,0625. (4)

Если время передачи одного управляющего слова равно Тс, то при осуществлении задержки заднего фронта сигнала Rв = 1 на время 2Тс вероятность формирования сигнала Rв = 0 (необнаружение сбоев при передаче информации) равна Р011. Тогда при времени задержки первого элемента 4 задержки τв = 2Тс вероятность формирования достоверных сигналов Rв = 1 и N = 1 равна

PN = 1 - Р01' = 0,9375 > Рд. (5)

В рассматриваемых условиях действия помех сигнал Rв = 1 существует непрерывно в течение всего времени до тех пор, пока при передаче трех следующих друг за другом управляющих слов элементы кода Sn+1 = 0 и Sn+2 = 1. Вероятность такого события равна

Р01" = Р013 = 0,016. (6)

Иначе говоря, пребывание сигнала Rв = 1 возможно один раз в течение времени передачи 64 управляющих слов, что непосредственно следует из выражения (6). Если задержку τ3 второго элемента 5 второго элемента 5 задержки выбрать в пределах

5Тс ≅τ3≅ 63Тс,

а задержка τв = 2Тс, то достоверная блокировка выходных сигналов Ki и сигнал неисправности N = 1 формируются с вероятностью PN = 0,9375.

При единичных случайных сбоях в передаче управляющих слов Sк время существования сигнала Rв = 1 меньше 5Тс. В этом случае производится блокировка выходных сигналов Ki, формирование контрольного сигнала неисправности не осуществляется.

Оценивают достоверность выдачи выходных сигналов Ki известным дешифратором, Считают, что содержание управляющего слова SК может быть произвольным, а правильный выходной сигнал должен быть единственным. Вероятность выдачи правильного сигнала Ki известным устройством равна

P′= (1/2)n

Например, при n = 3, P' = 0,125, а вероятность выдачи правильного сигнала рассматриваемым дешифратором определяется выражением (5) и равна 0,9373. (56) 1. Авторское свидетельство СССР N 1494006, кл. G 06 F 11/00, 1986.

2. Клингман. Проектирование специализированных микропроцессорных систем. М. : Мир, 1985, с. 31, рис. 1.19.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ДИСТАНЦИОННОГО УПРАВЛЕНИЯ ОБЪЕКТАМИ | 1990 |

|

RU2006955C1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 1990 |

|

RU2040040C1 |

| ЦИФРОВАЯ СЛЕДЯЩАЯ СИСТЕМА | 1990 |

|

RU2037869C1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 1990 |

|

RU2037873C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ПЕРИОДНО-МОДУЛИРОВАННОГО ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ПАРАЛЛЕЛЬНЫЙ КОД И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2032270C1 |

| ПУСКОВОЙ АГРЕГАТ | 1991 |

|

RU2010989C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОБЪЕКТОМ | 1991 |

|

RU2006940C1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ ПО ДВУХПРОВОДНОЙ ЛИНИИ СВЯЗИ | 1991 |

|

RU2022369C1 |

| РЕДУКТОР ДЛЯ ЭЛЕКТРОПРИВОДА | 1992 |

|

RU2039897C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ФАЗЫ | 1992 |

|

RU2028727C1 |

Изобретение относится к технике формирования цифровых унитарных сигналов, в частности к устройствам дешифрации. Дешифратор позволяет повысить достоверность выдаваемых сигналов. Входной регистр 1 содержит n разрядов, выходы которых соединены с соответствующими информационными входами декодера 2, и два дополнительных разряда, выходы которых соединены с первым и вторым входами элемента ИМПЛИКАЦИЯ 3. Выход последнего подключен к входу первого элемента 4 задержки, выход которого соединен с входом блокировки декодера 2 и входом второго элемента 5 задержки, выход которого является контрольным выходом дешифратора. Такое соединение элементов повышает достоверность выходных информационных сигналов дешифратора за счет блокировки декодера 2. 1 ил.

ДЕШИФРАТОР, содержащий входной регистр, информационный вход которого является входом дешифратора, выходы первого - n-го разрядов входного регистра (n - разрядность входного кода) соединены с соответствующими информационными входами декодера, выходы которого являются информационными выходами дешифратора, отличающийся тем, что, с целью повышения достоверности дешифратора, в него введены элемент ИМПЛИКАЦИЯ и элементы задержки, входной регистр содержит дополнительно два разряда на установку кода "01", выходы которых соединены соответственно с первым и вторым входами элемента ИМПЛИКАЦИЯ, выход которого соединен через первый элемент задержки с входом блокировки декодера и входом второго элемента задержки, выход которого является контрольным выходом дешифратора.

Авторы

Даты

1994-01-30—Публикация

1990-08-08—Подача