Изобретение относится к автоматике и вычислительной технике и может быть использовано для работы в резервированных устройствах.

Известно устройство для мажоритарного выбора сигналов, содержащее в каждом канале первый мажоритарный элемент, информационные выходы которого подключены к выходам регистров, а выход к исполнительным механизмам, информационные входы устройства соединены с информационными D-входами регистров, контрольные R-входы которых подключены к входам контроля устройства, элементы ИЛИ, второй мажоритарный элемент, информационные входы которого подключены к соответствующим контрольным R-входам регистров, выход его соединен с первыми входами двух элементов ИЛИ, другие входы которых подключены соответственно к первому и третьему входам второго мажоритарного элемента, а выходы к дополнительным управляющим входам первого мажоритарного элемента.

Недостатком известного устройства является невысокая достоверность формирования выходных сигналов.

Целью изобретения является повышение достоверности формирования выходных сигналов.

Это достигается тем, что в устройство для мажоритарного выбора сигналов, содержащее первый и второй элементы ИЛИ, первый, второй и третий (n+1) разрядные входные регистры, первые n выходов каждого из которых подключены к соответствующим входам группы из n-мажоритарных элементов, при этом первые n разрядов каждого из входных регистров являются информационными, а (n+1) разряд является контрольным, в него дополнительно введены первая, вторая и третья группы из n элементов РАВНОЗНАЧНОСТЬ каждая, первый, второй и третий элементы И на n входов каждый, четвертый, пятый и шестой элементы И на два входа каждый, третий элемент ИЛИ, элемент задержки и n-канальный коммутатор, при этом соответствующие n выходы первого, второго и третьего входных регистров соединены с соответствующей парой входов элементов РАВНОЗНАЧНОСТЬ первой, второй и третьей групп, выходы каждой из которых соединены соответственно с входами первого, второго и третьего элементов И, выходы которых подключены к входам первого элемента ИЛИ, прямой выход которого соединен с управляющим входом n-канального коммутатора, инверсный выход первого элемента ИЛИ соединен с первым входом второго элемента ИЛИ, выход которого подключен к входу элемента задержки, второй вход второго элемента ИЛИ соединен с инверсным выходом третьего элемента ИЛИ, первый, второй и третий входы которого подключены к выходам соответственно четвертого, пятого и шестого элементов И, первый и второй входы каждого из которых соединены попарно с выходом (n+1) разряда соответственно первого, второго и третьего его входных регистров, выходы n-мажоритарных элементов соединены соответственно с входами n-канального коммутатора, причем выход элемента задержки является выходом сигнала неисправности, а информация, записываемая в (n+1) разряд каждого регистра, соответствует единичному состоянию.

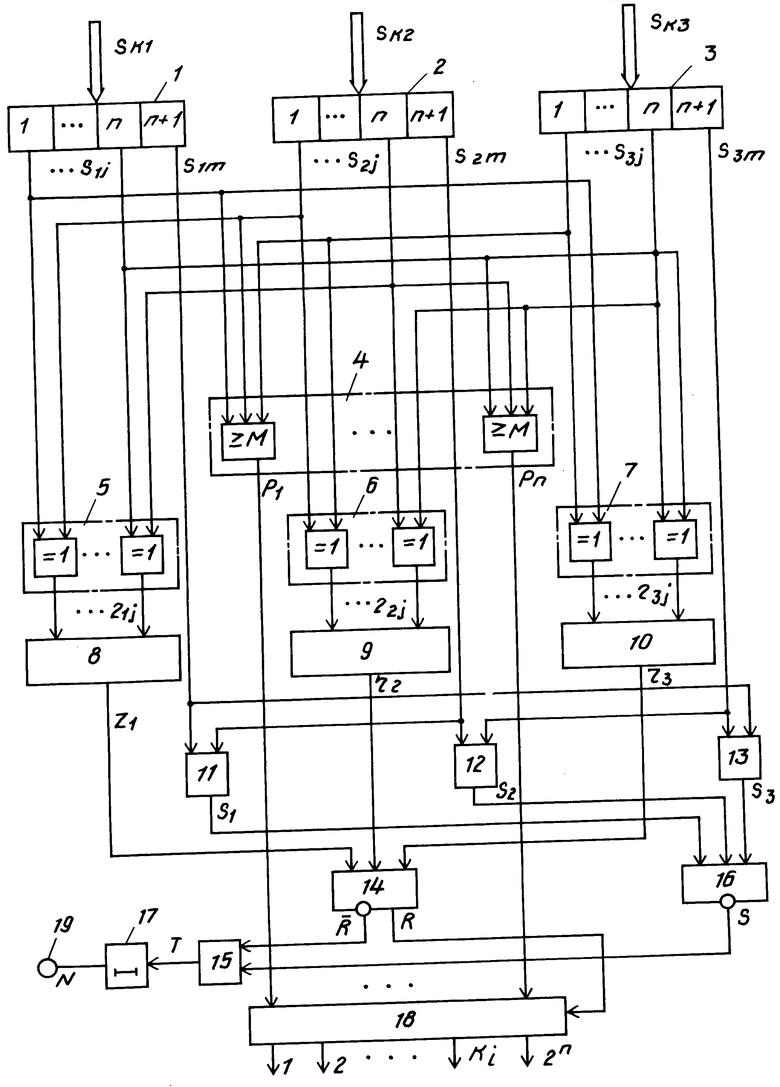

На чертеже представлена схема устройства для мажоритарного выбора сигналов.

Устройство состоит из первого 1, второго 2 и третьего 3 регистров, соединенных с соответствующими входами группы 4 из n-мажоритарных элементов и соответствующими входами первой 5, второй 6 и третьей 7 групп из n элементов РАВНОЗНАЧНОСТЬ, выходы каждой из которых соединены с соответствующими входами первого 8, второго 9 и третьего 10 элементов И на n входов соответственно, выходы которых подключены к входам первого элемента ИЛИ 14. Выходы (n+1) разряда первого 1, второго 2 и третьего 3 регистра попарно соединены с соответствующими входами четвертого 11, пятого 12 и шестого 13 элементов И, выходы каждого из которых соединены с соответствующими входами третьего элемента ИЛИ 16. Инверсный выход первого элемента ИЛИ 14 соединен с первым входом второго элемента ИЛИ 15, второй вход которого подключен к инверсному выходу третьего элемента ИЛИ 16, а выход элемента ИЛИ 15 соединен с входом элемента 17 задержки, выход которого является выходом 19 устройства "сигнал неисправности". Прямой выход первого элемента ИЛИ 14 соединен с управляющим входом коммутатора 18, входы которого подключены к соответствующим выходам группы 4 мажоритарных элементов.

Устройство для мажоритарного выбора сигналов работает следующим образом.

Пусть на вход первого регистра 1 поступает управляющее слово Sk1 с элементами кода S1j (j 1,2.n) и S1m, на вход второго регистра 2 поступает управляющее слово Sk2 с элементами кода S2j и S2m и на вход третьего регистра 3 поступает управляющее слово Sk3 с элементами кода S3j и S3m (m n+1).

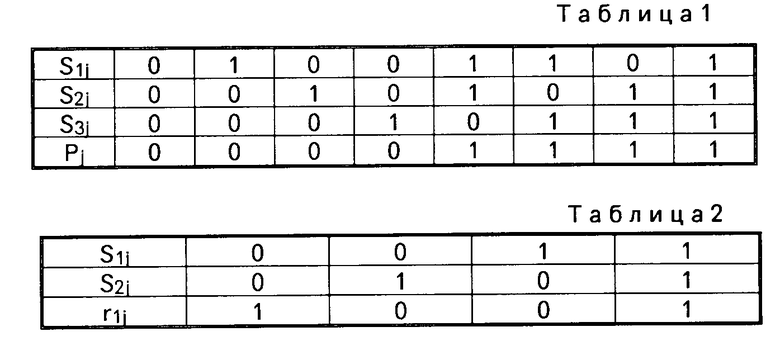

Выходной сигнал Рj на выходе любого мажоритарного элемента из группы 4 формируется согласно табл. 1.

Выходной сигнал r1j (r2j или rзj любого элемента РАВНОЗНАЧНОСТЬ первой 5, второй 6 или третьей 7 групп соответственно формируется согласно табл.2.

Выходной сигнал r1 первого элемента И 8 на n входов равен 1, если S1j S2j, выходной сигнал r2 второго элемента И 9 на n входом равен 1, если S2j S3j, выходной сигнал r3 третьего элемента И 10 на n входов равен 1, если Sзj S1j. Cигналы r1, r2 и r3 будут равны нулю, если указанные равенства не выполняются хотя бы при одном значении j. Запишем сказанное в виде

r1 1, если S1j S2j, j 1, 2,n (1)

r1=0, если S1j≠S2j, j=l, l∈[1,2,n]

(2)

r2 1, если S2j S3j (3)

r2 0, если S2j ≠ S3j, j l (4)

r3 1, если S3j S1j (5)

r3 0, если S3j ≠ S1j, j l (6)

Выходной сигнал Ki (i 1,2.2n) коммутатора 18 формируется, если сигнал R с прямого выхода первого элемента ИЛИ 14 равен 1. Если R 0, то и выходной сигнал Ki= 0. Это достигается подачей сигнала R на вход блокировки выходных сигналов коммутатора 18.

Сигнал R 1, если один из сигналов r1, r2 или r3 равен 1 (выполняется одно из равенств 1, 3 или 5, что соответствует равенству любых двух из трех управляющих слов с элементами кода S1j, S2j и S3j.

Если R 0 (выполняются одновременно равенства 2, 4 и 6), то выходной сигнал коммутатора 18 Ki 0. Другими словами Ki 0, если управляющие слова с элементами кода S1j, S2j и S3j отличаются друг от друга.

Выходной сигнал Ki коммутатора 18 формируется следующим образом. Сигналы S1j первого регистра 1, S2j второго регистра 2, S3j третьего регистра 3 подаются на соответствующие входы мажоритарных элементов группы 4. Выходные сигналы Рj этих элементов поступают на входы коммутатора 18, образуя управляющее слово Рk, элементы которого Рjформируются в соответствии с табл.1. Коммутатор 18 преобразует управляющее слово Рk в выходные сигналы Ki ≠ 0, если выходной сигнал первого элемента ИЛИ 14 R 1. Если R 0, то Ki 0. Условия формирования сигнала R описаны выше.

Рассмотрим формирование сигнала неисправности N на выходе 19 элемента задержки 17 с временем задержки τ Сигнал неисправности N 1, если выходной сигнал второго элемента ИЛИ 15 Т 1 в течение времени t ≥ τ Сигнал Т 1, если сигнал с инверсного выхода первого элемента ИЛИ 14 R 1 (выполняются одновременно равенства 2, 4, и 6) или сигнал с инверсного выхода третьего элемента ИЛИ 16 S 1.

Условия формирования сигнала R ( ) описаны выше. Рассмотрим условия формирования сигнала S. Сигнал S 1, если каждый из сигналов S1 (выход четвертого элемента И 11), S2 (выход пятого элемента И 12) и S3 (выход шестого элемента И 13) равен нулю. Сигнал S1 формируется четвертым элементом И 11, на вход которого подаются сигналы S1m и S2m с выхода (n+1) разряда первого 1 и второго 2 регистров соответственно, S2формируется пятым элементом И 12,на вход которого подаются сигналы S2m и S3m ( с выхода (n+1) разряда третьего регистра 3), S3 формируется шестым элементом И 13, на вход которого подаются сигналы S1m и S3m.

) описаны выше. Рассмотрим условия формирования сигнала S. Сигнал S 1, если каждый из сигналов S1 (выход четвертого элемента И 11), S2 (выход пятого элемента И 12) и S3 (выход шестого элемента И 13) равен нулю. Сигнал S1 формируется четвертым элементом И 11, на вход которого подаются сигналы S1m и S2m с выхода (n+1) разряда первого 1 и второго 2 регистров соответственно, S2формируется пятым элементом И 12,на вход которого подаются сигналы S2m и S3m ( с выхода (n+1) разряда третьего регистра 3), S3 формируется шестым элементом И 13, на вход которого подаются сигналы S1m и S3m.

В соответствии с изложенным имеем

S 1, если S1 S2 S3 0 (7)

S=0, если Sk=1, K∈(1,2,3)

(8)

S1 1, если S1m S2m 1 (9)

S2 1, если S2m S3m 1 (10)

S3 1, если S1m S3m 1 (11)

S1 S2 S3 0, если Skm 0, Spm 0 (12)

P∈(1,2,3), P≠K

Иначе говоря, сигнал S 0, если хотя бы любые два из трех сигналов S1m, S2m и S3m равны 1, сигнал S1, если хотя бы два из трех названных сигналов равны 0.

В соответствии с выражениями (7) и (8) исправной работе устройства соответствует условие (13)

Skm Spm 1, а неисправной работе условие (14)

Skm Spm 0.

Изобретение относится к автоматике и вычислительной технике и может быть использовано для работы в резервированных устройствах. Целью изобретения является повышение достоверности формирования выходных сигналов. Устройство для мажоритарного выбора сигналов содержит три n + 1 разрядных входных регистра, соединенных с входами группы из n-мажоритарных элементов и с соответствующими входами трех групп из n элементов РАВНОЗНАЧНОСТЬ, выходы каждой из которых соединены с соответствующими входами первого, второго и третьего элементов И. Выходы первого, второго и третьего элементов И соединены с входами первого элемента ИЛИ, выход которого соединен с управляющим входом n-канального коммутатора, входы которого подключены к соответствующим выходам группы мажоритарных элементов. Инверсный выход первого элемента ИЛИ соединен с входом второго элемента ИЛИ, выход которого соединен с элементом задержки. Выходы n + 1 разрядов входных регистров соединены с соответствующими входами пятого, шестого и седьмого элементов И, выходы которых соединены с соответствующими входами третьего элемента ИЛИ, инверсный выход которого соединен с вторым входом второго элемента ИЛИ. 1 ил. 2 табл.

УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ, содержащее первый и второй элементы ИЛИ, первый, второй и третий (n + 1)-разрядные входные регистры, первые n выходов каждого из которых подключены к соответствующим входам группы из n мажоритарных элементов, при этом первые n разрядов каждого из входных регистров являются информационными, а (n + 1)-й разряд контрольным, отличающееся тем, что в него дополнительно введены первая, вторая и третья группы из n элементов РАВНОЗНАЧНОСТЬ каждая, первый, второй и третий элементы И на n входов каждый, четвертый, пятый и шестой элементы И на два входа каждый, третий элемент ИЛИ, элемент задержки и n-канальный коммутатор, при этом соответствующие n-е выходы первого, второго и третьего входных регистров соединены с соответствующей парой входов элементов РАВНОЗНАЧНОСТЬ первой, второй и третьей групп, выходы каждой из которых соединены соответственно с входами первого, второго и третьего элементов И, выходы которых подключены к входам первого элемента ИЛИ, прямой выход которого соединен с управляющим входом n-канального коммутатора, инверсный выход первого элемента ИЛИ соединен с первым входом второго элемента ИЛИ, выход которого подключен к входу элемента задержки, второй вход второго элемента ИЛИ соединен с инверсным выходом третьего элемента ИЛИ, первый, второй и третий входы которого подключены к выходам соответственно четвертого, пятого и шестого элементов И, первый и второй входы каждого из которых соединены попарно с выходом (n + 1)-го разряда соответственно первого, второго и третьего его входных регистров, выходы n-мажоритарных элементов соединены соответственно с входами n-канального коммутатора, причем выход элемента задержки является выходом сигнала неисправности, а информация, записываемая в (n + 1)-й разряд каждого регистра, соответствует единичному состоянию.

| Устройство для мажоритарного выбора сигналов | 1986 |

|

SU1325485A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-07-20—Публикация

1990-07-09—Подача