Изобретение относится к технике радиосвязи и может быть использовано для выделения тактовой частоты в системах передачи данных с фазовой манипуляцией.

Цель изобретения - повышение диапазона частот и точности синхронизации.

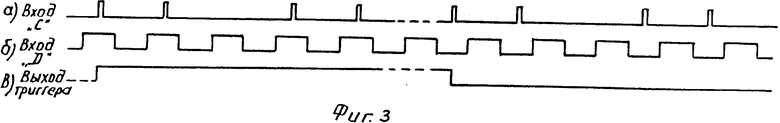

На фиг. 1 представлена структурная электрическая схема устройства; на фиг. 2, 3, 4 - временные диаграммы, поясняющие его работу.

Устройство содержит фазовый детектор 1, первый фильтр 2 нижних частот (ФНЧ), сумматор 9, подстраиваемый генератор 4, первый и второй делители 5, 6 частоты, первый и второй мультиплексоры 7, 8, формирователь 9 коротких импульсов, первый элемент ИЛИ 10, частотомер 11, синхронный D-триггер 12, коммутатор 13 тактов, коммутатор 14 направления, генератор 15 тактовой частоты, бистабильный элемент 16, второй элемент ИЛИ 17, n разрядный двоичный счетчик, цифроаналоговый преобразователь (ЦАП) 19, второй фильтр 20 нижних частот (ФНЧ), миллиамперметр 21.

Устройство для выделения тактового колебания имеет три режима работы, а именно

автоматический поиск по частоте;

автоматическая подстройка фазы;

ручной режим настройки.

Режимы работы устанавливаются позиционным кодом, поступающим с переключателя режим работы (например, типа ПТ-2 с тремя положениями) на управляющие входы коммутатора 13 таков и коммутатора 14 направления. Последние представляют из себя простейшие комбинационные схемы, алгоритм работы которых представлен в табл. 1.

Символы Р и З обозначают в табл. 1 соответственно логические уровни разрешения и запрета для вентилей, входящих в состав коммутаторов 13 и 14. Подстраиваемый генератор 4 имеет октавный диапазон перестройки по частоте. Верхняя граница этого диапазона соответствует максимальному значению рабочей частоты устройства для выделения тактового колебания. Все последующие диапазоны образованы путем деления частот верхнего поддиапазона в первом делителе 5. Выбор поддиапазона осуществляется путем подачи соответствующего кода с переключателя поддиапазонов на управляющие входы первого мультиплексора 7. Выходы второго делителя 6 подключены к сигнальным входам второго мультиплексора 8 таким образом, что при поступлении на управляющие входы первого 7 и второго 8 мультиплексоров кода, соответствующего верхнему частотному поддиапазону, на выход к второму мультиплексору 8 проходит сигнал, поделенный вторым делителем 6 с максимальным коэффициентом деления. При коде на управляющих входах мультиплексоров 7, 8, соответствующему нижнему частотному поддиапазону, на выход второго мультиплексера 8 проходит сигнал, поделенный вторым делителем 6 частоты с минимальным коэффициентом деления.

В табл. 2 показана связь между номером поддиапазона и коэффициентами деления первого и второго делителей 5, 6, сигналы с которых коммутируются на выходы мультиплексоров 7, 8 при количестве поддиапазонов, равном восьми.

Символом m в табл. 2 обозначено начальное значение коэффициента деления второго делителя 6. Выбор определяется быстродействием примененного n-разрядного двоичного счетчика 18 и верхней границей рабочего частотного диапазона.

Устройство работает следующим образом.

Сигнал с выхода демодулятора фазоманипулированных сигналов поступает на n формирователей коротких импульсов 9. Сигнал на выходе первого элемента ИЛИ 10 представляет случайную последовательность коротких импульсов, соответствующих моментам скачков фазы фазоманипулированного сигнала и содержит спектральную составляющую на тактовой частоте сигнала. Для настройки на тактовую частоту сигнала переключателем режимов работы устанавливается первый режим (автоматический поиск по частоте), а переключателем поддиапазонов устанавливается первый (нижний) поддиапазон. При неравенстве частот на выходах синхронного D-триггера 12 (фиг. 2а) на выходе последнего присутствует сигнал с частотой биений (фиг. 2в). Этот сигнал, прошедший через второй делитель 6 частоты, второй мультиплексор 8 и коммутатор 13 тактов поступает на тактовый вход n-разрядного двоичного счетчика 18, преобразующего количество импульсов, поступивших на его вход в двоичный n-разрядный код на выходе. Этот код поступает на цифроаналоговый преобразователь 19, ступенчатое напряжение с выхода которого поступает через сумматор 3 на управляющий вход подстраиваемого генератора 4, осуществляет его перестройку. При этом на индикаторе частотомера 11 наблюдается непрерывное изменение показаний частоты. Последовательно увеличивая номер поддиапазона при помощи переключателя поддиапазонов с выдержкой 2 5 с, добиваются прекращения изменений показания работы на индикаторе частотомера 11. Это свидетельствует о том, что произошел захват системой фазовой автоподстройки частоты. На входах фазового детектора 1 частоты равны, а на выходе формируется напряжение рассогласования, соответствующее остаточной ошибке по фазе. Величина этой ошибки со своим знаком визуально определяется стрелкой миллиамперметра 21. Частоты сигналов на входах синхронного D-триггера 12 также равны (фиг. 3 а, б) и на его выходе в зависимости от направления перестройки, при котором произошел захват, наблюдается либо напряжение логической "1" (фиг. 3в - левая часть эпюры), либо логического "0" (фиг. 3в - правая часть эпюры). Очевидно, что процесс перестройки генератора 4 по частоте заканчивается не в результате анализа величины напряжения на выходе фильтра 2 нижних частот, сравнения этого напряжения с порогами в прототипе и выдаче команд, а в результате пропадания импульсов биений на выходе синхронного D-триггера 12 при равенстве частот на его входах, т. е. в предлагаемом устройстве не требуется схема отключения поиска. Поскольку именно наличие частоты биений является причиной перестройки подстраиваемого генератора 4, процесс поиска по частоте заканчивается автоматически сразу же после захвата частоты кольцом фазовой автоподстройки и не зависит ни от структуры входного сигнала, ни от типа примененного в устройстве фазового детектора 1. В устройстве по мере приближения частоты подстраиваемого генератора 4 к частоте сигнала замедляется скорость поиска.

По окончании поиска по частоте переключателем режимов работы включается режим "два" - автоматическая подстройка фазы. При этом через второй элемент ИЛИ 17 поступает команда на запуск генератора 15 тактовой частоты, импульсы которого через коммутатор 13 поступают на тактовый вход n-разрядного двоичного счетчика 18. В режиме "два" синхронный D-триггер 12 выполняет функцию датчика направления напряжение логического "0" или логической "1", с выхода которого через коммутатор 34 направления поступает на вход направления n-разрядного двоичного счетчика. На выходе цифроаналогового преобразователя 19 изменяется уровень ступенчатого напряжения в сторону уменьшения фазового рассогласования. Процесс подстройки фазы продолжается до момента изменения напряжения на выходе синхронного триггера 12 ("0" "1" или же "1" "0"). Наступает режим слежения, причем отслеживающее напряжение формируется на обоих входах сумматора 3. Точность отслеживания фазы определяется величиной ступеньки цифроаналогового преобразователя 19.

Захват частоты кольцом фазовой автоподстройки на гармониках частоты тактового колебания не вызывает снятия поискового воздействия, так как на выходе синхронного триггера 12 продолжает формироваться сигнал с частотой биений, осуществляющий через коммутатор 13 тактов n-разрядный двоичный счетчик 18, цифроаналоговый преобразователь 19 и второй вход сумматора 3 перестройку генератора 4. Это иллюстрируется эпюрами напряжений на входах синхронного D-триггера 12 (фиг. 4 а, б) и его выходе (фиг. 4в) для случая, когда входная частота в два раза выше частоты тактового колебания.

При низком отношении сигнал/шум входного сигнала включается режим "три" (ручной режим настройки). При нажатии одной из кнопок ручной настройки через второй элемент ИЛИ 17 запускается генератор 15 тактовой частоты, вырабатывающий импульсы, которые через коммутатор 13 тактов поступает на тактовый вход n-разрядного двоичного счетчика 18, на вход направления которого поступает сигнал логического "0" или "1" через коммутатор 14 от бистабильного элемента 16. Состояние выхода бистабильного элемента 16 задается нажатием одной из кнопок ручной перестройки в зависимости от требуемого направления перестройки. Контроль захвата по частоте и постройке по фазе осуществляется с помощью миллиамперметра 21. (56) Авторское свидетельство СССР N 566376, кл. Н 04 L 7/02, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНТЕЗАТОР ЧАСТОТЫ | 2002 |

|

RU2237972C2 |

| ТЕЛЕВИЗИОННОЕ УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ПЕРЕМЕЩЕНИЙ ОБЪЕКТОВ | 1984 |

|

RU2140721C1 |

| Устройство восстановления несущей частоты многопозиционных фаз манипулированных сигналов с переменной кратностью | 1989 |

|

SU1626437A1 |

| ИЗМЕРИТЕЛЬ ФАЗ ОСЦИЛЛОГРАФИЧЕСКИЙ | 2005 |

|

RU2314543C2 |

| Преобразователь напряжения | 1990 |

|

SU1713043A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

| БИНАРНЫЙ КВАНТОВАТЕЛЬ С РЕГУЛИРУЕМЫМ ПОРОГОМ | 1993 |

|

RU2065252C1 |

| УСТРОЙСТВО ПАКЕТНОЙ ОБРАБОТКИ ЗАПРОСОВ | 1992 |

|

RU2035065C1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| УСТРОЙСТВО ПРИЕМА АДРЕСНОГО ВЫЗОВА | 1994 |

|

RU2097941C1 |

Использование: в технике радиосвязи для выделения колебания тактовой частоты в системах передачи данных с фазовой манипуляцией. Сущность изобретения: устройство содержит фазовый детектор 1, первый фильтр 2 нижних частот (ФНЧ), сумматор 3, подстраиваемый генератор 4, первый и второй делители 5,6 частоты, первый и второй мультиплексоры 7,8, формирователь 9 коротких импульсов, первый элемент ИЛИ 10, частотомер 11, синхронный D-триггер 12, коммутатор 13 тактов, коммутатор 14 направления, генератор 15 тактовой частоты, бистабильный элемент 16, второй элемент ИЛИ 17, n-разрядный двоичный счетчик 18, цифроаналоговый преобразователь 19, второй фильтр 20 нижних частот, миллиамперметр 21. Изобретение обеспечивает повышение диапазона частот и точности синхронизации. 4 ил.

УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ТАКТОВОГО КОЛЕБАНИЯ, содержащее первый элемент ИЛИ и последовательно соединенные фазовый детектор, фильтр нижних частот (ФНЧ) и сумматор, выход которого подключен к управляющему входу перестраиваемого генератора, отличающееся тем, что, с целью повышения диапазона частот и точности синхронизации, введены первый и второй делители частоты, первый и второй мультиплексоры, синхронный D-триггер, второй элемент ИЛИ, генератор тактовой частоты, коммутатор тактов, бистабильный элемент, коммутатор направления, n-разрядный двоичный счетчик, цифроаналоговый преобразователь (ЦАП), n формирователей коротких импульсов и второй ФНЧ, выход которого подключен к входу миллиамперметра, а к входу второго ФНЧ подключен выход фазового детектора, к первому входу которого, а также к D-входу синхронного D-триггера и входу частотомера подключен выход первого мультиплексора и является тактирующим выходом устройства, при этом n формирователей коротких импульсов через первый элемент ИЛИ подключены к второму входу фазового детектора и синхровходу синхронного D-триггера, выход которого подключен к первому сигнальному входу коммутатора направления и к входу второго делителя частоты, выходы которого подключены к сигнальным входам второго мультиплексора, при этом выход перестраиваемого генератора подключен к первому сигнальному входу первого мультиплексора и через первый делитель частоты к другим сигнальным входам первого мультиплексора, управляющие входы которого и управляющие входы второго мультиплексора являются входами кодов переключателя диапазонов устройства, входами ручной настройки которого являются первые и вторые входы бистабильного элемента и второго элемента ИЛИ, выход которого подключен к запускающему входу генератора тактовой частоты, при этом выходы второго мультиплексора и генератора тактовой частоты подключены соответственно к первому и второму сигнальным входам коммутатора тактов, а выход бистабильного элемента подключен к второму сигнальному входу коммутатора направления, третий, четвертый и пятый управляющие входы которого соединены соответственно с третьим, четвертым и пятым управляющими входами коммутатора тактов и являются входами переключения режимов работы, причем пятые управляющие входы коммутатора тактов и коммутатора направления подключены к третьему входу элемента ИЛИ, а выходы коммутатора тактов и коммутатора направления подключены соответственно к тактовому входу и входу направления n-разрядного двоичного счетчика, выходы которого через цифроаналоговый преобразователь подключены к второму входу сумматора.

Авторы

Даты

1994-02-15—Публикация

1991-03-18—Подача