TiaxoflHTCfi: в режиме в пор пока его содер шится до нуля. Это с вычитающего счетчика но вторым дешифратор состояния, на выходе ляется импульс, кото на вход К- 1-К-тригг элемент ИЛИ 16 прохо гер 17 и будет запис BbfM сигналом, в резу выходе D-триггера пульс, который запис гер 18 состояние О решения записи второ счеТчика гТЗ поступае сигнал и в него след импульсом будет запи

При этом импульс на дешифратора 15 зако

Первьц вычитающий чинает производить ла N, по единице за

Изобретение относится к радиотех 1и- ке и может быть использовано для формирования сетки стабильных частот в приемопередающей измерительной аппаратуре.5

Целью изобретения является повышение быстродействия.

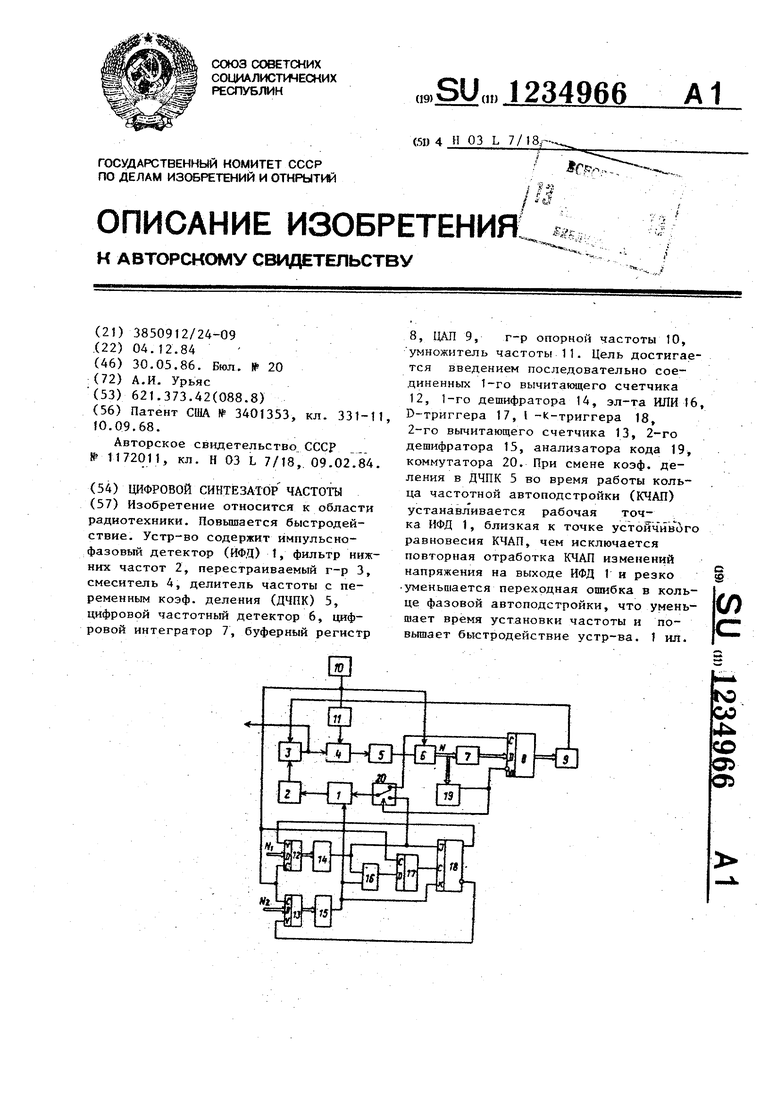

На чертеже изображена структурная электрическая схема цифрового синте- затора частоты.Ш

Цифровой синтезатор -шстоты содержит импульсно-фазовый детектор (ИФД) 1, фильтр нижних частот (ФНЧ) 2, перестраиваемый генератор 3, смеситель 4, делитель частоты с переменным 55 коэффициентом деления (ДПКД) 5, цифровой частотньш детектор 6, цифро - вой интегратор 7, буферный регистр 8, Цифроаналоговый преобразователь (ЦДЛ) 9, Генератор опорной частоты 10, 20 умножитель 11 частоты, первый вычитающий счетчик 12, второй вычитающий счетчик 13, первьш дешифратор 1А, второй дешифратор 15, элемент 1-ШИ 16,

С -триггер 17, I-К-триггер 18, анализа-25 продолжается до тех тор кода 19, коммутатор 20.

Цифровой синтезатор частоты рабо тает следующим образом.

ЦIiфpoвoй синтезатор частоты состоит из трех частей:кольца частотной авто- подстройки, состоящего из перестраиваемого генератора 3, смесителя 4, :ЛПКД 5, цифрового частотного детек- тора 6 и цифрового интегратора 7, буферного регистра 8 и ЦАП 9, кольца фазовой автоподстройки, состоящего из перестраиваемого генератора 3, смесителя 4, ДПКД 5, коммутатора 20, ИФД 1 и ФНЧ 2; узла формирования опорных сигналов ИФД 1,состоящего из первого и второго вычитающих счетчиков 12 и 13 первого и второго дешифраторов, 14 и 15, элемента ИЛИ 16, D-триггера 17 и 1-К-триггера 18.

Формирование опорного сигнала ИФД 1.происходит следующим образом.

Сигнал с выхода генератора опорной частоты 10 поступает на тактовые входы первого и второго вычитаю 1у1х счетчиков 12 и 13, на информационные входы которых поданы постоянные коды N, и N. соответственно. Пусть в не30

35

, И N соответственно, который момент времени I-К-триггер 18 находится в состоянии 1, тогда сигнал с его выхода дает разрешение на параллельную запись кода N в первьгй вычитающий счетчик 12. Второй вычитающий счетчик 13 в это время

опорной частоть и э

держимое первого вы чика 12 не уменьшит вькоде первого деши явится импульс, в р опрокидывается 1 -К ма переходит в исход В результате на вых второго дешифраторо чески появляются им тью в один период о и с периодом-, равны риодов опорной част чем между импульсам сдвиг,, равный (N,-+ выходными импульсам первого 14 дешифрато на считывание до нул один такт на задерж 17), и равный ( выходными импульсам го деишфраторов.Рдим для исключения боте схемы.

В режиме синхрони зовой автоподстройки коммутатор 20, и час выходе ДПКД 5 равна ла на выходе второго и принимает свое номи

40

50

55

„

где ной

г (

« IS н N,,

1о частота частоты 10.

TiaxoflHTCfi: в режиме вычитания до тех пор пока его содержимое не уменьшится до нуля. Это состояние второго вычитающего счетчика 13 зафиксировано вторым дешифратором 15 нулевого состояния, на выходе которого появляется импульс, который поступает на вход К- 1-К-триггера 18, и через элемент ИЛИ 16 проходит на I) -триггер 17 и будет записан в него такто- BbfM сигналом, в результате чего на выходе D-триггера 17 появляется импульс, который записывает в 1 -К-три гер 18 состояние О, и на вход разрешения записи второго вычитающего счеТчика гТЗ поступает разрешающий сигнал и в него следующим тактовым импульсом будет записано число N ,

При этом импульс на вьгходе второго дешифратора 15 закончится.

Первьц вычитающий счетчик 12 начинает производить вычитание из числа N, по единице за каждый период

продолжается до тех

опорной частоть и этот peлда i работы

пор, пока содержимое первого вычитающего счетчика 12 не уменьшится до нуля, а на вькоде первого дешифратора 14 не появится импульс, в результате чего опрокидывается 1 -К-триггер 18 и схема переходит в исходное состояние. В результате на выходах первого и второго дешифраторов 14 и 15 периодически появляются импульсы длительностью в один период опорной частоты и с периодом-, равным (N,+N,4- 2) периодов опорной частоты (тактов), причем между импульсами,будет временный сдвиг,, равный (N,-+ 1) тактов между выходными импульсами второго 15 и первого 14 дешифраторов (N, тактов на считывание до нуля числа N плюс один такт на задержку в D--триггере 17), и равный ( 1) тактов между выходными импульсами первого и второ- го деишфраторов.Ртриггер 17 необходим для исключения состязаний в работе схемы.

В режиме синхронизации кольцо фазовой автоподстройки замкнуто через коммутатор 20, и частота сигнала на выходе ДПКД 5 равна частоте сигнала на выходе второго дешифратора 15 и принимает свое номинальное значение.

„

где ной

г (

« IS н N,, 1

1о частота частоты 10.

генератора опор312

На в(1ходе цифрового qacTOTfforo детехторг к моменту прихода очеред-- ного импульса с выхода ДПКД 5 будет иметь место нулевой код и содержимое 5дафрозог о интет ратора 7 изменяться не будет. Анализатор кода 19 вырабатывает выходной сигнал, если посту- пагошее на него с выхода ц1- фрового частотного детектора 6 число N не превышает по абсолютной величине не- которую заранее установленную величину (например f может быть равной одной или двум двоичным единицам в зависимости от параметров системы). В режимы синхронизации кольца фазо- вой автоподстройки значение N равно нулю и выходной сигнал анализатора кода 1 9 запрещает перепись числа с выхода цифрового интегратора 7 в буферный регистре, сохраняя постоянным его вы- ходнойкод, и, соответственно, выходное напряжение 1ДАП 9, а также соединяет вы- ход ДПКД 5 со входом ИФД.1 чарез коммутатор 20, замыкая кольцо фазовой автоподстройки. Такое состояние устройства сохраняется до смены ко- эффициёнта деления в ДПКД 5,

При изменении коэффициента деления ДПК, Д 5 частота сигнала на его выходе изменяется и на выходе цифро- вого частотного детектора 6 появляется число, значительно отличающееся от нуля, в результате чего на вькоде анализатора кода 19 сигнал исчезает. При этом коммутатор 20 разрывает кольцо фазовой автоподстройки и замыкается кольцо частотной автоподстройки путем снятия запрета переписки с входа буферного регистра 8. В этом реяа-гме на входы ИФД t поступают сигналы с вы- ходов первого и второго дешифраторов 14 и 15, одинаковые, по частоте, но сдвинутые во времени (и, следовательно, п-о фазе) на величину, определяемую соотношением кодов N, Это соотношение всегда можно выбрать таКИМ, чтобы сдвиг фаз сигналов на входах ИФД 1 точно (с точностью до одного периода опорной частоты) соот ветствовал рабочей точке ИФД 1 в режиме синхронизации кольца ФАП.

Вь;бором соотношения кодов N, и N всегда можно обеспечить, чтобы в . режиме, работы кольца частотной автоподстройки разность фаз на входах ИФД 1 соответствовала .разности фаз в режиме синхронизма кольца фазовой автоподстройки,, что эквивалентно

тому, что напряжеР ие на выходе Ф,Ц I в обоих случаях остается одинаковьм.

Если обозначить через К oTHonieu ie опорной частоты f к шагу сетки синтезатора (к частоте на втором входе ИФД Я, то для выполнения этого условия достаточно выбрать значения К,, и N ближайшими целыми к следующим величинам:

f

N, -f .

(О

N, K( 1- -f )-1..

(2)

0

5

Например, если используется пило-, образный фазовый детектор и начальная расстройка равна нулю, .то , 71 и N, К/2-1, К/2-1,

При треугольной характеристике фазового детектора р, 1 /2 и NY К/4- -1, N ЗК/4-1.

Таким образом, в режиме работы . кольца частотной автоподстройки напряжение на выходе ИФД 1 поддерживает ся постоянным. После того, как переходной процесс в кольце частотной автоподстройки закончится и частота сигнала на выходе ДПКД 5 станет близкой ( с точностью до ошибки дискретности цифрового частотного детектора 6) к своему номинальному значению, число на выходе цифрового частотного детектора 6 станет равным игги близким к нулю, анализатор кода: 19 выработает выходной сигнал, который раэрыва-ет цепь ко.чьца частотной ав- топодстройки через иуферный регистр S с запоминанием напр.яжения на выходе ЦАП 9 и замыкает кольцо фазовой азтоподстройки, подключая первый вход ИФД 1 к выходу ДПКД 5 через коммутатор 20. При этом, поскольку разность фаз на входах ИФД 1 уже бьша очень близка к точке устойчивоца равновесия Ч., , то переходной процесс в кольце ФАП имеет очень малую амплитуду и длительность (эксперимент показывает, что при К 50 выброс фазовой ошибки не превышает 3,5°),

В предлагаемом устройстве при смене коэффициента деления в ДПКД 5 (т.е. при перестройке частоты синтезатора) во время работы кольца частотной автоподстройки устанавливается рабочая точка ИФД 1, очень близкая к точке устойчивого равновесия коль- .ца фазовой автоподстройки, чем исключается возможность повторной отработки кольцом частотной автоподстройки

изменений напряжения на выходе ИФД 1 и резко уменьшается переходная ошибка в кольце фазовой автоподстройки, что в конечном итоге уменьшает время установки частоты и повышает быстродей- ствие синтезатора частот. Для обеспечения этого эффекта необходимо установить значения кодов N , и N по формулам (1) и (2) в зависимости от параметров синтезатора и типа примененного ИФД 1 .

Использование изобретения в циф-. ровых синтезаторах частоты позволит исключить изменение выходного напря- женин ИФД 1 в процессе начальной установки частоты, установить заранее рабочую точку ИФД 1, устранить возможность повторных отработок частоты кольцом частотной автоподстройки и уменьшить переходную ошибку в кольце фазовой автоподстройки, что в совокупности позволяет улучшить один из основных параметров широкополосных синтезаторов частоты - быст- родействие при перестройке частоты .

Формула изобретения

Цифровой синтезатор частоты, содержащий последовательно соединенные импульсно-фазовьш детектор, фильтр нижних частот, перестраиваемый генератор, смеситель, делитель частоты с переменным коэффициентом деления, цифровой частотный детектор цифровой интегратор, буферный регистр и ияфроаналоговый преобразователь, выход которого соединен с вторым входом перестраиваемого гене

Редактор К.Волощук Заказ 2990/58

Составитель Ю.Ковалев

Техред О.Гортвай Корректор М.Самборская

Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35., Раушская наб., д. 4/5

Производственно-полиграфическое :предприятие, г.Ужгород, ул.Проектная,4

ратора, тлследовательно соединенные генератор опорной частоты и умножитель частоты, выход которого подключен к второму входу смесителя, при этом выход генератора опорной частоты соединен также с тактовым входом цифрового частотного детектора, о т- личающийся тем, что, с целью повьппения быстродействия, введены последовательно соединенные первый вычитающий счетчик, первый дешифратор, элемент ИЛИ, D -триггер, 1 -к- триггер, второй вычитающий счетчик и второй дешифратор, анализатор кода и коммутатор,управляющий вход которого объединен с входом запрета записи буферного регистра и подключен к выходу анализатора кода, вход которого соединен с выходом цифрового частотного детектора, тактовые входы первого и второго вычитающих счетчиков и Т)-триггера объединены и подключены к выходу генератора опорной частоты, первый вход коммутатора объединен с I -входом I -К-триггера и подключен .к выходу первого дешифратора, при этом первый вход импуль- сно-фазового детектора, К -вход Т-К-триггера и второй вход эл€;мента ИЛИ объединены и подключены к выходу второго дешифратора, прямой выход 1 -К-триггера соединен с входом разрешения параллельной записи первого вычитающего счетчика, выход коммутатора подключен к второму входу им- . пульсно-фазового детектора, а второй вход коммутатора объединен с тактовым входом буферного регистра и соединен с выходом делителя частоты с переменным коэффициентом деления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1363458A1 |

| Цифровой синтезатор частот | 1987 |

|

SU1494215A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Синтезатор частот | 1987 |

|

SU1474838A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Синтезатор частот | 1989 |

|

SU1730720A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1172011A1 |

| Цифровой синтезатор частот | 1983 |

|

SU1117840A1 |

Изобретение относится к области радиотехники. Повышается быстродействие. Устр-во содержит ймпульсно- фазовый детектор (ИФД) 1, фильтр нижних частот 2, перестраиваемый г-р 3, смеситель 4, делитель частоты с переменным коэф. деления (ДЧПК) 5, цифровой частотный детектор 6, цифровой интегратор 7, буферный регистр 8, ЦАП 9, г-р опорной частоты 10, умножитель частоты 11. Цель достигается введением последовательно соединенных 1-го вычитающего счетчика 12, 1-го дешифратора 14, эл-та ИЛИ 16, D-триггера 17, I -к-триггера 18, 2-го вычитающего счетчика 13, 2-го дешифратора 15, анализатора кода 19, коммутатора 20. При смене коэф. деления в ДЧПК 5 во время работы кольца частотной автоподстройки (КЧАП) устанавливается рабочая точка ИФД 1, близкая к точке устойч йвого равновесия КЧАП, чем исключается повторная отработка КЧАП изменений напряжения на выходе ИФД 1 и резко уменьшается переходная ошибка в кольце фазовой автоподстройки, что уменьшает время установки частоты и по- вьш1ает быстродействие устр-ва. 1 ил. (Л

| Патент США № 3401353, кл | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-05-30—Публикация

1984-12-04—Подача