Изобретение относится к автоматике и технической диагностики и может быть использовано в устройствах распознавания случайных сигналов.

Цель изобретения - повышение точности устройства.

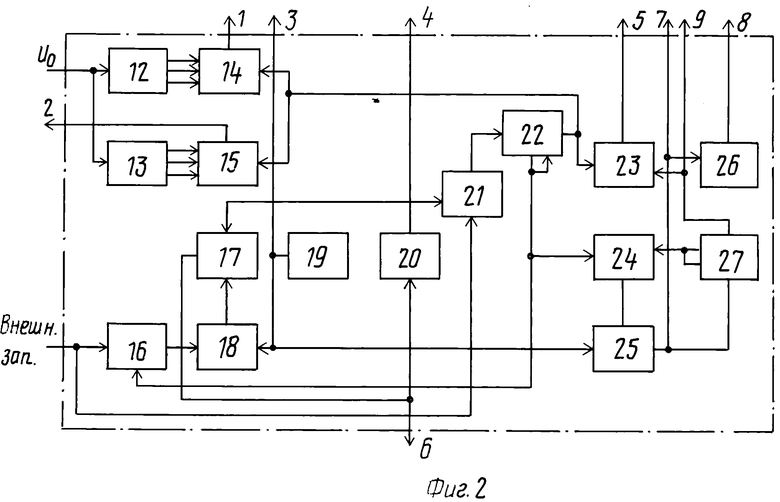

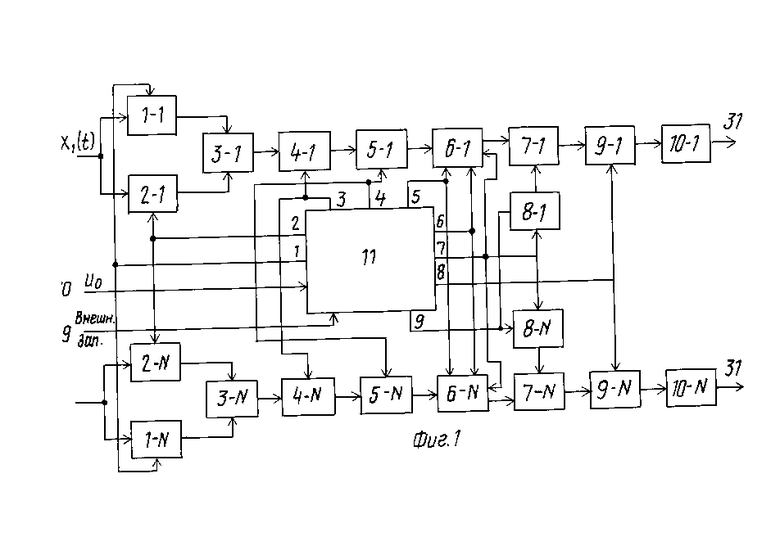

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - блок управления.

Устройство содержит N каналов, каждый из которых содержит первый 1 и второй 2 компараторы, элемент 3 ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент 4 И, счетчик 5, блок 6 оперативной памяти, умножитель 7, блок 8 постоянной памяти, накапливающий сумматор 9, блок 10 сравнения, блок 11 управления.

Блок 11 управления содержит первый 12 и второй 13 делители напряжения, первый 14 и второй 15 коммутаторы, первый триггер 16, первый счетчик 17, первый элемент 18 И, генератор импульсов 19, первый элемент задержки 20, первый элемент 21 ИЛИ, второй счетчик 22, второй элемент 23 ИЛИ, второй триггер 24, второй элемент 25 И, второй элемент задержки 26 и третий счетчик 27.

Позицией 28 обозначен информационный вход устройства, 29 - его управляющий вход, 30 - вход подачи опорного напряжения, 31 - выходы устройства.

Все каналы идентичны, поэтому рассмотрим работу одного. В каждом канале происходит оценивание гистограммы и далее с помощью линейного классификатора принимается решение о принадлежности сигнала тому или иному классу.

Устройство работает следующим образом.

На первый вход компаратора 1 поступают исследуемые сигналы со входа 28, а на второй вход - опорное напряжение Иоп1 с блока 11 управления. Как только входное напряжение превысит Иоп1, на выходе компаратора 1 появится логическая единица, которая поступает на первый вход элемента 3 ИСКЛЮЧАЮЩЕЕ ИЛИ. На первый вход компаратора 2 поступают исследуемые сигналы со входа 28, а на второй вход - опорное напряжение Иоп1 (Иоп1 > Иоп1) с блока управления 11. Как только входное напряжение превысит Иоп1, на выходе компаратора 2 появится логическая единица, которая поступает на второй вход элемента 3 ИСКЛЮЧАЮЩЕЕ ИЛИ. На выходе элемента 3 ИСКЛЮЧАЮЩЕЕ ИЛИ имеем логическую единицу только в том случае, когда на одном из его входов присутствует логический ноль, а на другом - логическая единица, т. е. длительность сигнала на выходе элемента 3 ИСКЛЮЧАЮЩЕЕ ИЛИ пропорциональна времени пребывания входного сигала в интервале (Иоп1 - Иоп1). Сигнал с выхода элемента 2 ИСКЛЮЧАЮЩЕЕ ИЛИ поступает на первый вход элемента 4 И, на второй вход которого поступают импульсы с генератора 19 блока управления 11. Импульсы с выхода элемента 4 И подсчитываются в счетчике 5, т. е. показания Р1 счетчика 5 пропорциональны времени, в течение которого Иоп1 < Ивх < Иоп1. Сравнение Ивх с опорными напряжениями происходит за время анализа Та. После чего блок управления 11 формирует для блока 6 импульс разрешения записи и адресные сигналы, после чего происходит запись показаний счетчика 5 в блок 6. Далее меняются значения опорных напряжений до величин Иоп2 и Иоп2. Цикл повторяется, т. е. в счетчике 5 накапливается величина Р2, пропорциональная времени, в течение которого Иоп2 < Ивх < Иоп2 и т. д. для всех Иопi и Иопi (i = 1, М, где М - число порогов сравнения). После того, как в блок 6 записано М значений величины Pi, первый этап работы закончен.

Решение о принадлежности сигнала тому или иному классу принимается на втором этапе работы. На этом этапе блок управления 11 формирует адресные сигналы и сигналы разрешения выборки для блока 6 и блока 8, а также тактовые сигнала для накапливающего сумматора 9. Под действием этих импульсов из блока 6 считываются значения Pi, из блока 8 - значения коэффициентов γi , которые перемножаются в умножителе 7, произведения накапливаются в сумматоре 9 и сумма сравнивается с порогом С в блоке 10 сравнения. Порог С определяется на этапе обучения совместно с весовыми коэффициентами γi.

Решающее правило имеет вид (для двухклассовой ситуации):

если  Pi>C, то X(t) ∈ F1

Pi>C, то X(t) ∈ F1

если  Pi≅ C, то X(t) ∈ F2 где X(t) - входной сигнал.

Pi≅ C, то X(t) ∈ F2 где X(t) - входной сигнал.

Блок 11 управления работает следующим образом.

Импульс внешнего запуска со входа 29 устанавливает триггер 16 в единичное состояние, этот же импульс записывается в счетчике 22 (через элемент ИЛИ 21), который подсчитывает число порогов сравнения. От внешнего источника напряжение Ио со входа 30 поступает на входы резистивных делителей напряжения 12 и 13, на выходах которых формируются опорные напряжения Иопi и Иопi. Через коммутаторы 14 и 15, работой которых управляют сигналы с выхода счетчика 22, напряжения Иопi и Иопi поступают соответственно на коммутаторы 1-1, . . . , 1-N и 2-1, . . . , 2-N. На вход счетчика 17 подаются импульсы с генератора 19 через элемент И 18. Объем счетчика 17 пропорционален времени анализа Та. Сигнал переполнения счетчика 17, свидетельствующий об окончании анализа, подается на входы разрешения записи блоков 6-1, . . . , 6-N, адресные входы которых соединены с выходом счетчика 22 (через элемент 23 ИЛИ). Импульс переполнения счетчика 17, задержанный элементом задержки 20 на время записи чисел в блоки 6-1, . . . , 6-N, подается на вход счетчика 22 и обнуляет счетчики 17 и 5-1, . . . , 5-N. Следовательно, показания счетчика 22 увеличиваются на единицу, на выходах коммутаторов появляются другие опорные напряжения, цикл повторяется. Объем счетчика 22 равен заданному числу порогов. Импульс переполнения счетчика 22 свидетельствует об окончании первого этапа работы. Этот импульс подается на вход установки в "О" триггера 16 (т. е. импульсы с генератора 19 переступают поступать на вход счетчика 17), обнуляет счетчик 22 и подается на вход установки в "1" триггера 24. Импульсы с выхода генератора 19 через элемент И 25 поступают на вход разрешения выборки блоков 6-1, . . . , 6-N и блоков 8-1, . . . , 8-N, а также вход счетчика 27, на выходе которого формируется адресный сигнал для блоков 6-1, . . . , 6-N и блоков 8-1, . . . , 8-N. Эти же импульсы, задержанные элементом задержки 26 на время выборки из блоков 6-1, . . . , 6-N чисел Pi и из блока 8-1, . . . , 8-N коэффициентов γi и их перемножения в перемножителях 7-1, . . . , 7-N, являются тактовыми для накапливающих сумматоров 9-1, . . . , 9-N. Импульс переполнения счетчика 27, объем которого соответствует заданному числу порогов, подается на вход установки в "0" триггера 24 и обнуляет счетчик 27. Устройство готово к обработке следующей последовательности.

Повышение точности в предложенном устройстве осуществлено тем, что при распознавании учитывается информация о высших моментах распределений многомерных сигналов с некоррелированными компонентами. (56) Авторское свидетельство СССР N 851431, кл. G 06 K 9/00, 1979.

Использование: область автоматики и технической диагностики. Сущность изобретения: устройство содержит в каждом канале два компаратора 1, 2, один элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3, один элемент И 4, один счетчик 5, один блок оперативной памяти 6, один умножитель 7, один накапливающий сумматор 9, один блок постоянной памяти 8, один блок сравнения, один блок управления 11. 1 - 3 - 4 - 5 - 6 - 7 - 9 - 10, 2 - 3, 11 - 1, 11 - 2, 11 - 4, 11 - 5, 11 - 6, 11 - 8, 11 - 9. 1 з. п. ф-лы, 2 ил.

Авторы

Даты

1994-03-15—Публикация

1990-12-10—Подача