со

СХ) 00

00 со со

Изобретение относится к вычислительной технике.

Цель изобретения - повышение точности устройства.

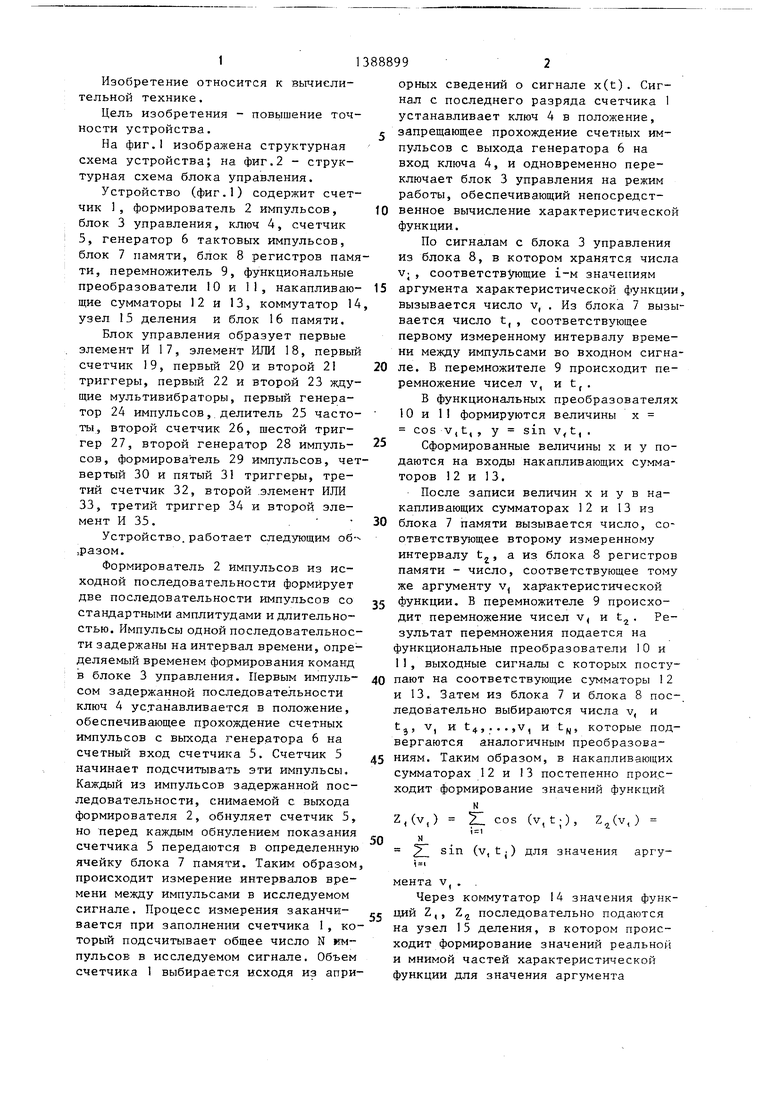

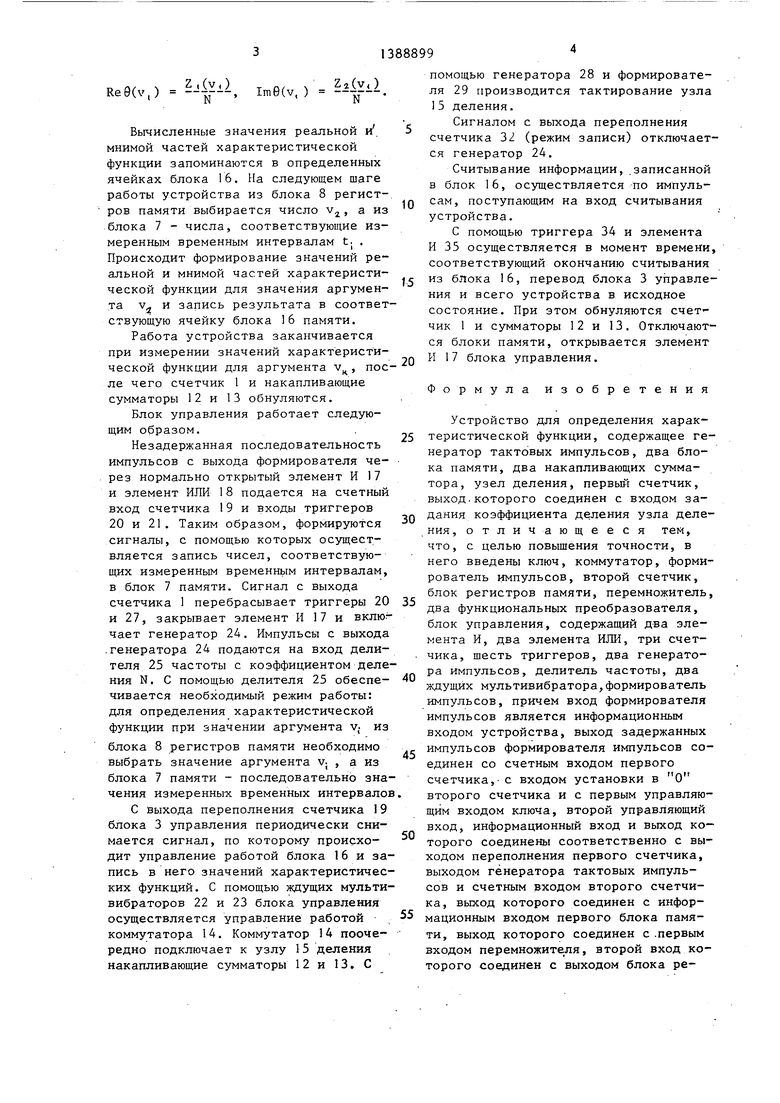

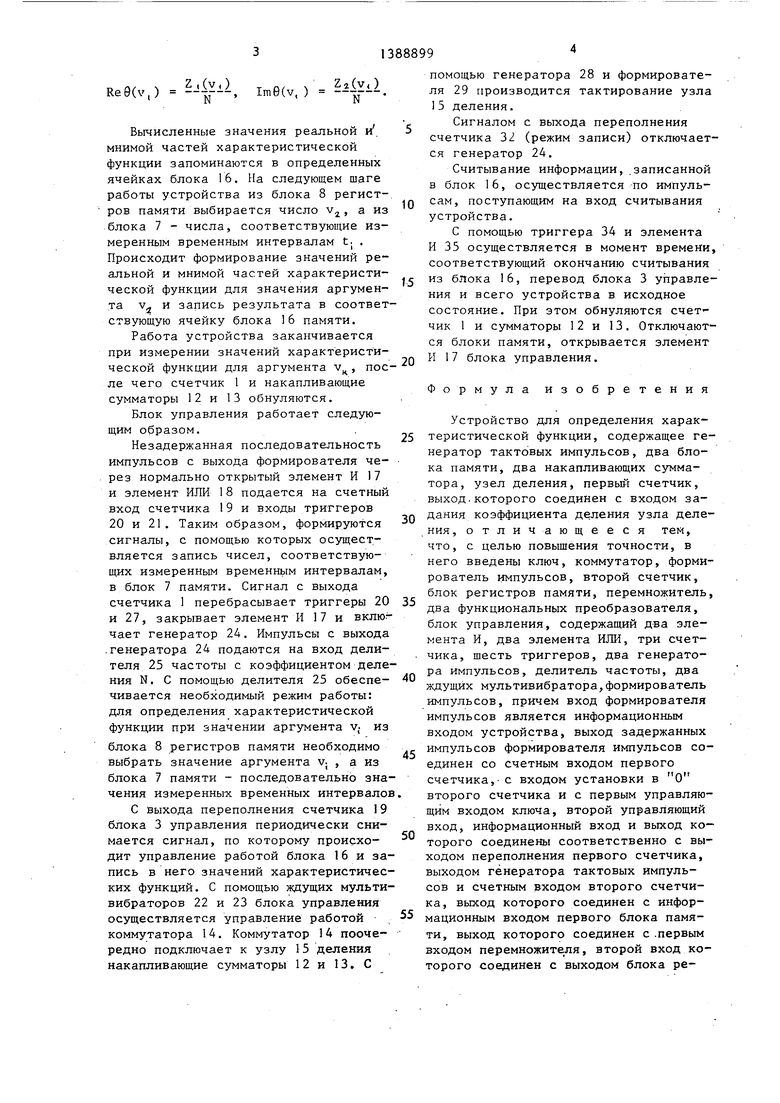

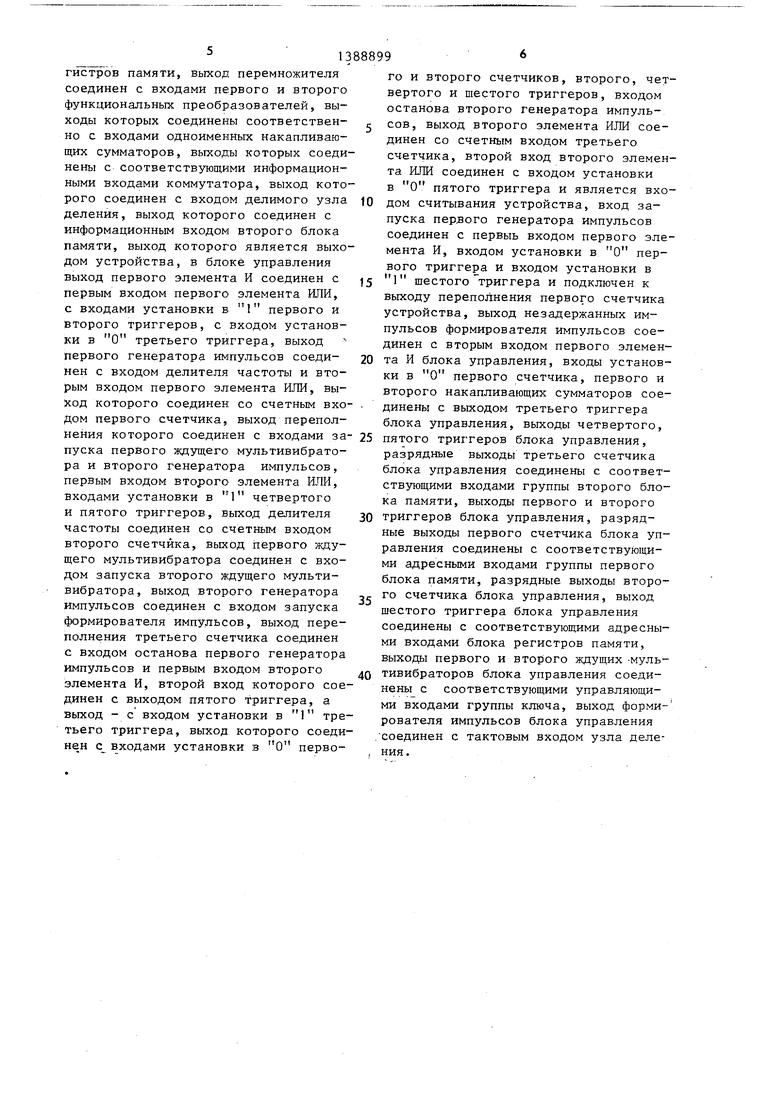

На фиг.1 изображена структурная схема устройства; на фиг.2 - структурная схема блока управления.

Устройство (фиг.1) содержит счетчик 1, формирователь 2 импульсов, блок 3 управления, ключ 4, счетчик 5, генератор 6 тактовых импульсов, блок 7 памяти, блок 8 регистров памяти, перемножитель 9, функциональные

1

преобразователи 10 и 11, накапливаю- щие сумматоры 12 и 13, коммутатор 14 узел 15 деления и блок 16 памяти.

Блок управления образует первые элемент И 17, элемент ИЛИ 18, первый счетчик 19, первый 20 и второй 21 триггеры, первый 22 и второй 23 ж,цу- щие мультивибраторы, первый генератор 24 импульсов, делитель 25 частоты, второй счетчик 26, шестой триггер 27, второй генератор 28 импульсов, формирователь 29 импульсов, четвертый 30 и пятый 31 триггеры, третий счетчик 32, второй .элемент ИЛИ 33, третий триггер 34 и второй элемент И 35..

Устройство, работает следующим об.разом.

Формирователь 2 импульсов из исходной последовательности формирует две последовательности импульсов со стандартными амплитудами и длительностью. Импульсы одной последовательности задержаны на интервал времени, определяемый временем формирования команд в блоке 3 управления. Первым импульсом задержанной последовательности ключ 4 ус.танавливается в положение, обеспечивающее прохождение счетных импульсов с выхода генератора 6 на счетный вход счетчика 5. Счетчик 5 начинает подсчитывать эти импульсы. К 1ждый из импульсов задержанной последовательности, снимаемой с выхода формирователя 2, обнуляет счетчик 5, но перед каждым обнулением показания счетчика 5 передаются в определенную ячейку блока 7 памяти. Таким образом происходит измерение интервалов времени между импульсами в исследуемом сигнале. Процесс измерения заканчивается при заполнении счетчика I, который подсчитывает общее число N им- пульсоЕ в исследуемом сигнале. Объем счетчика 1 выбирается исходя из апри

20

25

30

15 ,

, 888992

орных сведений о сигнале x(t). Сигнал с последнего разряда счетчика 1 устанавливает ключ 4 в положение, г запрещающее прохождение счетных импульсов с выхода генератора 6 на вход ключа 4, и одновременно переключает блок 3 управления на режим работы, обеспечивающий непосредст- 10 венное вычисление характеристической функции.

По сигналам с блока 3 управления из блока 8, в котором хранятся числа Vj, соответствующие i-м значениям аргумента характеристической функции, вызывается число v, . Из блока 7 вызывается число t, , соответствующее первому измеренному интервалу времени между импульсами во входном сигнале. В перемножителе 9 происходит перемножение чисел V, и tj.

В функциональных преобразователях 10 и 1 формируются величины х cos v,t,, у sin v,t,.

Сформированные величины х и у подаются на входы накапливающих сумматоров 12 и 13.

После записи величин х и у в накапливающих сумматорах 12 и 13 из блока 7 памяти вызывается число, соответствующее второму измеренному интервалу tj,, а из блока 8 регистров памяти - число, соответствующее тому же аргументу v, хар актеристической функции. В перемножителе 9 происхо35

40

дит перемножение чисел v и t. Результат перемножения подается на функциональные преобразователи 10 и 11, выходные сигналы с которых поступают на соответствующие сумматоры 12 и 13. Затем из блока 7 и блока 8 последовательно выбираются числа v, и

V,

и t

-3 1 вергаются

4,...,v, И t, которые под- аналогичным преобразова- 5 ниям. Таким образом, в накапливающих сумматорах 12 и 13 постепенно происходит формирование значений функций N

Z,(V,) i: cos (v,t;), Z(V,)

1 1 N

sin (v,tj) для значения аргу0

мента V,. .

Через коммутатор 14 значения функций Z,, Z последовательно подаются на узел 15 деления, в котором происходит формирование значений реальной и мнимой частей характеристической функции для значения аргумента

5jiYl)

N

Ime(v, )

lYi

N

Вычисленные значения реальной и, мнимой частей характеристической функции запоминаются в определенных ячейках блока 16. На следующем шаге работы устройства из блока 8 регистров памяти выбирается число v, а из блока 7 - числа, соответствующие измеренным временным интервалам tj . Происходит формирование значений реальной и мнимой частей характеристической функции для значения аргумента Vj и запись результата в соответствующую ячейку блока 16 памяти.

Работа устройства заканчивается при измерении значений характеристической функции для аргумента v, j пос ле чего счетчик 1 и накапливающие сумматоры 12 и 13 обнуляются.

Блок управления работает следующим образом.

Незадержанная последовательность импульсов с выхода формирователя через нормально открытый элемент И 17 и элемент ИЛИ 18 подается на счетный вход счетчика 19 и входы триггеров 20 и 21. Таким образом, формируются сигналы, с помощью которых осуществляется запись чисел, соответствующих измеренным временньгм интервалам, в блок 7 памяти. Сигнал с выхода счетчика 1 перебрасывает триггеры 20 и 27, закрывает элемент И 17 и вклю чает генератор 24. Импульсы с выхода .генератора 24 подаются на вход делителя 25 частоты с коэффициентом деления N. С помощью делителя 25 обеспечивается необходимый режим работы: для определения характеристической функции при значении аргумента V; из

блока 8 регистров памяти необходимо выбрать значение аргумента V; , а из блока 7 памяти - последовательно значения измеренных временных интервалов

С выхода переполнения счетчика 19 блока 3 управления периодически снимается сигнал, по которому происходит управление работой блока 16 и запись в него значений характеристических функций. С помощью ждущих мультивибраторов 22 и 23 блока управления осуществляется управление работой коммутатора 14. Коммутатор 14 поочередно подключает к узлу 15 деления накапливающие сумматоры 12 и 13. С

помощью генератора 28 и формирователя 29 производится тактирование узла 15 деления.

Сигналом с выхода переполнения

счетчика 32 (режим записи) отключается генератор 24.

Считывание информации, записанной в блок 16, осуществляется -по импуль Q сам, поступающим на вход считывания устройства.

С помощью триггера 34 и элемента И 35 осуществляется в момент времени, соответствующий окончанию считывания

.5 из блока 16, перевод блока 3 управления и всего устройства в исходное состояние. При этом обнуляются счет чин 1 и сумматоры 12 и 13. Отключаются блоки памяти, открывается элемент

20 И 17 блока управления.

Формула изобретения

Устройство для определения харак- 25 теристической функции, содержащее генератор тактовых импульсов, два блока памяти, два накапливающих сумматора, узел деления, первый счетчик, выход.которого Соединен с входом задания коэффициента деления узла деления, отличающееся тем, что, с целью повьшения точности, в него введены ключ, коммутатор, формирователь импульсов, второй счетчик, блок регистров памяти, перемножитель, два функциональных преобразователя, блок управления, содержащий два элемента И, два элемента ИЛИ, три счетчика, шесть триггеров, два генератора импульсов, делитель частоты, два ждущих мультивибратора,формирователь импульсов, причем вход формирователя импульсов является информационным входом устройства, выход задержанных импульсов формирователя импульсов соединен со счетным входом первого счетчика,- с входом установки в О второго счетчика и с первым управляющим входом ключа, второй управляющий вход, информационный вход и выход которого соединены соответственно с выходом переполнения первого счетчика, выходом генератора тактовых импульсов и счетным входом второго счетчика, выход которого соединен с инфор- 55 мационным входом первого блока памяти, выход которого соединен с .первым входом перемножителя, второй вход которого соединен с выходом блока ре30

35

40

45

50

13

памяти, выход перемножителя соединен с входами первого и второго функциональных преобразователей, выходы которых соединены соответственно с входами одноименных накапливающих сумматоров, выходы которых соединены с соответствующими информационными входами коммутатора, выход которого соединен с входом делимого узла деления, выход которого соединен с информационным входом второго блока памяти, выход которого является выходом устройства, в блоке управления выход первого элемента И соединен с первым входом первого элемента ИЛИ, с входами установки в 1 первого и второго триггеров, с входом установки в О третьего триггера, выход первого генератора импульсов соединен с входом делителя частоты и вторым входом первого элемента ИЛИ, выход которого соединен со счетным входом первого счетчика, выход переполнения которого соединен с входами запуска первого ждущего мультивибратора и второго генератора импульсов, первым входом второго элемента ИЛИ, входами установки в 1 четвертого и пятого триггеров, выход делителя частоты соединен со счетным входом второго счетчика, выход первого ждущего мультивибратора соединен с входом запуска второго ждущего мультивибратора, выход второго генератора импульсов соединен с входом запуска формирователя импульсов, выход переполнения третьего счетчика соединен с входом останова первого генератора импульсов и первым входом второго элемента И, второй вход которого соединен с выходом пятого триггера, а выход - с входом установки в 1 третьего триггера, выход которого соединен с входами установки в О перво

0

го и второго счетчиков, второго, четвертого и шестого триггеров, входом останова второго генератора импульсов, выход второго элемента ИЛИ соединен со счетным входом третьего счетчика, второй вход второго элемента ИЛИ соединен с входом установки в О пятого триггера и является входом считывания устройства, вход запуска первого генератора импульсов соединен с первыь входом первого элемента И, входом установки в О первого триггера и входом установки в

1 шестого триггера и подключен к выходу переполнения первого счетчика устройства, выход незадержанных импульсов формирователя импульсов соединен с вторым входом первого элемента И блока управления, входы установки в О первого счетчика, первого и второго накапливающих сумматоров соединены с выходом третьего триггера блока управления, выходы четвертого, пятого триггеров блока управления, разрядные выходы третьего счетчика блока управления соединены с соответствующими входами группы второго блока памяти, выходы первого и второго триггеров блока управления, разрядные выходы первого счетчика блока управления соединены с соответствующими адресными входами группы первого блока памяти, разрядные выходы второ го счетчика блока управления, выход

5

0

0

шестого триггера блока управления соединены с соответствующими адресными входами блока регистров памяти, выходы первого и второго ждущих -мультивибраторов блока управления соеди- нены с соответствующими управляющими входами группы ключа, выход форми- рователя импульсов блока управления соединен с тактовым входом узла деления.

бход

2дход

группа 8xooo8

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| АНАЛИЗАТОР ПЛОТНОСТИ ВЕРОЯТНОСТИ ФАЗЫ СИГНАЛА | 2006 |

|

RU2313101C1 |

| Термокомпенсированный кварцевый генератор ударного возбуждения | 1989 |

|

SU1709491A2 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ РАДИОТЕХНИЧЕСКОЙ СИСТЕМЫ ПЕРЕДАЧИ ИНФОРМАЦИИ С АМПЛИТУДНО-ИМПУЛЬСНОЙ МОДУЛЯЦИЕЙ | 1991 |

|

RU2042194C1 |

| Устройство синхронизации | 1990 |

|

SU1781835A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЭНЕРГЕТИЧЕСКИХ ПАРАМЕТРОВ АНТЕННЫ | 1994 |

|

RU2139548C1 |

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ ПОМЕХОУСТОЙЧИВОСТИ ПРИЕМНИКА ВИДЕОСИГНАЛОВ | 1993 |

|

RU2048680C1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1112550A2 |

| Цифровой измеритель временных интервалов | 1982 |

|

SU1065822A1 |

| Телевизионный цветосинтезатор | 1985 |

|

SU1284006A1 |

Изобретение относится к области- вычислительной техники. Целью изобретения является повьппение точности. Цель достигается за счет исключения переходных процессов при анализе импульсных случайных процессов, а также за счет измерения значений характеристической функции для произвольных значений аргумента. Работа устройства основывается на измерении длительности пауз между импульсами с последующим функциональным преобразованием и суммированием измеренных значений. Устройство содержит счетчики 1,5, формирователь 2 импульсов, блок 3 управления, ключ 4, генератор 6 тактовых импульсов, блоки 7, 16 памяти, блок 8 регистров памяти, перемножитель 9, функциональные преобразователи 10, 11, накапливающие сумматоры 12, 13, узел деления 15, коммутатор 14, 2 ил. с (Л

«

| Устройство для определения структурной функции | 1983 |

|

SU1117659A1 |

Авторы

Даты

1988-04-15—Публикация

1986-06-24—Подача