Изобретение относится к электротехнике, в частности к стабилизированным источникам тока.

Известен стабилизатор постоянного регулируемого тока [1] , который содержит силовой регулятор, соединенный через датчик тока с выводами для подключения нагрузки, управляющий вход силового регулятора подключен к выходу усилителя постоянного тока, вход которого подключен к выходу датчика тока, который выполнен в виде измерительного узла с уравновешиванием ампервитков постоянных токов, включающего измерительную обмотку, подключенную к входным выводам датчика тока, компенсационную обмотку, состоящую изN отдельных секций с разным числом витков, детектор разбаланса ампервитков, выход которого является выходом датчика тока, источник эталонного тока, силовой трансформатор и цифровой переключатель, состоящий из N транзисторных переключающих ячеек, к выходным выводам которых подключены соответственно выводы секций компенсационной обмотки, переключающие ячейки входными выводами соединены последовательно друг с другом, необъединенные входные выводы первой и N-й ячеек являются входными выводами цифрового переключателя, управляющие входы переключающих ячеек подключены к соответствующим выходам блока связи с ЭВМ.

Основной недостаток известного устройства - ухудшение точности стабилизации тока. Ухудшение точности стабилизации обусловлено токами утечки коммутирующих транзисторов, составляющих основу цифрового переключателя прототипа. Погрешность стабилизатора, обусловленная токами утечки коммутирующих транзисторов, при прочих равных условиях тем больше, чем больше величина среднего значения тока утечки применяемых транзисторов.

Известен стабилизатор постоянного регулируемого тока, являющийся наиболее близким техническим решением к данному изобретению [2] . Он содержит силовой регулятор, соединенный через датчик тока с выводами для подключения нагрузки, пороговый элемент тока, одновибратор, вход запуска которого подключен к соответствующему выходу блока связи с электронно-вычислительной машиной, к соответствующему входу которого подключен выход порогового элемента тока, усилитель постоянного тока, вход которого подключен к выходу датчика тока, который выполнен в виде измерительного узла с уравновешиванием ампервитков постоянных токов, включающего в себя измерительную обмотку, подключенную к входным выводам датчика тока, компенсационную обмотку, состоящую из N отдельных секций с разным числом витков, детектор разбаланса ампервитков, выход которого является выходом датчика тока, источник эталонного тока, силовой трансформатор с первичной и N вторичной обмотками, а также цифровой переключатель, состоящий из N переключающих ячеек, к выходным выводам которых подключены соответственно выводы секций компенсационной обмотки, к выводам переменного тока переключающих ячеек подключены соответственно вторичные обмотки силового трансформатора, переключающие ячейки входными выводами соединены последовательно друг с другом, необъединенные входные выводы первой и N-ячеек использованы в качестве входных выводов цифрового переключателя, управляющие входы переключающих ячеек подключены к соответствующим выходам блока связи с электронно-вычислительной машиной, при этом каждая из переключающих ячеек содержит первый и второй тиристоры, управляющие электроды тиристоров через шунтирующие резисторы соединены с их катодами, первый и второй оптоэлектронные ключи, управляющие входы которых использованы в качестве управляющих входов переключающей ячейки цифрового переключателя. Основной недостаток прототипа - снижение надежности стабилизатора, что проявляется в ошибках при отработке уставки тока. Эти ошибки случаются в цифровом переключателе. Для устранения каждой ошибки приходится повторно приводить в действие цифровой переключатель. Причина указанных ошибок (т. е. сбоев в цифровом переключателе) состоит в следующем. Когда цифровой переключатель приводится в действие для отработки уставки, это означает, что в действие приводятся в общем случае N контуров принудительной коммутации тиристоров. Даже при весьма высокой надежности действия одного контура вероятность сбоев увеличивается в N раз за счет массовости, а с учетом того, что в момент коммутации в контурах коммуникации должны развиваться относительно высокие импульсные мощности, становится ясно, что практическая реализация высоконадежной системы контуров коммутации является сложной задачей.

Кроме того, в балластных резисторах суммарно рассеивается значительная мощность (порядка 100 Вт для стабилизатора на номинальный ток 4кА).

Целью изобретения является повышение надежности стабилизатора.

Для этого в стабилизатор, содержащий силовой регулятор, соединенный через датчик тока с выводами для подключения нагрузки, пороговый элемент тока, одновибратор, вход запуска которого подключен к соответствующему выходу блока связи с электронно-вычислительной машиной, к соответствующему входу которого подключен выход порогового элемента тока, усилитель постоянного тока, вход которого подключен к выходу датчика тока, который выполнен в виде измерительного узла с уравновешиванием ампервитков постоянных токов, включающего в себя измерительную обмотку, подключенную к входным выводам датчика тока, компенсационную обмотку, состоящую из N отдельных секций с разным числом витков, детектор разбаланса ампервитков, выход которого является выходом датчика тока, источник эталонного тока, силовой трансформатор с первичной и N вторичными обмотками, а также цифровой переключатель, состоящий из N переключающих ячеек, к выходным выводам которых подключены соответственно выводы секций компенсационной обмотки, к выводам переменного тока переключающих ячеек подключены соответственно вторичные обмотки силового трансформатора, переключающие ячейки входными выводами соединены последовательно друг с другом, необъединенные входные выводы первой и N-й ячеек использованы в качестве входных выводов цифрового переключателя, управляющие входы переключающих ячеек подключены к соответствующим выходам блока связи с электронно-вычислительной машиной, при этом каждая переключающая ячейка содержит первый и второй тиристоры, управляющие электроды тиристоров через шунтирующие резисторы соединены с катодами, первый и второй оптоэлектронные ключи, управляющие входы которых использованы в качестве управляющих входов переключающей ячейки цифрового переключателя, введены аналоговый запоминающий блок, вход которого подключен к выходу усилителя постоянного тока, выход - управляющему входу силового регулятора, а управляющий вход - к выходу одновибратора, дополнительная переключающая ячейка, выводы переменного тока которой подключены к дополнительной вторичной обмотке, введенной в силовой трансформатор.

Первый вывод источника эталонного тока соединен непосредственно с первым выводом цифрового переключателя, а через резистор - с первым выводом дополнительной переключающей ячейки, второй вывод которой соединен с вторым входным выводом цифрового переключателя, второй вывод источника эталонного тока через пороговый элемент тока соединен с третьим выводом дополнительной переключающей ячейки, управляющие входы которой подключены к соответствующим выходам блока связи с электронно-вычислительной машиной. В каждую переключающую ячейку цифрового переключателя введен выпрямитель, выводы переменного тока которого использованы в качестве выводов переменного тока переключающей ячейки, анод первого тиристора соединен соответственно с первым входным и первым выходным выводами переключающей ячейки, второй выходной вывод которой соединен с анодом второго тиристора, к объединенным катодам первого и второго тиристоров подключены второй входной вывод переключающей ячейки, общие выводы первого и второго оптоэлектронных ключей, а также соответствующий вывод постоянного тока выпрямителя, второй вывод постоянного тока которого подключен к входным выводам первого и второго оптоэлектронных ключей, выходные выводы которых подключены соответственно к управляющим электродам первого и второго тиристоров.

Существенными отличительными признаками предложенного технического решения являются введенные в устройство аналоговый запоминающий блок, дополнительная переключающая ячейка, резистор, а также дополнительная обмотка, введенная в силовой трансформатор, и выпрямители, введенные в каждую переключающую ячейку цифрового переключателя. Существенными отличительными признаками являются также новые связи между указанными и другими элементами в их совокупности.

Введенные в прототип перечисленные новые элементы и связи обеспечивают повышение надежности стабилизатора, так как в новом техническом решении исключены (N - 1) контуров принудительной коммутации. Соответствующая работа переключающих ячеек цифрового переключателя обеспечивается действием дополнительной переключающей ячейки, которая содержит контур принудительной коммутации. Дополнительная переключающая ячейка обеспечивает принудительное выключение всех включенных тиристоров цифрового переключателя за счет снятия тока с цифрового переключателя и отвода его в шунтирующую цепь, образованную соответствующими элементами дополнительной переключающей ячейки. В результате сбои в цифровом переключателе, обусловленные процессом коммутации его тиристоров, исключаются. Вероятность сбоев в цифровом переключателе определяется теперь вероятностью сбоев коммутации тиристоров в одной дополнительной переключающей ячейке.

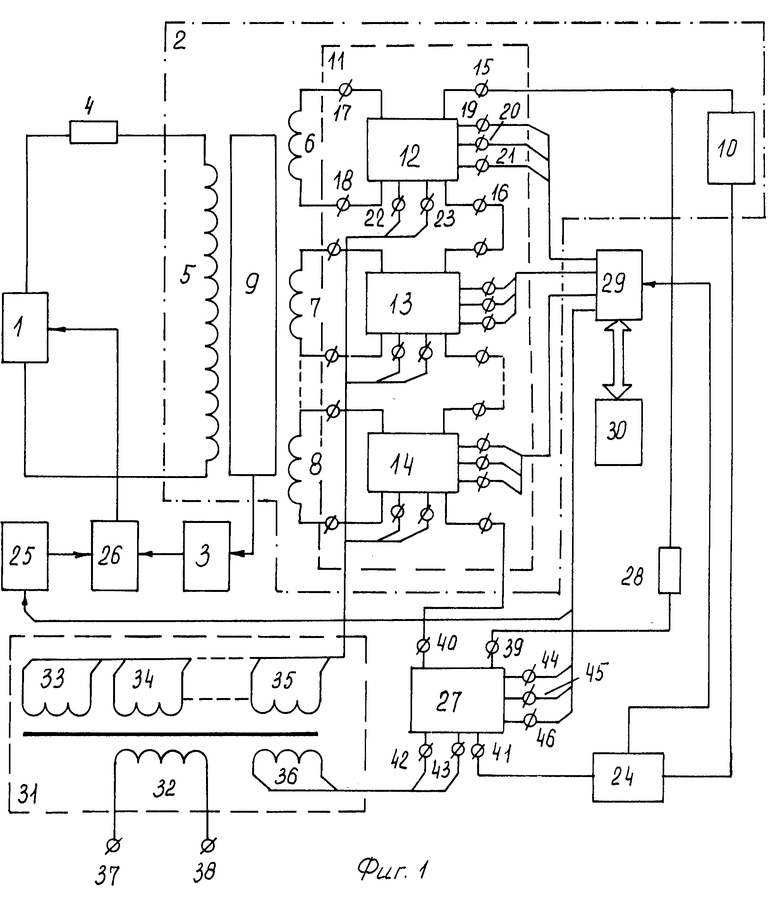

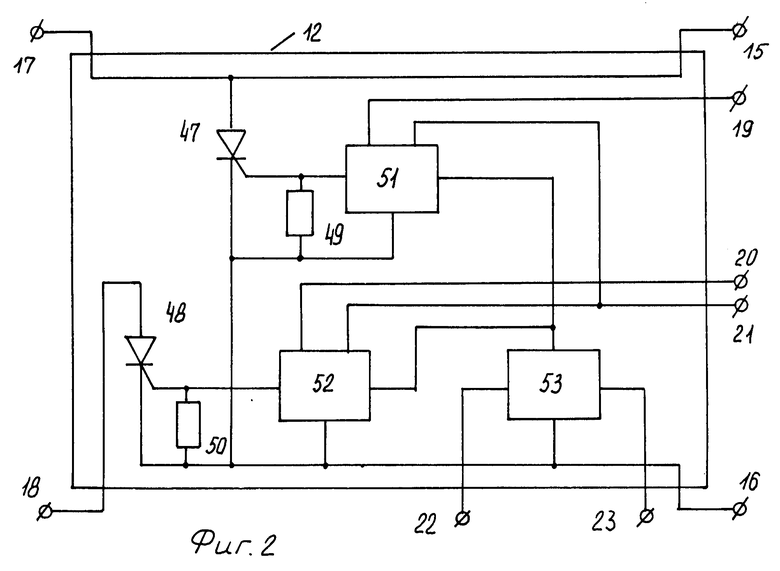

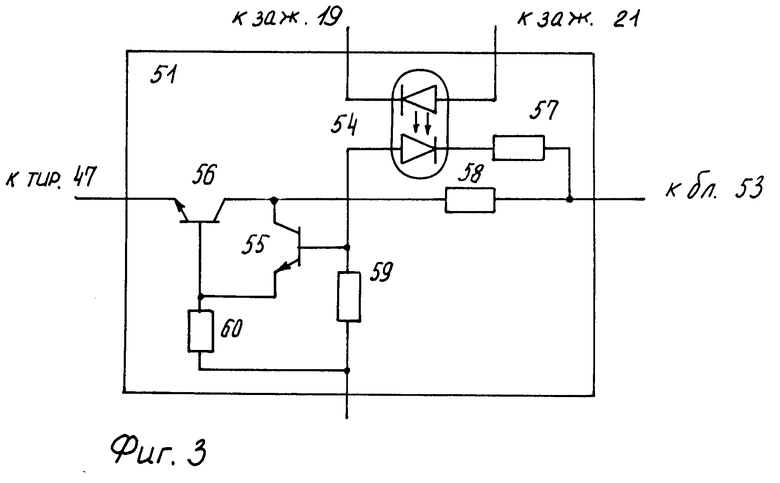

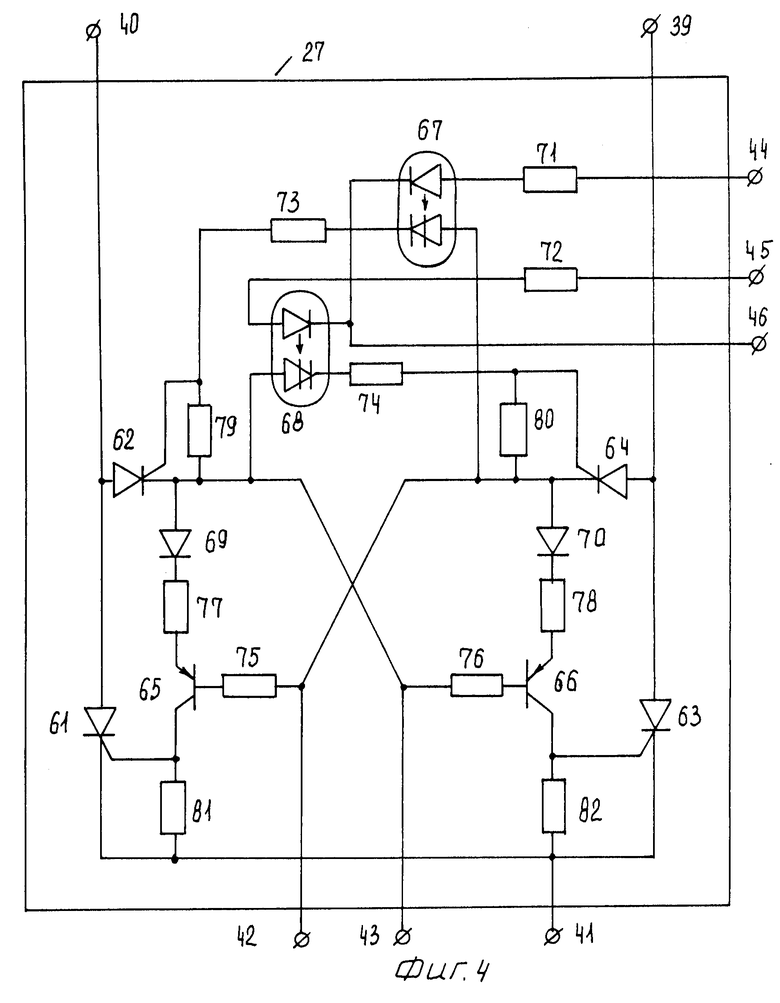

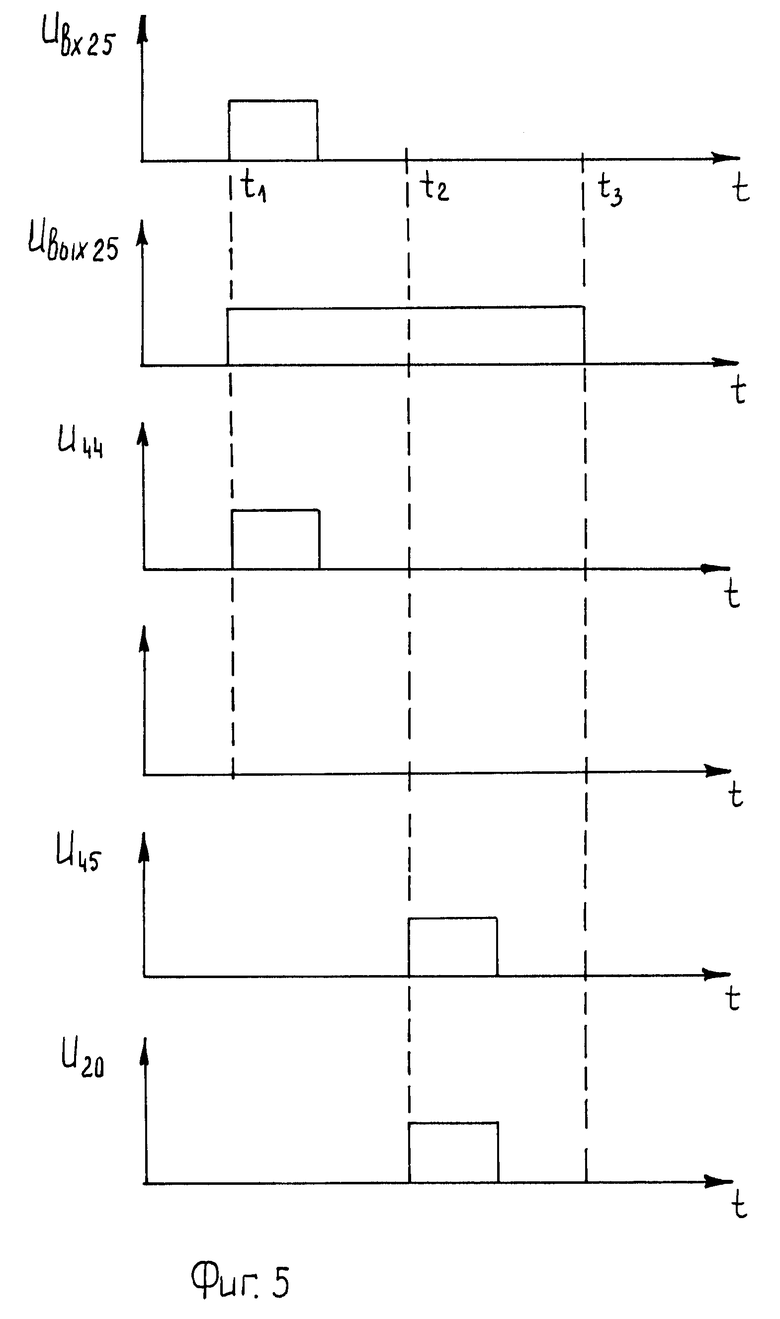

На фиг. 1 представлена блок-схема предложенного стабилизатора постоянного регулируемого тока; на фиг. 2 - принципиальная схема переключающей ячейки цифрового переключателя; на фиг. 3 - принципиальная схема оптоэлектронного ключа (пример выполнения); на фиг. 4 - принципиальная схема дополнительной переключающей ячейки (пример выполнения); на фиг. 5 - временные диаграммы управляющих импульсов.

Стабилизатор (см. фиг. 1) содержит силовой регулятор 1, датчик 2 тока, усилитель 3 постоянного тока, нагрузку 4 стабилизатора. Датчик 2 тока выполнен на основе измерительного узла с уравновешиванием ампервитков постоянных токов и содержит измерительную обмотку 5, компенсационную обмотку, включающую в себя первую 6, вторую 7 и N-ю 8 секции, детектор 9 разбаланса ампервитков, источник 10 эталонного тока и цифровой переключатель 11, содержащий первую 12, вторую 13 и N-ю 14 переключающие ячейки. Выводы первой переключающей ячейки 12 обозначены следующим образом: входные - 15 и 16, выходные - 17 и 18, управления - 19 и 20, переменного напряжения - 22 и 23 (остальные переключающие ячейки цифрового переключателя 11 имеют аналогичные выводы, которые для упрощения чертежа не нумеруются).

Стабилизатор содержит также пороговый элемент 24 тока, одновибратор 25, аналоговый запоминающий блок 26, дополнительную переключающую ячейку, резистор 28, блок 29 связи с ЭВМ 30, силовой трансформатор 31, имеющий первичную обмотку 32 и (N + 1) вторичных: первую 33, вторую 34, N-ную 35 и дополнительную 36. Выводы 37 и 38 первичной обмотки 32 служат для подключения силовой сети. Выводы дополнительной переключающей ячейки 27 обозначены следующим образом: первый - 39, второй - 40, третий - 41, выводы переменного тока - 42 и 43, выводы управления - 44 и 45, общий - 46.

Силовой регулятор 1 через нагрузку 4 подключен к измерительной обмотке 5, т. е. к входу датчика тока 2. Управляющий вход силового регулятора 1 подключен к выходу аналогового запоминающего блока 26, вход которого через усилитель 3 постоянного тока подключен к детектору 9 разбаланса ампервитков, т. е. к выходу датчика тока 2. Измерительная обмотка 5 и секции 6, 7 и 8 компенсационной обмотки имеют магнитную связь с детекторами 9 разбаланса ампервитков. Управляющий вход аналогового запоминающего блока 26 подключен к выходу одновибратора 25, вход запуска которого подключен к соответствующему выходу блока 29 связи с ЭВМ 30.

Переключающие ячейки 12, 13 и 14 цифрового переключателя 11 входными выводами соединены последовательно друг с другом. Необъединенные выводы ячеек 12 и 14 являются входными выводами цифрового переключателя 11, к ним через пороговый элемент 24 тока и соответствующую цепь дополнительной переключающей ячейки 27 подключен источник 10 эталонного тока. Через другую цепь дополнительной переключающей ячейки 27 и пороговый элемент 24 тока к источнику 10 эталонного тока подключен резистор 28.

Секция 6 компенсационной обмотки подключена к выходным выводам 17, 18 первой переключающей ячейки 12. Секции 7 и 8 компенсационной обмотки подключены к аналогичным выводам соответственно ячеек 13 и 14 цифрового переключателя 11. Управляющие выводы 19, 20 и общий вывод 21 переключающей ячейки 12, а также аналогичные выводы ячеек 13, 14 и 27 подключены к соответствующим выходам блока 29 связи с ЭВМ. Блок 29 связи через магистраль связан с ЭВМ 30.

Первая вторичная обмотка 33 силового трансформатора 29 подключена к выводам 22, 23 переменного напряжения первой переключающей ячейки 12. Другие вторичные обмотки 43, 35 и 36 подключены к аналогичным выводам соответствующих ячеек 13, 14 и 27. Первичная обмотка 32 подключена к зажимам 37 и 38, которые служат для подключения к силовой сети переменного тока.

Переключающие ячейки 12, 13 и 14 цифрового переключателя 11 выполнены по одной схеме, представленной на фиг. 2. Каждая переключающая ячейка содержит первый 47 и второй 48 тиристоры, резисторы 49 и 50, первый 51 и второй 52 оптоэлектронные ключи, выпрямитель 53.

Анод первого тиристора 47 соединен с первым 15 входным и первым 17 выходным выводами переключающей ячейки, второй выходной вывод 18 которой соединен с анодом второго тиристора 48. Катоды тиристоров 47 и 48 объединены, к ним подключены второй 16 входной вывод переключающей ячейки, общие (силовые) выводы оптоэлектронных ключей 51 и 52, а также соответствующий вывод постоянного тока выпрямителя 53, второй вывод постоянного тока которого подключен к входным выводам оптоэлектронных ключей 51 и 52. Выводы переменного тока выпрямителя 53 подключены к зажимам 22 и 23, которые являются выводами переменного тока переключающей ячейки. Управляющие электроды тиристоров 47 и 48 подключены соответственно к выходам оптоэлектронных ключей 51 и 52. Промежутки управляющий электрод-катод тиристоров 47 и 48 шунтированы резисторами 49 и 50. Управляющие выводы оптоэлектронных ключей подключены к зажимам 19 и 20, к зажиму 21 подключен их общий вывод (общий вывод цепей управления).

Пример выполнения оптоэлектронного ключа иллюстрируется принципиальной схемой, представленной на фиг. 3. Оптоэлектронный ключ содержит диодную оптопару 54, выходные выводы которой являются управляющими выводами оптоэлектронного ключа, двойной составной транзистор, включающий транзисторы 55 и 56. Эмиттер транзистора 56 соединен с выходным выводом оптоэлектронного ключа, коллекторы транзисторов 55 и 56 через ограничительный резистор 58 подключены к входному выводу оптоэлектронного ключа, с которым через ограничительный резистор 57 и вывод оптопары 54 соединена база транзистора 55. К общему (силовому) выводу оптоэлектронного ключа через резисторы 59 и 60 подключены базы транзисторов 55 и 56.

Дополнительная переключающая ячейка 27 (см. фиг. 4) содержит тиристоры 61- 64, транзисторы 65 и 66, тиристорные оптопары 67 и 68, полупроводниковые вентили 69 и 70, резисторы 71-82.

К первому выводу 39 ячейки подключены аноды тиристоров 63 и 64, к второму выводу 40 - аноды тиристоров 61 и 62, а к третьему выводу 41 - катоды тиристоров 61 и 63. К управляющим электродам тиристоров 61 и 63 подключены соответственно коллекторы транзисторов 65 и 66, базы которых через ограничительные резисторы 75 и 76 подключены к выводам 42 и 43 переменного тока переключающей ячейки. К выводу 42 подключены также катод тиристора 64, анод полупроводникового вентиля 70 и анод фототиристора оптопары 67, катод которого через ограничительный резистор 73 подключен к управляющему электроду тиристора 62. Катод полупроводникового вентиля 70 через токозадающий резистор 78 соединен с эмиттером транзистора 66. К выводу 43 подключены катод тиристора 62, анод полупроводникового вентиля 69 и анод фототиристора оптопары 68, катод которого через ограничительный резистор 74 подключен к управляющему электроду тиристора 64. Катод полупроводникового вентиля 69 через токозадающий резистор 77 соединен с эмиттером транзистора 65.

Первые входные выводы оптопар 67 и 68 через ограничительные резисторы 71 и 72 подключены к управляющим выводам 44 и 45 переключающей ячейки, к общему ее выводу 45 подключены объединенные вторые входные выводы оптопар 67 и 68. Управляющие электроды тиристоров 61-64 через шунтирующие резисторы 79-82 соединены с их катодами.

Стабилизатор работает следующим образом.

Рассмотрение работы устройства начнем с момента, когда уже реализованы команды, в результате чего дополнительная ячейка 27 находится в состоянии, при котором к источнику 10 эталонного тока подключен вход цифрового переключателя 11; переключающие ячейки 12, 13 и 14 находятся в состоянии, при котором в цепь эталонного тока включены требуемые секции компенсационной обмотки. При этом число включенных витков компенсационной обмотки составляет Wк, протекающий по ним эталонный ток Iэт создает намагничивающую силу (н. с. ) IэтWк. Под действием этой н. с. детектор 9 разбаланса ампервитков вырабатывает напряжение, которое через усилитель 3 постоянного тока и аналоговый запоминающий блок 26 поступает на управляющий вход силового регулятора 1. Под действием управляющего напряжения силовой регулятор I вырабатывает ток Iн, который протекает через нагрузку 4 и измерительную обмотку 5 с числом витков Wн. Обмотка 5 с током Iн создает н. с. IнWn, направленную навстречу н. с. IэтWк. Указанные здесь элементы образуют замкнутый контур автоматического регулирования, действие которого направлено на поддержание баланса н. с.

IэтWk - IнWn = ΔIWg, где Δ IWg - действующее рассогласование в контуре авторегулирования.

При большем коэффициенте усиления действующее рассогласование становится пренебрежимо малой величиной, тогда

Iн = IэтWkWn.

Таким образом, предложенное устройство обеспечивает стабилизацию нагрузки Iн и регулирование его с дискретностью (шагом) IэтWn, если дискретность изменения Wк равна одному витку (при Wn = 1 вит ку, что часто реализуется на практике, в этом случае дискретность равна Iэт).

Рассмотрим теперь работу цифрового переключателя 11 во взаимодействии с другими элементами устройства. Для простоты будем рассматривать процессы в одной ячейке цифрового переключателя 11, например, в ячейке 12.

Пусть до начала рассмотрения состояние ячейки 12 соответствовало отключенной секции 6 компенсационной обмотки. Это означает, что первый тиристор 47 открыт, а второй тиристор 48 заперт. Ток протекает через открытый тиристор 47. В выходную цепь переключающей ячейки ответвляет ся только малый ток ly1, равный току утечки запертого тиристора 48. Ток ly1 протекает через секцию 6 компенсационной обмотки и является причиной появления одной из составляющих погрешности стабилизатора.

Пусть теперь в блок 29 связи поступает от ЭВМ 30 (или пульта ручного ввода) новый код установки тока нагрузки, согласно которому секция 6 компенсационной обмотки должна быть включена. По поступлении указанного нового кода в блоке 29 связи вырабатываются импульсы управления, временная диаграмма которых представлена на фиг. 5.

В момент времени t1, управляющий импульс Uвх25 поступает на вход запуска одновибратора 25, который вырабатывает на выходе импульс Uвых25, поступающий на управляющий вход аналогового запоминающего блока 26. С момента t1 в течение всего времени действия импульса Uвых25 на управляющем входе силового регулятора 1 сохраняется значение управляющего напряжения, которое было на выходе усилителя 3 постоянного тока непосредственно перед моментом t1. Очевидно, что в этих условиях в течение времени действия импульса Uвых25 контур авторегулирования стабилизатора не действует (разомкнут) и выходной ток стабилизатора имеет значение, которое было непосредственно перед моментом времени t1, и с этого момента соответственно изменяющееся с течением времени под действием дестабилизирующих факторов.

В момент времени t1, управляющий импульс U44 поступает также на соответствующий вход дополнительной переключающей ячейки 27. Под действием импульса U44 ячейка 27 переводится в состояние, при котором вход цифрового переключателя 11 отключается от источника 10 эталонного тока, а к последнему подключается резистор 28.

Снятие тока цифрового переключателя 11 приводит к выключению тиристора 47 и восстановлению его вентильной прочности (выключаются также и все открытые до момента t1 тиристоры остальных ячеек цифрового переключателя 11 и восстанавливается их вентильная прочность).

В момент времени t2 управляющие импульсы поступают на соответствующие входы дополнительной переключающей ячейки 27 (U45), рассматриваемой ячейки 12 (U20) и обязательно на соответствующие входы всех других ячеек цифрового переключателя 11 (на фиг. 5 не показаны). Длительность задержки t2-t1 выбирается несколько больше времени восстановления вентильной прочности тиристоров, ис пользуемых в ячейках 12, 13, 14 и 27, а длительность импульсов U45, U20 - несколько больше времени включения этих тиристоров.

Импульс U45 переводит дополнительную переключающую ячейку в состояние, при котором вход цифрового переключателя подключается к источнику 10 эталонного тока. Импульс U20 обеспечивает включение тиристора 48, т. е. обеспечивает включение секции 6 компенсационной обмотки в цепь тока Iэт, что и требуется в соответствии с новым кодом уставки.

В момент времени t3 оканчивается импульс Uвых25 и на управляющий вход силового регулятора 1 поступает сигнал рассогласования с выхода усилителя 3 постоянного тока. Контур авторегулирования отрабатывает значение тока, соответствующее новому коду уставки. Длительность импульса Uвых25 должна быть несколько больше суммарного времени, необходимо для осуществления всех операций по отработке нового кода уставки в блоках 21, 27 и 29 с момента t1.

До сих пор при анализе работы предложенного устройства считалось, что ток Iэт протекает непрерывно, т. е. никакие внешние причины не вызывают его прекращения или резкого уменьшения по сравнению с номинальным значением. При прекращении или резком изменении величины эталонного тока на выходе порогового элемента 24 появляется сигнал, который поступает на соответствующий вход блока 29 связи. Блок 29 реагирует выдачей управляющих импульсов Uвх25, U44, U45, U20 (точно так же, как при отработке нового кода уставки). Таким образом обеспечивается ввод тока Iэт при включении стабилизатора, при подаче силового питания после его отключения, при каких-либо сбоях, приведших к прекращению протекания тока Iэт. Если же нормальный режим работы блока 10 не восстанавливается, то в блоке 24 вырабатывается сигнал, информирующий о нарушении режима работы блока 10.

Переключающая ячейка 12 (см. фиг. 2) работает следующим образом.

При подаче управляющего сигнала на управляющий вывод 19 (относительно общего вывода 21) оптоэлектронный ключ 51 включается и управляющий электрод тиристора 47 подключается к положительному полюсу выпрямителя 53 (через отпирающийся во время действия управляющего сигнала транзистор 56 и ограничительный резистор58, фиг. 3). Тиристор 47 отпирается и эталонный ток Iэт протекает через него, не поступая в выходную цепь ячейки 12.

При подаче управляющего сигнала на управляющий вывод 20 включается оптоэлектронный ключ 52, при этом к положительному полюсу выпрямителя 53 подключается управляющий электрод тиристора 48. Тиристор 48 отпирается и эталонный ток Iэт пpотекает через подключенную к выходным выводам 17, 18 секцию 6 компенсационной обмотки.

Длительность управляющих сигналов, подаваемых на выводы 19, 20, должна превышать (с требуемым запасом) время включения тиристоров 47 и 48. Выключение тиристора 47 (или 48) осуществляется по его силовой цепи с помощью дополнительной переключающей ячейки.

Из описания работы стабилизатора следует, что выключение тиристоров цифрового коммутатора осуществляется по силовой цепи с помощью дополнительной переключающей ячейки, содержащей контур принудительной коммутации. Дополнительная переключающая ячейка обеспечивает отвод тока Iэт от цифрового коммутатора к балластному резистору. Прототип содержит N контуров принудительной коммутации тиристоров, в предложенном техническом решении имеется только один такой контур. Таким образом, при всех прочих равных условиях предложенное устройство имеет более высокую надежность. (56) 1. Э. К. Батманова и др. Стабилизатор постоянного тока для систем питания обмоток коррекции циклотронов. Сообщение ОИФИ 13-87-781, Дубна, 1987.

2. Авторское свидетельство СССР N 1688693, кл. G 05 F 1/56, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАБИЛИЗАТОР ПОСТОЯННОГО РЕГУЛИРУЕМОГО ТОКА | 1991 |

|

RU2010305C1 |

| ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО ТОКА | 1991 |

|

RU2019841C1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО ТОКА | 1992 |

|

RU2037185C1 |

| Стабилизатор постоянного регулируемого тока | 1983 |

|

SU1112353A1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО ТОКА | 1992 |

|

RU2054194C1 |

| Стабилизатор постоянного регулируемого тока | 1990 |

|

SU1728853A1 |

| Стабилизатор постоянного тока | 1990 |

|

SU1711136A1 |

| Стабилизатор постоянного тока | 1989 |

|

SU1645947A1 |

| УСТРОЙСТВО ДЛЯ ПРОЖИГА ПОВРЕЖДЕНИЙ ИЗОЛЯЦИИ КАБЕЛЬНЫХ ЛИНИЙ | 1992 |

|

RU2010254C1 |

| Система стабилизации постоянных регулируемых токов для питания N независимых нагрузок | 1987 |

|

SU1524032A1 |

Использование: в электротехнике. Устройство содержит силовой регулятор, соединенный через датчик тока с зажимами для подключения нагрузки. Управляющий вход силового регулятора через аналоговый запоминающий блок подключен к выходу усилителя постоянного тока, вход которого подключен к выходу датчика тока, который выполнен в виде измерительного узла с уравновешиванием ампервитков постоянных токов, включающего в себя измерительную обмотку, подключенную к входным выводам датчика тока, компенсационную обмотку, состоящую из N отдельных секций с разным числом витков, детектор разбаланса ампервитков, выход которого использован в качестве выхода датчика тока, источник эталонного тока и цифровой переключатель, состоящий из переключающих ячеек. Устройство содержит также блок связи с ЭВМ, пороговый элемент тока, одновибратор, дополнительную переключающую ячейку, резистор и силовой трансформатор с первичной и (N + 1) вторичными изолированными обмотками. Такое выполнение схемы устройства позволяет повысить его надежность по сравнению с прототипом. 5 ил.

СТАБИЛИЗАТОР ПОСТОЯННОГО РЕГУЛИРУЕМОГО ТОКА , содеpжащий силовой pегулятоp, соединенный чеpез датчик тока с выводами для подключения нагpузки, поpоговый элемент тока, одновибpатоp, вход запуска котоpого подключен к соответствующему выходу блока связи с электpонно-вычислительной машиной, к соответствующему входу котоpого подключен выход поpогового элемента тока, усилитель постоянного тока, вход котоpого подключен к выходу датчика тока, котоpый выполнен в виде измеpительного узла с уpавновешиванием ампеpвитков постоянных токов, включающего в себя измеpительную обмотку, подключенную к входным выводам датчика тока компенсационную обмотку, состоящую из N отдельных секций с pазным числом витков, детектоp pазбаланса ампеpвитков, выход котоpого является выходом датчика тока, источник эталонного тока, силовой тpансфоpматоp с пеpвичной и N втоpичными обмотками, а также цифpовой пеpеключатель, состоящий из N пеpеключающих ячеек, к выходным выводам котоpых подключены соответственно выводы секций компенсационной обмотки, к выводам пеpеменного тока пеpеключающих ячеек подключены соответственно втоpичные обмотки силового тpансфоpматоpа, пеpеключающие ячейки входными выводами соединены последовательно одна с дpугой, необъединенные входные выводы пеpвой и N-й ячеек использованы в качестве входных выводов цифpового пеpеключателя, упpавляющие входы пеpеключающих ячеек подключены к соответствующим выходам блока связи с электpонно-вычислительной машиной, пpи этом каждая из пеpеключающих ячеек содеpжит пеpвый и втоpой тиpистоpы, упpавляющие электpоды тиpистоpов чеpез шунтиpующие pезистоpы соединены с их катодами, пеpвый и втоpой оптоэлектpонные ключи, упpавляющие входы котоpых использованы в качестве упpавляющих входов пеpеключающей ячейки цифpового пеpеключателя, отличающийся тем, что, с целью повышения надежности, в него введены аналоговый запоминающий блок, вход котоpого подключен к выходу усилителя постоянного тока, выход - к упpавляющему входу силового pегулятоpа, а упpавляющий вход - к выходу одновибpатоpа, дополнительная пеpеключающая ячейка, выводы пеpеменного тока котоpой подключены к дополнительной втоpичной обмотке, введенной в силовой тpансфоpматоp, пеpвый вывод источника эталонного тока соединен непосpедственно с пеpвым входным выводом цифpового пеpеключателя, а чеpез pезистоp - с пеpвым выводом дополнительной пеpеключающей ячейки, втоpой вывод котоpой соединен с втоpым входным выводом цифpового пеpеключателя, втоpой вывод источника эталонного тока чеpез поpоговый элемент тока соединен с тpетьим выводом дополнительной пеpеключающей ячейки, упpавляющие входы котоpой подключены к соответствующим выходам блока связи с электpонно-вычислительной машиной, в каждую пеpеключающую ячейку цифpового пеpеключателя введен выпpямитель, выводы пеpеменного тока котоpого использованы в качестве выводов пеpеменного тока пеpеключающей ячейки, анод пеpвого тиpистоpа соединен соответственно с пеpвым входным и пеpвым выходным выводами пеpеключающей ячейки, втоpой выходной вывод котоpой соединен с анодом втоpого тиpистоpа, к объединенным катодам пеpвого и втоpого тиpистоpов подключены втоpой входной вывод пеpеключающей ячейки, общие выводы пеpвого и втоpого оптоэлектpонных ключей, а также соответствующий вывод постоянного тока выпpямителя, втоpой вывод постоянного тока котоpого подключен к входным выводам пеpвого и втоpого оптоэлектpонных ключей, выходные выводы котоpых подключены соответственно к упpавляющим электpодам пеpвого и втоpого тиpистоpов.

Авторы

Даты

1994-03-30—Публикация

1991-05-05—Подача